# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

11) Número de publicación: 2 784 236

61 Int. Cl.:

G11C 16/08 (2006.01) G11C 8/04 (2006.01) G11C 8/12 (2006.01)

(12)

## TRADUCCIÓN DE PATENTE EUROPEA

T3

(86) Fecha de presentación y número de la solicitud internacional: 31.01.2014 PCT/US2014/014014

(87) Fecha y número de publicación internacional: 06.08.2015 WO15116129

(96) Fecha de presentación y número de la solicitud europea: 31.01.2014 E 14881146 (6)

(97) Fecha y número de publicación de la concesión europea: 25.03.2020 EP 3100273

(54) Título: Direccionamiento tridimensional para memoria

45) Fecha de publicación y mención en BOPI de la traducción de la patente: 23.09.2020

(73) Titular/es:

HEWLETT-PACKARD DEVELOPMENT COMPANY, L.P. (100.0%) 10300 Energy Drive Spring TX 77389, US

(72) Inventor/es:

NG, BOON BING y GOY, HANG RU

(74) Agente/Representante:

SÁNCHEZ SILVA, Jesús Eladio

#### **DESCRIPCIÓN**

Direccionamiento tridimensional para memoria

#### 5 Antecedentes

La memoria es un elemento importante para almacenar información en un sistema. La memoria puede conseguirse mediante la creación y mantenimiento de una cantidad de estados diferentes, tal como "0" y "1". La memoria de solo lectura programable y borrable (EPROM) es un tipo de memoria no volátil que comprende una matriz de transistores de puerta flotante programados individualmente que almacenan unidades de memoria (por ejemplo, bits) codificadas por la conductividad de los transistores de almacenamiento.

Los cabezales de impresión integrados (IPH) pueden incluir memoria. La memoria IPH puede usarse para almacenar información como ID de bolígrafo, ID único, número de serie analógico (ASN), información de seguridad y otra información de mejora de características de IPH.

El documento US 2010/328405 A1 describe un cartucho de fluido integrado para asegurar la memoria integrada y un método para comunicaciones seguras entre un dispositivo dispensador de precisión y un cartucho de fluido integrado.

#### 20 Resumen

10

15

35

40

45

50

55

60

La invención se define por un dispositivo de memoria del cabezal de impresión de acuerdo con la reivindicación 1, un sistema de acuerdo con la reivindicación 7 y un método de acuerdo con la reivindicación 8.

#### 25 Breve descripción de los dibujos

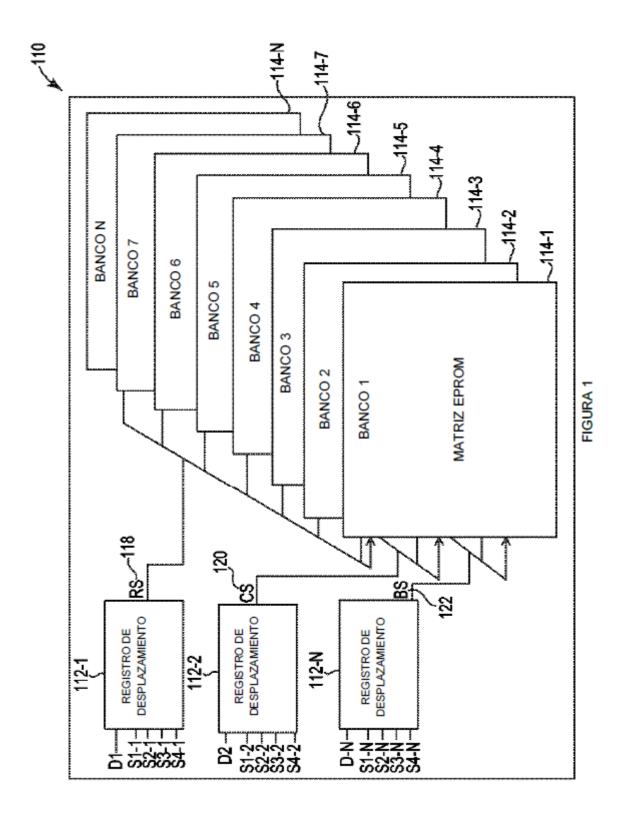

La Figura 1 es un diagrama de un ejemplo de un dispositivo de memoria del cabezal de impresión de acuerdo con la presente descripción.

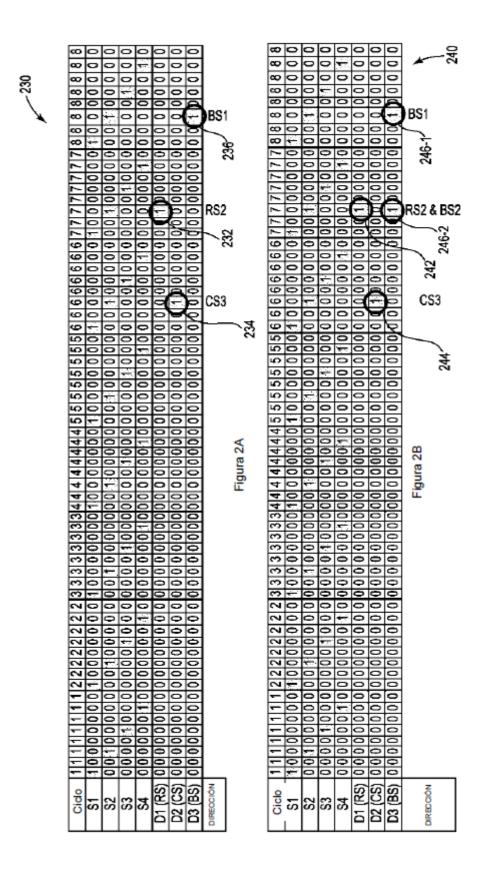

30 La Figura 2A es una tabla que ilustra un ejemplo del esquema de direccionamiento tridimensional para EPROM de acuerdo con la presente descripción.

La Figura 2B es una tabla que ilustra un ejemplo del esquema de direccionamiento paralelo tridimensional para EPROM de acuerdo con la presente descripción.

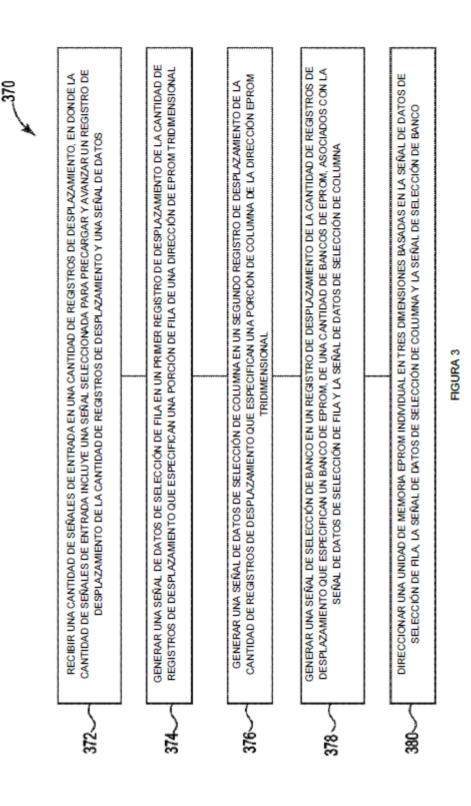

La Figura 3 es un diagrama de flujo de un ejemplo de un método para el direccionamiento tridimensional de una unidad de memoria EPROM de un cabezal de impresión integrado.

#### Descripción detallada

Los cabezales de impresión integrados (IPH) pueden utilizar una variedad de tecnologías de memoria diferentes. Por ejemplo, los IPH pueden usar tecnología de memoria con fusibles metálicos para almacenar información. Sin embargo, la memoria de solo lectura programable y borrable (EPROM) proporciona beneficios sobre la tecnología de fusibles metálicos, ya que existe un requisito de tamaño relativamente menor para un transistor selector de EPROM, no hay necesidad de dañar potencialmente una fuerza mecánica en la programación de la EPROM, y es imposible reconocer la condición del estado bajo inspección visual de la EPROM.

La capacidad de una plataforma IPH para implementar funciones puede estar limitada por la cantidad de memoria que tiene (por ejemplo, la cantidad de unidades de memoria direccionables que almacena la memoria). Es decir, cuanta más información se pueda almacenar en un IPH, más características pueden implementarse en el IPH. La cantidad de unidades de memoria direccionables (por ejemplo, bits) para un IPH puede estar limitada por muchos factores.

El direccionamiento EPROM en un IPH convencional se realiza mediante direccionamiento directo. El direccionamiento directo utiliza una señal de datos independiente para cada banco de EPROM. Como resultado, el direccionamiento directo requiere un registro (por ejemplo, registro de desplazamiento) por banco de EPROM para direccionar las unidades de memoria EPROM del banco de EPROM correspondiente.

La cantidad de estados reales de silicio (Si) disponibles para un registro dado y la EPROM asociada puede estar limitada por muchos factores. Por ejemplo, las restricciones de tamaño impuestas por el tamaño y/o la función del IPH pueden servir para limitar el estado real de Si disponible. Además, las restricciones de costos asociadas con la fabricación de un IPH determinado pueden limitar la cantidad de estados reales de Si disponibles para su registro y el banco EPROM correspondiente. Las limitaciones de estados reales de Si de un IPH se traducen en el registro del IPH y las limitaciones del banco EPROM, lo que se traduce en restricciones de unidades de memoria direccionables.

65 Los ejemplos de la presente descripción incluyen un dispositivo de memoria del cabezal de impresión que utiliza un esquema de direccionamiento tridimensional para EPROM junto con un sistema y un método para el direccionamiento

tridimensional para una unidad de memoria EPROM. El dispositivo de memoria del cabezal de impresión, los sistemas y los métodos pueden utilizar una serie de registros de desplazamiento, cada uno conectado a una cantidad de bancos de EPROM para generar una dirección EPROM tridimensional. La dirección EPROM tridimensional puede incluir una señal de datos de selección de fila, una señal de datos de selección de columna y una señal de datos de selección de banco. La señal de datos de selección de fila puede especificar una porción de fila de una dirección de unidad de memoria EPROM individual, la señal de selección de columna puede especificar una porción de columna de la dirección de EPROM individual, y la señal de selección de banco puede especificar un banco de EPROM de una cantidad de bancos de EPROM asociados con la dirección de la unidad de memoria EPROM individual especificada por el primer y segundo registro de desplazamiento. Como resultado, los ejemplos de la presente descripción que utilizan una dirección EPROM tridimensional pueden direccionar unidades de memoria EPROM en una mayor cantidad de bancos de EPROM mientras utilizan menos estados reales de Si (por ejemplo, menos registros de desplazamiento ya que cada banco EPROM no requiere un registro de desplazamiento correspondiente para direccionarlo) que los métodos convencionales.

10

15

20

25

30

65

La Figura 1 ilustra un ejemplo de un dispositivo de memoria del cabezal de impresión 110 de acuerdo con la presente descripción. El dispositivo de memoria del cabezal de impresión 110 puede integrarse en cualquier diseño de IPH. Por ejemplo, el dispositivo de memoria del cabezal de impresión 110 puede ser una porción de un IPH de inyección de tinta que tiene el cabezal de impresión integrado en el cartucho de tinta. El IPH asociado con el dispositivo de memoria del cabezal de impresión 110 puede incluir, por ejemplo, una carcasa, una cámara de tinta, una cantidad de entradas y salidas en comunicación fluida con la cámara de tinta, una cantidad de resistencias de disparo, varios contactos eléctricos y un controlador. El controlador puede incluir el dispositivo de memoria del cabezal de impresión 110.

El dispositivo de memoria del cabezal de impresión 110 puede incluir una cantidad de registros de desplazamiento 112-1, 112-N. Mientras que tres registros de desplazamiento 112-1, 112-N se ilustran en la Figura 1, la invención no está tan limitada. Por ejemplo, la cantidad de registros de desplazamiento 112-1, 112-N puede ser cualquier cantidad de registros de desplazamiento dentro de las restricciones de estados reales de Si disponibles.

En algunos ejemplos, cada uno de los registros de desplazamiento 112-1, 112-N puede incluir una cascada de circuitos biestables con dos estados estables que comparten un reloj de tiempo común. Cada circuito biestable puede conectarse a la entrada de datos del siguiente biestable en la cascada, lo que da como resultado un circuito que desplaza una matriz de bits almacenado al desplazar los datos recibidos en su entrada y al último bit de la matriz en cada transición de una entrada de reloj. Cada circuito biestable de un registro de desplazamiento puede denominarse etapa. La cantidad de registros de desplazamiento 112-1, 112-N puede incluir cualquier cantidad de etapas. Por ejemplo, los registros de desplazamiento pueden incluir ocho etapas como se muestra en la Figura 1.

Los registros de desplazamiento 112-1, 112-N pueden ser cualquier tipo de registro de desplazamiento. Por ejemplo, cada uno de los registros de desplazamiento 112-1, 112-N puede ser un registro de desplazamiento de entrada en serie, salida en paralelo.

Los registros de desplazamiento 112-1, 112-N pueden aceptar varias señales de entrada (por ejemplo, señales de selección S1-1, S4-N, señales de datos D1, D-N, etc.) a través de cualquier cantidad de líneas de entrada. Las señales de selección S1-1, S4-N pueden usarse para precargar y avanzar el registro de desplazamiento 112-1, 112-N que recibe las señales de selección S1-1, S4-N. Por ejemplo, el registro de desplazamiento 112-1 puede avanzar al pulsar repetidamente las señales de selección S1-1, S4-1 donde cada ciclo a través de las cuatro señales de selección S1-1, S4-1 hace que el registro de desplazamiento 112-1 avance una etapa. Las señales seleccionadas S1-1, S4-N pueden ser señales independientes o una señal común. Por ejemplo, las señales de selección S1-1, S1-2, S1-N pueden ser una señal común en lugar de señales distintas. Lo mismo puede decirse de las señales de selección S2-1, S2-2, S2-N, las señales de selección S3-1, S3-2, S3-N y las señales de selección S4-1, S4-2, S4-N.

Las señales de datos D1, D-N pueden servir como señales de inicio y pueden comunicar la dirección de fila y columna de una unidad de memoria EPROM. La entrada de datos por las señales D1, D-N puede asignarse arbitrariamente a cualquiera de los registros de desplazamiento 112-1, 112-N de manera que un registro de desplazamiento particular 112-1, 112-N no se limite a recibir un tipo particular de entrada de datos.

Cada uno de los registros de desplazamiento 112-1, 112-N puede conectarse a una cantidad de bancos de memoria 114-1, 114-N. Cualquier cantidad de bancos de memoria 114-1, 114-N es posible. Sin embargo, la cantidad de bancos de memoria 114-1, 114-N del dispositivo de memoria del cabezal de impresión 110 puede estar limitada por la cantidad de registros de desplazamiento 112-1, 112-N y la cantidad de etapas y ciclos de cada uno de los registros de desplazamiento 112-1, 112-N ya que el direccionamiento de una cantidad de bancos de memoria 114-1, 114-N incluye tener suficientes registros de desplazamiento/etapas de registro de desplazamiento/ciclos de registro de desplazamiento para distinguir entre las unidades de memoria de la cantidad de bancos de memoria 114-1, 114-N.

Cada banco de memoria 114-1, 114-N puede ser una matriz de unidades de memoria EPROM direccionables (por ejemplo, bits, etc.). El banco de memoria 114-1, 114-N puede tener cualquier tamaño de matriz EPROM con cualquier cantidad de direcciones de unidades de memoria EPROM individuales. Por ejemplo, un banco de memoria 114-1, 114-N lógicamente puede ser una matriz EPROM de ocho filas por ocho columnas que forman sesenta y cuatro unidades de memoria EPROM direccionables individuales. La disposición lógica y la cantidad de bits direccionables pueden estar

limitados por la cantidad de etapas y ciclos de cada uno de los registros de desplazamiento 112-1, 112-N, ya que direccionar una cantidad de unidades de memoria EPROM direccionables individuales incluye tener suficiente registro de desplazamiento etapas/ciclos de registro de desplazamiento para distinguir entre ellos.

- 5 Cada registro de desplazamiento 112-1, 112-N puede generar varias salidas (por ejemplo, señal de selección de fila (RS) 118, señal de selección de columna (CS) 120, señal de selección de banco (BS) 122). Aunque la Figura 1 ilustra las señales RS 118, CS 120 y BS 122 que se generan a partir de registros de desplazamiento separados 112-1, 112-N, la descripción no es tan limitada. Puede generarse más de una señal a partir de un registro de desplazamiento individual de la cantidad de registros de desplazamiento 112-1, 112-N. Por ejemplo, si cada uno de los bancos de memoria 114-1, 114-N incluye lógicamente una matriz EPROM que comprende ocho filas por ocho columnas que forman sesenta y cuatro 10 unidades de memoria EPROM direccionables individuales y cada registro de desplazamiento 112-1, ..., 112-N era un registro de desplazamiento de dieciséis etapas 112-1, 112-N, entonces un registro de desplazamiento particular (por ejemplo, el registro de desplazamiento 112-1) podría generar las señales RS 118 y CS 120 suficientes para direccionar la fila y la columna de una unidad de memoria EPROM direccionable de cualquiera de las matrices cuando se combina con una señal BS 122. La relación entre la cantidad de etapas del registro de desplazamiento 112-1, 112-N y la cantidad 15 de unidades de memoria EPROM direccionables individualmente puede determinar cuántas señales puede generar el registro de desplazamiento en particular (por ejemplo, el registro de desplazamiento 112-1). Siempre que el registro de desplazamiento particular (por ejemplo, el registro de desplazamiento 112-1) incluya suficientes etapas para direccionar tanto la columna como la porción de fila de una dirección de unidad de memoria EPROM de cualquiera de las matrices 20 EPROM de la cantidad de bancos de memoria 114-1, 114-N una vez emparejado con la señal BS 122, entonces ese registro de desplazamiento particular (por ejemplo, el registro de desplazamiento 112-1) puede generar las señales RS 118 y CS 120.

- Puede usarse una señal de datos D1 para generar la señal RS 118. La señal RS 118 puede identificar la porción de fila lógica de una dirección de una unidad de memoria EPROM direccionable individualmente dentro de cualquiera de las matrices EPROM de los bancos de memoria 114-1, 114-N. La señal RS 118 puede generarse al aplicar una señal de datos D1 durante un ciclo particular de una señal de selección particular S1-1, S4-N.

- Puede usarse una señal de datos D2 para generar la señal CS 120. La señal CS 120 puede identificar la porción de columna lógica de una dirección de una unidad de memoria EPROM direccionable individualmente dentro de cualquiera de las matrices EPROM de los bancos de memoria 114-1, 114-N. La señal CS 120 puede generarse al aplicar una señal de datos D2 durante un ciclo particular de una señal de selección particular S1-1, S4-N en un registro de desplazamiento particular 112-2.

- Puede usarse una señal de datos D-N para generar la señal BS 122. La señal BS 122 de puede identificar un banco de memoria particular de la cantidad de bancos de memoria 114-1, 114-N dentro del cual reside lógica o físicamente la unidad de memoria EPROM direccionable individualmente. Cuando la señal BS 122 se empareja con la señal RS 118 y la señal CS 120, se especifica una dirección de unidad de memoria EPROM tridimensional. Es decir, la señal RS 118 y la señal CS 120 representan una dirección EPROM bidimensional que especifica la fila lógica (por ejemplo, la señal RS 118) y la columna lógica (por ejemplo, CS 120) que son aplicables para direccionar una unidad de memoria EPROM en cualquiera de los bancos de memoria EPROM 114-1, 114-N. La señal BS 122 introduce una tercera dimensión en la dirección EPROM que especifica a qué banco de memoria 114-1, 114-N se dirige la señal RS 118 y la señal CS 120. En varias modalidades, la señal 122 de BS puede especificar un único banco de memoria de una cantidad de bancos de memoria 114-1, 114-N.

45

50

- Alternativamente, la señal 122 de BS puede especificar más de una de la cantidad de bancos de memoria 114-1, 114-N permitiendo el direccionamiento EPROM tridimensional paralelo. Por ejemplo, el D-N puede aplicarse durante varios ciclos de una señal de selección S1, S4 para direccionar la fila y columna especificada de más de uno de los bancos de memoria 114-1, 114-N en paralelo.

- La señal RS 118, la señal CS 120 y la señal BS 122 pueden introducirse por un transistor correspondiente. Por ejemplo, la señal RS 118 puede introducirse por un transistor RS, la señal CS 120 por un transistor CS y la señal BS 122 por un transistor BS. Los transistores RS, CS y BS pueden ser transistores NMOS. Los transistores RS, CS y BS pueden disponerse de cualquier manera que permita la generación de la dirección EPROM tridimensional. Por ejemplo, el transistor BS puede conectarse con el transistor CS y el transistor RS en cascada/serie. En otro ejemplo, el transistor BS puede conectarse a la puerta del transistor CS y el transistor RS. En otro ejemplo más, el transistor BS puede conectarse con el transistor RS a través de un decodificador adicional.

- El ejemplo del dispositivo de memoria del cabezal de impresión 110 de la Figura 1 muestra un esquema de direccionamiento de memoria tridimensional que permite menos registros de desplazamiento 112-1, 112-N con menos ciclos de direccionamiento para direccionar muchas más unidades de memoria EPROM direccionables que los métodos convencionales. Por ejemplo, utilizando el método convencional de direccionamiento directo con cuatro registros de desplazamiento de dieciséis etapas, solo se podrían direccionar cuatro bancos de memoria correspondientes de matrices de memoria EPROM de unidad de memoria de ocho por ocho. Es decir, el método convencional de direccionamiento directo requiere cuatro registros de desplazamiento de dieciséis etapas para direccionar 256 unidades de memoria. En yuxtaposición con el método convencional, algunos ejemplos de la presente descripción permitirían tres registros de

desplazamiento de ocho etapas 112-1, 112-N para generar direcciones de unidades de memoria EPROM tridimensionales para ocho bancos de memoria 114-1, 114-N de unidades de matrices de memoria EPROM de unidad de memoria de ocho por ocho. Es decir, los ejemplos de la presente descripción permiten tres registros de desplazamiento de ocho etapas 112-1, 112-N para direccionar 512 unidades de memoria. La presente descripción puede permitir menos registros de desplazamiento y/o más pequeños. En el ejemplo anterior, hay tres registros de desplazamiento en lugar de cuatro y los tres registros de desplazamiento son de ocho etapas en lugar de dieciséis etapas, ahorrando espacio tanto en términos de cantidad como de tamaño de los registros de desplazamiento.

- La Figura 2A y la Figura 2B son diagramas de ejemplos del esquema de direccionamiento tridimensional para EPROM.

La Figura 2A ilustra una tabla 230 que muestra un ejemplo del esquema de direccionamiento tridimensional para EPROM de la presente descripción. La tabla 230 consta de una serie de filas y columnas correspondientes a señales y el momento de su aplicación, respectivamente. En la tabla 230, se ilustra una señal aplicada cuando aparece un "1" en lugar de un "0" en la matriz de la tabla 230.

- Las filas S1, S2, S3 y S4 de la tabla 230 representan señales seleccionadas S1, S2, S3 y S4 que pueden aplicarse a cada registro de desplazamiento para precargar y avanzar cada registro de desplazamiento. En la tabla 230, las señales de selección S1, S2, S3 y S4 no son necesariamente señales de selección de un registro de desplazamiento. Es decir, las señales de selección S1, S2, S3 y S4 pueden simbolizar cualquier señal de selección aplicada a cualquiera de los registros de desplazamiento que aceptan señales de datos. Para aclarar aún más, haciendo referencia a la Figura 1, S1 de la tabla 230 podría representar señales seleccionadas S1-1, S1-2, S1-3 y/o S1-N. Además, S2, S3 y S4 de la tabla 230 podrían representar S2-1, S2-2, S2-3 y/o S2-N; S3-1, S3-2, S3-3 y/o S3-N; y S4-1, S4-2, S4-3 y/o S4-N, respectivamente. En consecuencia, la tabla 230 puede ilustrar señales de selección similares S1, S2, S3 y S4 que se aplican para precargar y avanzar una serie de registros de desplazamiento distintos.

- Cada columna de la tabla 230 representa un ciclo de registro de desplazamiento (por ejemplo, ciclo 1, ciclo 2, ciclo 3, ciclo 4, ciclo 5, ciclo 6, ciclo 7, ciclo 8) en donde el ciclo 1 es el primer ciclo en desplazarse. Como el ciclo puede corresponder a la aplicación de las señales de selección S1-S4, cada ciclo de la tabla 230 corresponde a cuatro aplicaciones de las señales de selección S1, S2, S3 y S4. Por lo tanto, cada ciclo corresponde a ocho columnas de ciclo numeradas de manera similar sobre las cuales se aplican las señales seleccionadas de las filas S1, S2, S3 y S4.

30

35

55

60

65

- La tabla 230 ilustra además las señales de datos de las filas D1 (RS), D2 (CS) y D3 (BS). La señal de datos de la fila D1 (RS) puede corresponder a una señal de datos D1 que especifica una fila de una dirección tridimensional para EPROM, la señal de datos de la fila D2 (CS) puede corresponder a una señal de datos D2 que especifica una columna de una dirección tridimensional para EPROM, y la señal de datos de la fila D3 (BS) puede corresponder a una señal de datos D3 correspondiente a un banco de una dirección tridimensional para EPROM. Como se describió anteriormente, la señal de datos D1, la señal de datos D2 y la señal de datos D3 ilustradas en las filas D1 (RS), D2 (CS) y D3 (BS) pueden ser señales de datos aplicadas en distintos registros de desplazamiento.

- Leídos juntos, la tabla 230 ilustra el momento de la aplicación de las señales antes mencionadas para formular una dirección tridimensional para EPROM (por ejemplo, RS2, CS3, BS1 como salida en la fila de direcciones de la tabla 230). Por ejemplo, la tabla 230 ilustra que la señal de datos D1 puede aplicarse durante el séptimo ciclo de la señal de selección correspondiente a S2 de un registro de desplazamiento de ocho etapas. Aplicado en este momento, D1 genera una señal de selección de fila (RS) 232 que significa que selecciona la fila dos (RS2). Se ilustra además en la tabla 230 que, la señal de datos D2 puede aplicarse durante el sexto ciclo de la señal de selección S2 de un registro de desplazamiento para generar una señal de selección de columna (CS) 234 que significa que selecciona la columna tres (CS3). La tabla 230 también ilustra que la señal de datos D3 puede aplicarse durante el octavo ciclo de la señal de selección S2 de un registro de desplazamiento para generar una señal de selección de banco (BS) 236 que significa que selecciona el banco uno (BS1). Cuando se combinan, las señales RS, CS y BS especifican una dirección tridimensional para una unidad de memoria EPROM. En el ejemplo de la Figura 2A, la dirección tridimensional es RS2, CS3, BS1, que se dirige a la unidad de memoria de la segunda fila de la tercera columna de un primer banco de memoria EPROM.

- La Figura 2B ilustra una tabla 240 que muestra un ejemplo del esquema de direccionamiento paralelo tridimensional para EPROM de la presente descripción. La tabla 240 consta de una serie de filas y columnas correspondientes a señales y el momento de su aplicación, respectivamente. Al igual que con la tabla 230, se ilustra una señal aplicada cuando aparece un "1" en lugar de un "0" en la matriz de la tabla 240. Las filas y columnas de la tabla 240 ilustran los mismos principios básicos de la tabla 230, excepto que se implementan en un esquema de direccionamiento paralelo. El esquema de direccionamiento paralelo de la tabla 240 puede conseguirse mediante una aplicación adicional de la señal de datos D3. Al aplicar la señal de datos D3 una vez más, la señal RS 242 y la señal CS 244 son aplicables en paralelo a los dos bancos de EPROM especificados por las dos señales BS 246-1 y 246-2.

- Por ejemplo, la tabla 240 ilustra el momento de la aplicación de las señales antes mencionadas para formular direcciones tridimensionales paralelas para EPROM (por ejemplo, RS2, CS3, BS1 y RS2, CS3, BS2 como salida en la fila de direcciones de la tabla 240). Por ejemplo, la tabla 240 ilustra que la señal de datos D1 puede aplicarse durante el séptimo ciclo de la señal de selección correspondiente a S2 de un registro de desplazamiento de ocho etapas. Aplicada en este momento, D1 genera una señal de selección de fila (RS) 242 que significa que selecciona la fila dos (RS2). Se ilustra además en la tabla 240 que, la señal de datos D2 puede aplicarse durante el sexto ciclo de la señal de selección S2 de

un registro de desplazamiento para generar una señal de selección de columna (CS) 244 que significa que selecciona la columna tres (CS3). La tabla 240 también ilustra que la señal de datos D3 puede ser tanto durante el séptimo como el octavo ciclo de la señal de selección S2 del registro de desplazamiento 240 para generar dos señales BS 246-1 y 246-2 que significan que selecciona el banco uno (BS1) y selecciona el banco dos (BS2), respectivamente. Cuando se combinan, las señales RS, CS y BS especifican direcciones de unidad de memoria tridimensional paralelas para EPROM. En el ejemplo de la Figura 2B, las direcciones tridimensionales son RS2, CS3, BS1 y RS2, CS3, BS2. RS2, CS3, BS1 se dirige a la unidad de memoria de la segunda fila de la tercera columna de un primer banco de memoria EPROM. RS2, CS3, BS2 se dirige a la unidad de memoria de la segunda fila de la tercera columna de un segundo banco de memoria EPROM. El esquema de direccionamiento paralelo tridimensional para EPROM ilustrado en la tabla 240 es un esquema de lectura paralela entre bancos. Es decir, el esquema de direccionamiento paralelo tridimensional para EPROM separados. Otra alternativa (no se muestra) es un esquema de direccionamiento paralelo dentro del banco. En un esquema de direccionamiento paralelo dentro del banco. En un esquema de direccionamiento paralelo dentro del banco puede direccionar simultáneamente múltiples filas y/o columnas del mismo banco de memoria EPROM.

10

15

20

25

45

50

55

60

65

Los ejemplos de la presente descripción pueden incluir sistemas para direccionamiento tridimensional para EPROM en un dispositivo de impresión. Tal sistema puede incluir una cantidad de bancos EPROM. Los bancos de EPROM pueden ubicarse en un dispositivo de impresión. Por ejemplo, pueden ubicarse en un cabezal de impresión integrado. Cada uno de estos bancos de EPROM puede ser una matriz de memoria EPROM. La matriz de memoria EPROM puede ser una matriz de unidades de memoria EPROM organizadas en filas y columnas.

El sistema puede incluir una cantidad de registros de desplazamiento. La cantidad de registros de desplazamiento puede ser registros de desplazamiento de entrada en serie, salida en paralelo. Es decir, una cadena de datos puede ingresarse en serie en el registro de desplazamiento, pero salir en formato paralelo a múltiples salidas. Por ejemplo, los datos de entrada en serie recibidos a través de una sola entrada física (por ejemplo, cable) pueden enviarse a través de múltiples salidas físicas (por ejemplo, cables) para direccionar simultáneamente múltiples bancos de EPROM a los que están conectados los registros de desplazamiento.

Cada uno de los registros de desplazamiento del sistema puede sincronizarse con sus señales de selección 30 correspondientes. Es decir, las señales de selección que se introducen en el registro de desplazamiento para precargar el registro de desplazamiento y avanzar el registro de desplazamiento pueden comprender un pulso de reloj que determina cuándo ocurre cada desplazamiento del registro de desplazamiento. Por ejemplo, puede haber cuatro señales de selección repetidas (por ejemplo, S1, S2, S3 y S4) que funcionan como pulsos de reloj. Un conjunto de las cuatro señales de selección puede ser un ciclo de reloj para el registro de desplazamiento. En los ejemplos de la presente descripción, 35 el registro de desplazamiento puede utilizar ciclos de reloj al cambiar los datos para generar señales RS, CS y BS. La cantidad de ciclos de reloj asociados con el registro de desplazamiento puede determinar la cantidad de bancos de memoria EPROM y la cantidad de unidades de memoria EPROM de cada banco EPROM. Por ejemplo, la cantidad de bancos de memoria EPROM puede ser igual a la cantidad de ciclos de reloj asociados con un registro de desplazamiento 40 que genera la señal BS ya que cada ciclo de reloj puede corresponder a uno de los bancos de EPROM. Además, la cantidad de filas y la cantidad de columnas de unidades de memoria EPROM en cada matriz de memoria EPROM puede ser igual a la cantidad de ciclos de reloj asociados con un registro de desplazamiento que especifica una señal CS y/o RS ya que cada ciclo de reloj puede corresponder a una de las designaciones de fila y/o columna de la matriz de memoria EPROM.

El sistema puede incluir una señal de datos de selección de fila para especificar una porción de fila de la dirección tridimensional para EPROM. Por ejemplo, la señal de datos de selección de fila puede incluir una indicación de la fila de la unidad de memoria EPROM dentro de una matriz de memoria EPROM a la que se dirige la dirección tridimensional para EPROM. La señal de datos de selección de fila puede corresponder a un primer registro de desplazamiento de la cantidad de registros de desplazamiento. Por ejemplo, la señal de selección de fila puede ingresarse en el primer registro de desplazamiento como una señal de datos y puede especificar la porción de fila de la dirección tridimensional para EPROM en función de cuándo se aplica la señal de datos en relación con varias señales de selección.

El sistema también puede incluir una señal de datos de selección de columna para especificar una porción de columna de la dirección tridimensional para EPROM. Por ejemplo, la señal de datos de selección de columna puede incluir una indicación de la columna de la unidad de memoria EPROM dentro de una matriz de memoria EPROM a la que se dirige la dirección tridimensional para EPROM. La señal de datos de selección de columna puede corresponder a un segundo registro de desplazamiento de la cantidad de registros de desplazamiento. Por ejemplo, la señal de selección de columna puede ingresarse en el segundo registro de desplazamiento como una señal de datos y puede especificar la porción de fila de la dirección tridimensional para EPROM en función de cuándo se aplica la señal de datos en relación con varias señales de selección.

Puede incluirse en el sistema una señal de datos de selección de banco que especifique una parte de banco EPROM de la dirección tridimensional para EPROM. Por ejemplo, la señal de datos de selección de banco puede incluir una indicación del banco de EPROM de la cantidad de bancos de EPROM a los que se dirigen la columna de la señal de selección de columna y la fila de la señal de selección de fila. La señal de datos de selección de banco puede corresponder a un tercer

### ES 2 784 236 T3

registro de desplazamiento de la cantidad de registros de desplazamiento. Por ejemplo, la señal de selección de banco puede ingresarse en el tercer registro de desplazamiento como una señal de datos y puede especificar la porción de fila de la dirección tridimensional para EPROM en función de cuándo se aplica la señal de datos en relación con varias señales de selección.

5

La Figura 3 ilustra un diagrama de flujo de un ejemplo de un método 370 para el direccionamiento tridimensional de una unidad de memoria EPROM de un cabezal de impresión integrado. En 372, el método 370 puede incluir recibir una cantidad de señales de entrada en una cantidad de registros de desplazamiento, en donde la cantidad de señales de entrada incluye una señal de selección para precargar y avanzar un registro de desplazamiento de la cantidad de registros de desplazamiento y una señal de datos. Cada uno de los registros de desplazamiento puede conectarse a cada banco EPROM de una cantidad de bancos EPROM. Por ejemplo, cada registro de desplazamiento puede estar en comunicación con cada banco EPROM de la cantidad de bancos de EPROM de modo que pueda transmitir y/o recibir datos de cada uno de los bancos de memoria EPROM.

10

15

En 374, el método 370 puede incluir generar una señal de datos de selección de fila en un primer registro de desplazamiento de la cantidad de registros de desplazamiento que especifica una porción de fila de una dirección EPROM tridimensional.

20

En 376, el método 370 puede incluir generar una señal de datos de selección de columna en un segundo registro de desplazamiento de la cantidad de registros de desplazamiento que especifica una porción de columna de la dirección EPROM tridimensional.

0.1

En 378, el método 370 puede incluir generar una señal de selección de banco en un registro de desplazamiento de la cantidad de registros de desplazamiento que especifica un banco de EPROM, de una cantidad de bancos de EPROM, asociados con la señal de datos de selección de fila y la señal de datos de selección de columna.

25

En 380, el método 370 puede incluir el direccionamiento de una unidad de memoria EPROM individual en tres dimensiones en función de la señal de datos de selección de fila, la señal de datos de selección de columna y la señal de selección de banco. La dirección de la unidad de memoria EPROM tridimensional puede generarse dentro de los ocho ciclos de la cantidad de registros de desplazamiento. Por ejemplo, la cantidad de registros de desplazamiento puede generar una señal de selección de fila, una señal de selección de columna y una señal de selección de banco dentro de los ocho ciclos del registro de desplazamiento que recibe la señal de datos.

30

35

En la descripción detallada de la presente descripción, se hace referencia a los dibujos adjuntos que forman parte de la misma, y en los cuales se muestra a modo de ilustración cómo pueden practicarse ejemplos de la descripción. Estos ejemplos se describen con suficiente detalle para permitir que los expertos en la materia practiquen los ejemplos de esta descripción, y debe entenderse que pueden usarse otros ejemplos y pueden realizarse cambios en el proceso, eléctricos y/o estructurales sin apartarse del alcance de la presente descripción.

40

Además, la proporción y la escala relativa de los elementos proporcionados en las figuras pretenden ilustrar los ejemplos de la presente descripción, y no deben tomarse en un sentido limitante. Como se usa en la presente descripción, los designadores "N", particularmente con respecto a los números de referencia en los dibujos, indican que un número de la característica particular así designada puede incluirse con una serie de ejemplos de la presente descripción. Como se usa en la presente descripción, "una" o "una cantidad de" algo puede referirse a una o más de tales cosas.

#### REIVINDICACIONES

1. Dispositivo de memoria del cabezal de impresión (110), que comprende:

5

10

15

20

25

55

65

una serie de bancos de memoria de solo lectura programables (EPROM) borrables (114-1, 114-N), cada uno de los cuales comprende una matriz de memoria EPROM; y

una cantidad de registros de desplazamiento de entrada en serie, salida en paralelo (112-1, 112-N), cada uno conectado a cada banco EPROM de la cantidad de bancos de EPROM (114-1, 114-N), en donde los registros son capaces de generar una dirección EPROM tridimensional basada en señales de entrada, en donde generar la dirección EPROM tridimensional comprende generar varias salidas, las salidas que comprenden:

una señal de datos de selección de fila (118) que especifica una porción de fila de la dirección EPROM tridimensional,

una señal de datos de selección de columna (120) que especifica una porción de columna de la dirección EPROM tridimensional, y

una señal de datos de selección de banco (122) que especifica un banco de EPROM de la cantidad de bancos de EPROM (114-1, 114-N) asociados con la señal de datos de selección de fila (118) y la señal de datos de selección de columna (120), en donde

la señal de datos de selección de banco (122) especifica más de una de la cantidad de bancos de EPROM (114-1, 114-N) asociados con los datos de selección de fila y los datos de selección de columna, para generar una dirección EPROM tridimensional paralela para direccionar simultáneamente una fila y una columna en la cantidad específica de más de uno de los bancos de EPROM.

- 2. El dispositivo (110) de acuerdo con la reivindicación 1, que comprende un primer registro de desplazamiento de la cantidad de registros de desplazamiento (112-1, 112-N) que es capaz de generar la señal de datos de selección de fila (118) y la señal de datos de selección de columna (120), y un segundo registro de desplazamiento de la cantidad de registros de desplazamiento (112-1, 112-N) que es capaz de generar la señal de datos de selección de banco (122).

- 3. El dispositivo (110) de acuerdo con la reivindicación 1, que comprende un primer registro de desplazamiento de la cantidad de registros de desplazamiento (112-1, 112-N) que es capaz de generar la señal de datos de selección de fila (118), un segundo registro de desplazamiento de una cantidad de registros de desplazamiento (112-1, 112-N) que es capaz de generar la señal de datos de selección de columna (120), y un tercer registro de desplazamiento de la cantidad de registros de desplazamiento (112-1, 112-N) que es capaz de generar la señal de datos de selección de banco (122).

- 4. El dispositivo (110) de acuerdo con la reivindicación 3, en donde cada una de la cantidad de registros de desplazamiento (112-1, 112-N) es capaz de aceptar una cantidad de entradas que incluye una señal de datos correspondiente y una cantidad de señales de selección correspondientes (S1, S2, S3, S4).

- 5. El dispositivo (110) de acuerdo con la reivindicación 4, en donde las señales de selección correspondientes se precargan y avanzan un registro de desplazamiento correspondiente.

- 6. El dispositivo (110) de acuerdo con la reivindicación 5, en donde el registro de desplazamiento correspondiente está configurado para avanzar una etapa tras recorrer cuatro de las señales de selección correspondientes.

- 45 7. Un sistema que comprende: un dispositivo de impresión; y un dispositivo de memoria del cabezal de impresión de acuerdo con la reivindicación 1.

- 8. Un método para el direccionamiento tridimensional de una unidad de memoria de memoria de solo lectura programable y borrable (EPROM) de un cabezal de impresión integrado, que comprende: recibir una cantidad de señales de entrada en una cantidad de registros de desplazamiento de entrada en serie, salida en paralelo (112-1, 112-N), en donde cada registro de desplazamiento de la cantidad de registros de desplazamiento (112-1, ..., 112-N) está conectado a cada banco de EPROM de una cantidad de bancos de EPROM

(114-1, 114-N) y en donde la cantidad de señales de entrada incluye una señal de selección para precargar y avanzar un registro de desplazamiento de la cantidad de registros de desplazamiento (112-1, ...112-N) y una señal de datos;

generar una señal de datos de selección de fila de salida (118) en un primer registro de desplazamiento de la cantidad de registros de desplazamiento (112-1, 112-N) que especifica una porción de fila de una dirección EPROM tridimensional:

generar una señal de datos de selección de columna de salida (120) en un segundo registro de desplazamiento de la cantidad de registros de desplazamiento (112-1, 112-N) que especifica una porción de columna de la dirección EPROM tridimensional;

generar, en respuesta a una señal de datos de entrada que se aplica a más de una etapa del registro de desplazamiento que genera la señal de datos de selección de banco, una señal de datos de selección de banco de salida (122) en un registro de desplazamiento de la cantidad de registros de desplazamiento (112-1 ..., 112-N) que especifica más de una de la cantidad de bancos de EPROM (114-1, 114-N) asociados con los datos de

## ES 2 784 236 T3

selección de fila y los datos de selección de columna, para generar una dirección de EPROM tridimensional paralela para direccionar simultáneamente una fila y una columna en la cantidad específica de más de uno de los bancos de EPROM; y

direccionar una unidad de memoria EPROM individual en cada uno de los bancos especificados en tres dimensiones basadas en la señal de datos de selección de fila (118), la señal de datos de selección de columna (120) y la señal de selección de banco.

5

12