# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

11) Número de publicación: 2 787 907

51 Int. Cl.:

**H03M 13/11** (2006.01) **H03M 13/00** (2006.01)

(12)

### TRADUCCIÓN DE PATENTE EUROPEA

**T3**

(86) Fecha de presentación y número de la solicitud internacional: 10.08.2017 PCT/IB2017/054889

(87) Fecha y número de publicación internacional: 15.02.2018 WO18029633

Fecha de presentación y número de la solicitud europea: 10.08.2017 E 17767925 (5)

Fecha y número de publicación de la concesión europea: 11.03.2020 EP 3308469

(54) Título: Métodos de adaptación de velocidad para códigos LDPC

(30) Prioridad:

12.08.2016 US 201662374688 P

Fecha de publicación y mención en BOPI de la traducción de la patente: 19.10.2020

(73) Titular/es:

TELEFONAKTIEBOLAGET LM ERICSSON (PUBL) (100.0%)

164 83 Stockholm, SE

(72) Inventor/es:

ANDERSSON, MATTIAS; BLANKENSHIP, YUFEI y SANDBERG, SARA

(74) Agente/Representante:

**FÚSTER OLAGUIBEL, Gustavo Nicolás**

#### **DESCRIPCIÓN**

Métodos de adaptación de velocidad para códigos LDPC

#### 5 Campo técnico

La presente divulgación se refiere, en general, a las comunicaciones inalámbricas y, más particularmente, a los métodos de adaptación de velocidad para códigos de verificación de paridad de baja densidad (LDPC, por sus siglas en inglés).

#### **Antecedentes**

10

15

20

25

30

40

45

50

55

60

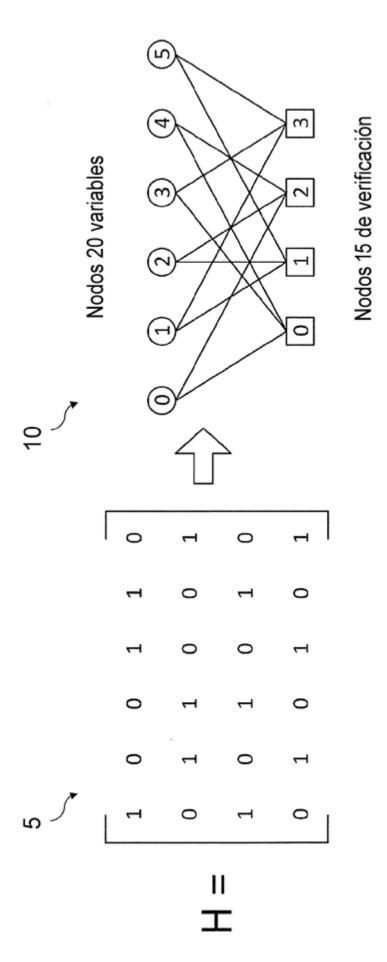

Los códigos LDPC se describen fácilmente a través de una matriz de verificación de paridad (PCM, por sus siglas en inglés), en las que las filas y columnas corresponden a nodos de verificación y nodos variables, respectivamente. Cada "1" en la PCM corresponde a una arista entre un nodo de verificación y un nodo variable.

La figura 1 ilustra un ejemplo de la PCM 5 y el grafo 10 bipartito correspondiente. La PCM 5 puede mapearse en el grafo 10 bipartito, que se compone de los nodos 15 de verificación y los nodos 20 variables, en el que las filas y columnas de la PCM 5 corresponden a los nodos 15 de verificación y los nodos 20 variables, respectivamente. Cada entrada h(i,j) = 1 en la PCM 5 corresponde a una arista entre un nodo 15 de verificación y un nodo 20 variable.

La velocidad de código (R) de la PCM 5 se define como el número de bits de información k dividido entre el número de bits codificados n, R = k/n, donde n es el número de columnas en la PCM 5 y k es igual al número de columnas menos el número de filas de la PCM 5.

Una clase importante de códigos LDPC son los códigos LDPC cuasicíclicos (QC, quasi-cyclic). La PCM H de un código QC-LDPC es de tamaño m x n, y puede representarse mediante una matriz base H\_base de tamaño m<sub>b</sub> = m/Z y n<sub>b</sub> = n/Z, y un factor de elevación Z. Cada entrada de H\_base contiene o bien el número -1 o bien uno o más números entre 0 y Z - 1. Por ejemplo, sean i y j números enteros entre 0 y (m/Z-1), y 0 y (n/Z-1), respectivamente. Luego, la submatriz formada a partir de las entradas en las filas Z\*i a Z\*(i + 1) - 1 y las columnas Z\*j a Z\*(j + 1) - 1 (suponiendo que la indexación de filas y columnas empiece en 0), están determinadas por la entrada en la fila i y la columna j de H\_base de la siguiente manera.

Si H\_base (i,j) = -1, entonces la submatriz en la matriz binaria expandida H es igual a la matriz nula Z por Z. El número -1 usado para indicar submatrices nulas puede seleccionarse arbitrariamente siempre que no sea un número entre 0 y Z-1.

Si H\_base (i,j) contiene uno o más números enteros  $k_1$ ,  $k_2$ , ...  $k_d$  entre 0 y Z - 1, la submatriz en la matriz binaria expandida H es igual a la suma de las matrices identidad desplazadas  $P_k_1 + P_k_2 + ... + P_k_d$ , donde cada submatriz Z x Z  $P_k$  se obtiene a partir de la matriz identidad Z por Z desplazando cíclicamente las columnas a la derecha k veces.

Los códigos LDPC pueden optimizarse para cualquier longitud de bloque y/o cualquier velocidad de código. Sin embargo, en los sistemas de comunicación prácticos, no es eficiente usar PCM diferentes para cada alternativa de velocidades y longitudes de bloque. En cambio, la adaptación de velocidad se implementa mediante a través de abreviación, perforación y/o repetición. Como ejemplo, los códigos LDPC para 802.11n se especifican con 12 códigos madre (3 longitudes de bloque diferentes y 4 velocidades diferentes). Las PCM para todas las demás longitudes de bloque y velocidades de código necesarias se especifican a través de mecanismos de adaptación de velocidades (que incluyen abreviación, perforación y/o repetición) aplicados a uno de los 12 códigos madre.

La abreviación es una técnica para obtener códigos de menor longitud y menor velocidad a partir de un código LDPC dedicado fijando el valor de algunos bits de información en algunos valores conocidos (por ejemplo, "0") al codificar. Se supone que las posiciones de los bits fijos están disponibles tanto para el codificador como para el decodificador. Para un código sistemático, los bits abreviados se perforan entonces de la palabra de código antes de la transmisión. En el proceso de decodificación, los bits fijos tienen una fiabilidad infinita. La abreviación reduce el tamaño de bloque de información de k a ktx.

La perforación, por otro lado, es una técnica en la que algunos bits codificados no se transmiten. Esto aumenta la velocidad de código del código madre LDPC dedicado y disminuye el tamaño de bloque de código.

Con la repetición, algunos de los bits codificados se repiten y transmiten más de una vez. A diferencia de la perforación, la repetición aumenta el tamaño de bloque de código.

Conjuntamente, la perforación, la abreviación y la repetición cambian el número de bits codificados de n a n<sub>tx</sub>. Después de aplicar la adaptación de velocidad, el tamaño de código nativo (k, n) definido por la PCM se modifica a un tamaño de código real (k<sub>tx</sub>, n<sub>tx</sub>). Por tanto, para un conjunto de k<sub>tx</sub> bits de información, se producen n<sub>tx</sub> bits codificados para la

transmisión. De manera correspondiente, la velocidad de código real se calcula basándose en Rtx = ktx/ntx.

Dado un código LDPC dedicado de tamaño de código (k, n), es necesario un método de adaptación de velocidad simple y efectivo para el tamaño de código real (Ktx, Ntx) necesario para una transmisión particular. Algunos códigos LDPC perforan algunos bits sistemáticos por diseño para mejorar el rendimiento del código, sin relación con la adaptación de velocidad. Sin embargo, no está claro cómo realizar la adaptación de velocidad tal como se define en 802.11n en este caso.

El documento US 2008/320353 divulga un método y un aparato para asignar versiones de redundancia a una memoria intermedia circular dentro de un sistema de comunicación. Durante la operación, se crea una memoria intermedia circular en la que sólo se definen versiones de redundancia para empezar en la parte superior (es decir, en la primera fila) de los intercaladores de subbloques constituyentes.

Jung-Fu Cheng et al.: "Analysis of Circular Buffer Rate Matching for LTE Turbo Code", 2003 IEEE 58° Congreso sobre Tecnología Vehicular, enero de 2008 páginas 1-5, analiza los algoritmos de adaptación de velocidad de memoria intermedia circular (CBRM, por sus siglas en inglés) para el código turbo en la evolución a largo plazo (LTE) de la interfaz aérea basada en WCDMA. Para mejorar el rendimiento a altas velocidades de código, se incorpora la perforación de bits sistemáticos junto con la CBRM. El algoritmo RM se optimiza adicionalmente basándose en las propiedades algebraicas de los intercaladores QPP y el código convolucional sistemático recursivo de 8 estados del código turbo LTE.

#### Sumario

5

Para abordar los problemas anteriores con los enfoques existentes, se divulga un método de adaptación de velocidad para producir un conjunto de bits codificados a partir de un conjunto de bits de información para la transmisión entre un primer nodo y un segundo nodo en un sistema de comunicaciones inalámbricas. El método comprende las etapas expuestas en la reivindicación 1. El método comprende generar un vector de palabra de código codificando el conjunto de bits de información con un código de verificación de paridad de baja densidad cuasicíclico, en el que el vector de palabra de código se compone de bits sistemáticos y bits de paridad. El método comprende realizar una adaptación de velocidad basada en memoria intermedia circular en el vector de palabra de código generado para producir los bits codificados para la transmisión. Realizar la adaptación de velocidad basada en memoria intermedia circular en el vector de palabra de código generado para producir los bits codificados para la transmisión comprende, entre otras cosas, perforar una primera pluralidad de bits sistemáticos dejando la primera pluralidad perforada de bits sistemáticos fuera de la memoria intermedia circular.

En determinadas realizaciones, la primera pluralidad de bits sistemáticos que se perforan puede preceder, en el vector de la palabra de código, a una segunda pluralidad de bits sistemáticos que no se perforan.

En determinadas realizaciones, puede definirse una pluralidad de versiones de redundancia por la memoria intermedia circular de tal manera que los bits codificados para una retransmisión se leen de la memoria intermedia circular según una versión de redundancia correspondiente definida para la retransmisión. El método puede comprender realizar una adaptación de velocidad basada en memoria intermedia circular en el vector de palabra de código generado para producir bits codificados para la retransmisión, en el que la adaptación de velocidad basada en memoria intermedia circular para la retransmisión comprende perforar la primera pluralidad de bits sistemáticos. La primera pluralidad de bits sistemáticos perforados para la retransmisión puede incluir un múltiplo par de Z bits sistemáticos, donde Z es un factor de elevación de la matriz de verificación de paridad.

En determinadas realizaciones, la primera pluralidad de bits sistemáticos perforados puede incluir un múltiplo par de Z bits sistemáticos, donde Z es un factor de elevación de la matriz de verificación de paridad.

En determinadas realizaciones, realizar una adaptación de velocidad basada en memoria intermedia circular en el vector de palabra de código generado puede comprender leer los bits sistemáticos y los bits de paridad fuera de una memoria intermedia circular para producir el vector de transmisión para la transmisión por un canal inalámbrico. La lectura de los bits sistemáticos y los bits de paridad fuera de la memoria intermedia circular para producir el vector de transmisión para la transmisión por el canal inalámbrico puede comprender, si el número de bits del vector de transmisión es mayor que el número total de bits en la memoria intermedia circular, repetir uno o más bits en la memoria intermedia circular iniciando un nuevo ciclo.

En determinadas realizaciones, los bits ficticios unidos pueden comprender una segunda pluralidad de bits sistemáticos que está separada de la primera pluralidad perforada de bits sistemáticos. En determinadas realizaciones, el método puede comprender perforar los bits ficticios unidos. En determinadas realizaciones, perforar los bits ficticios unidos puede comprender omitir la escritura de los bits ficticios unidos en la memoria intermedia circular. En determinadas realizaciones, perforar los bits ficticios unidos puede comprender omitir los bits ficticios unidos cuando se leen los bits codificados de la memoria intermedia circular.

En determinadas realizaciones, puede omitirse que un subconjunto de los bits de paridad se escriba en la memoria

3

50

35

55

60

intermedia circular.

5

10

15

35

40

45

50

55

60

65

En determinadas realizaciones, el método puede comprender perforar un subconjunto de los bits sistemáticos escritos en la memoria intermedia circular en una primera transmisión por el canal inalámbrico. El método puede comprender incluir el subconjunto de los bits sistemáticos que se perforaron en una retransmisión por el canal inalámbrico.

En determinadas realizaciones, el método puede comprender perforar bits a lo largo de columnas de tal manera que se perforen bits de manera uniforme de cada una de una pluralidad de filas y se mantenga una distribución de peso de la matriz de verificación de paridad en la memoria intermedia circular. Los bits sistemáticos y los bits de paridad pueden leerse de modo que se implemente un intercalador de canales como parte de realizar la adaptación de velocidad basada en memoria intermedia circular en el vector de palabra de código generado. En determinadas realizaciones, los bits perforados pueden tener un mayor peso de columna que los bits no perforados. En determinadas realizaciones, los bits sistemáticos y los bits de paridad pueden leerse de tal manera que no se implemente ningún efecto de intercalación de canales.

En determinadas realizaciones, el sistema de comunicaciones inalámbricas puede comprender un nuevo sistema de radio.

También se divulga un primer nodo para producir un conjunto de bits codificados a partir de un conjunto de bits de información para su transmisión a un segundo nodo en un sistema de comunicaciones inalámbricas. El primer nodo comprende conjuntos de circuitos de procesamiento tal como se expone en la reivindicación 13. Los conjuntos de circuitos de procesamiento están configurados para generar un vector de palabra de código codificando el conjunto de bits de información con un código de verificación de paridad de baja densidad cuasicíclico, en el que el vector de palabra de código se compone de bits sistemáticos y bits de paridad. Los conjuntos de circuitos de procesamiento están configurados para realizar una adaptación de velocidad circular basada en memoria intermedia en el vector de palabra de código generado para producir los bits codificados para la transmisión, en el que realizar la adaptación de velocidad circular basada en memoria intermedia en el vector de palabra de código generado para producir los bits codificados para la transmisión comprende entre otras cosas, perforar una primera pluralidad de bits sistemáticos dejando la primera pluralidad perforada de bits sistemáticos fuera de la memoria intermedia circular.

Determinadas realizaciones de la presente divulgación pueden proporcionar una o más ventajas técnicas. Por ejemplo, en determinadas realizaciones, los métodos de adaptación de velocidad basada en memoria intermedia circular pueden diseñarse de tal manera que puede proporcionarse una matriz arbitraria (Ktx, Ntx) mediante un único procedimiento. Como otro ejemplo, en determinadas realizaciones puede que no haya necesidad de definir un procedimiento independiente para cada uno de abreviación, perforación y repetición. Otras ventajas pueden resultar fácilmente evidentes para un experto en la técnica. Determinadas realizaciones pueden tener ninguna, algunas o todas las ventajas mencionadas.

#### Breve descripción de los dibujos

Para una comprensión más completa de las realizaciones divulgadas y sus características y ventajas, ahora se hace referencia a la siguiente descripción, junto con los dibujos adjuntos, en los que:

La figura 1 ilustra una PCM de ejemplo y el grafo bipartito correspondiente;

la figura 2 es un diagrama de bloques que ilustra una realización de una red, según determinadas realizaciones;

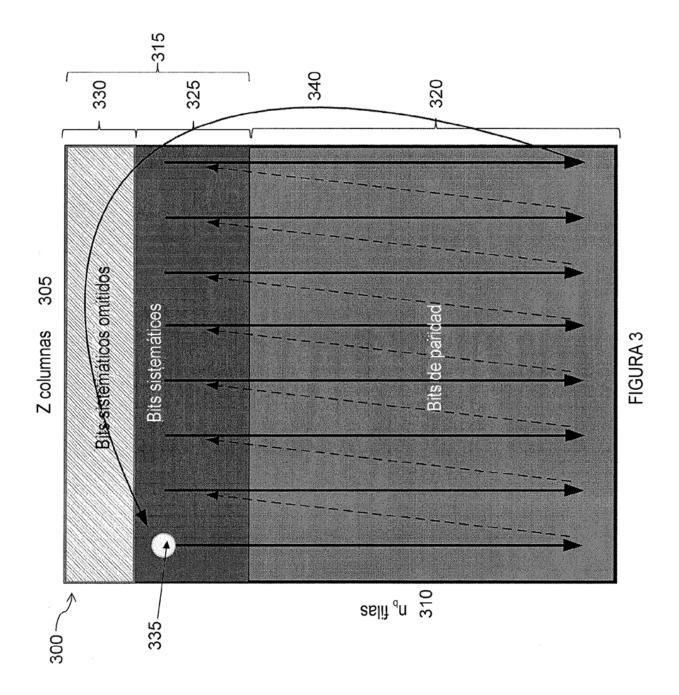

la figura 3 ilustra un ejemplo en el que los bits sistemáticos y los bits de paridad se leen a lo largo de columnas, según determinadas realizaciones;

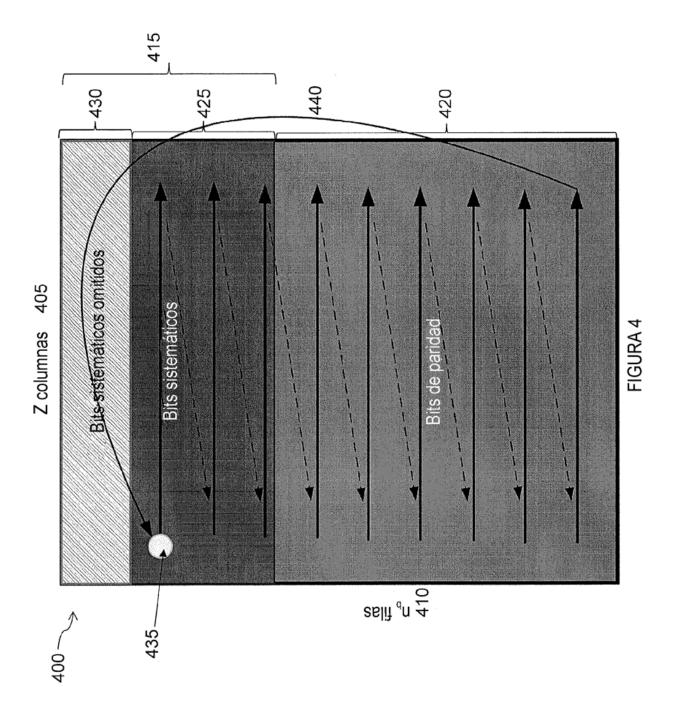

la figura 4 ilustra un ejemplo en el que los bits sistemáticos y los bits de paridad se leen a lo largo de filas, según determinadas realizaciones;

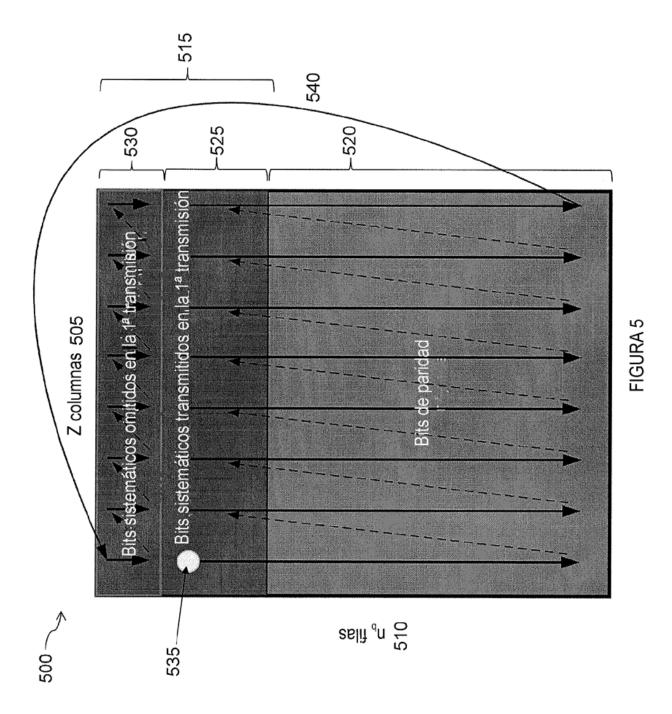

la figura 5 ilustra un ejemplo en el que, cuando se alcanza el final de la memoria intermedia circular, se inicia un nuevo ciclo para los bits sistemáticos que se omitieron en una primera transmisión, según determinadas realizaciones;

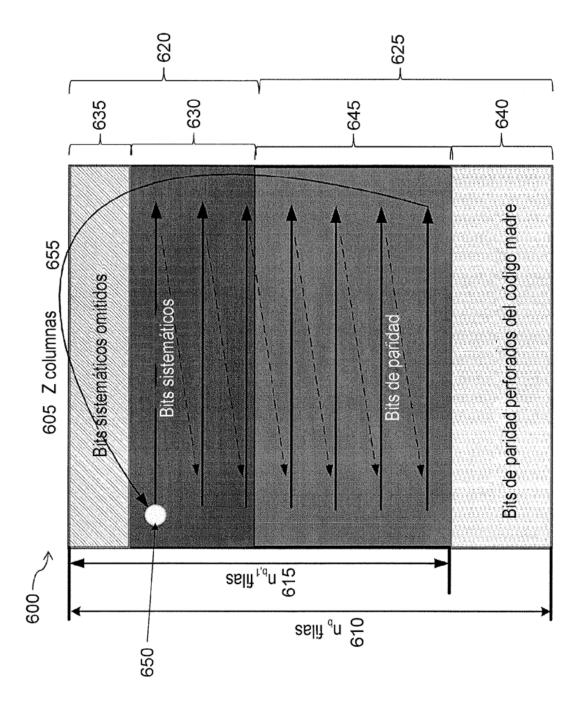

la figura 6 ilustra un ejemplo en el que la memoria intermedia circular utiliza un subconjunto de bits codificados según se define mediante la PCM, de modo que la velocidad de código usada para la transmisión real es mayor que una velocidad de código R de la PCM, según determinadas realizaciones;

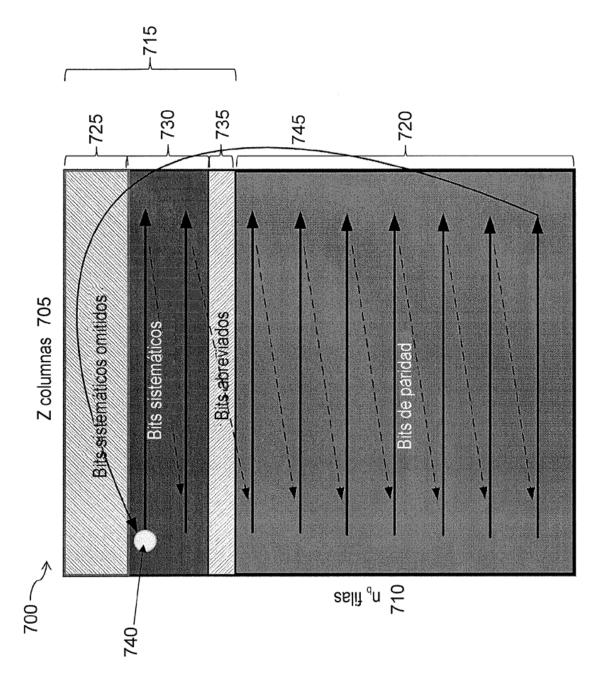

la figura 7 ilustra un ejemplo en el que también se implementa la abreviación como parte del procedimiento de adaptación de velocidad, según determinadas realizaciones;

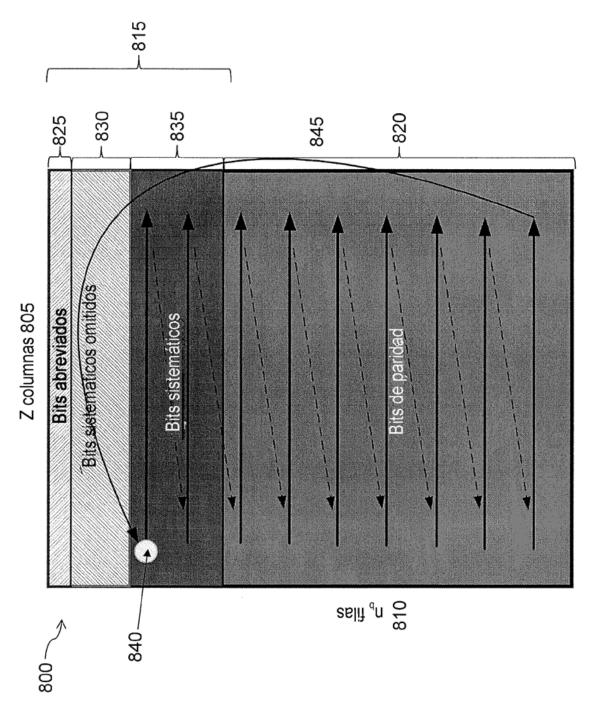

la figura 8 ilustra un ejemplo en el que se aplica en primer lugar abreviación a los bits sistemáticos que se omiten, y a los bits no omitidos si el número de bits abreviados es mayor que el número de bits omitidos, según determinadas realizaciones:

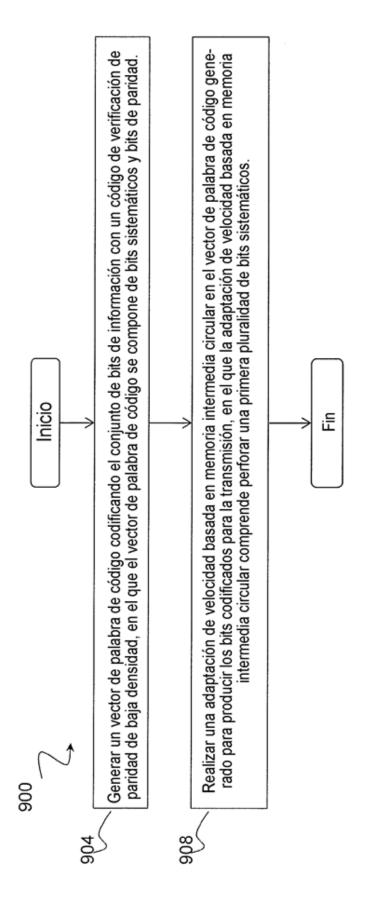

la figura 9 es un diagrama de flujo de un método en un primer nodo, según determinadas realizaciones;

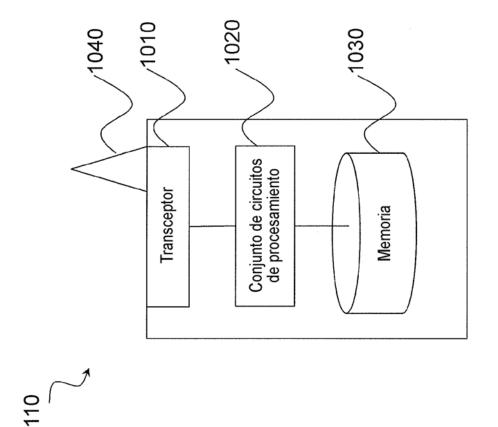

la figura 10 es un diagrama de bloques de un dispositivo inalámbrico a modo de ejemplo, según determinadas realizaciones;

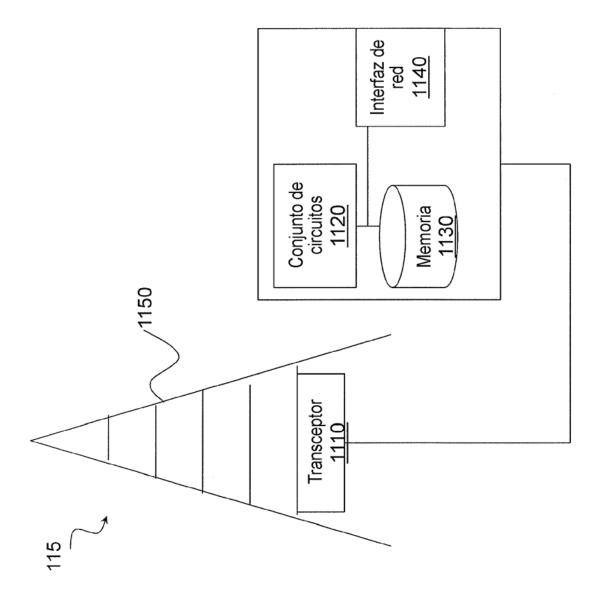

la figura 11 es un diagrama de bloques de un nodo de red a modo de ejemplo, según determinadas realizaciones;

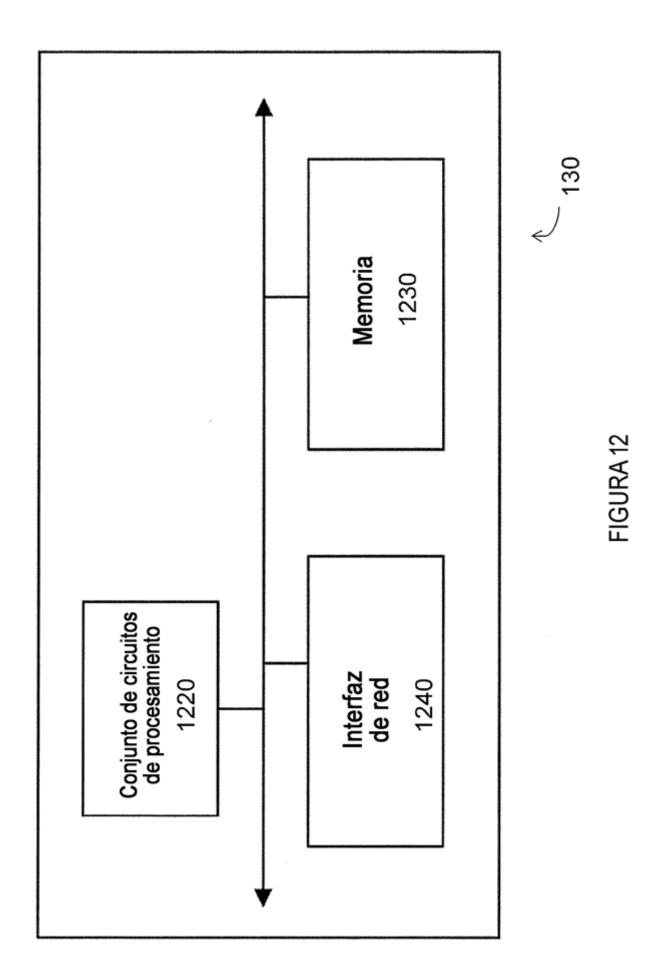

la figura 12 es un diagrama de bloques de un controlador de red radioeléctrica o nodo de red central a modo de ejemplo, según determinadas realizaciones;

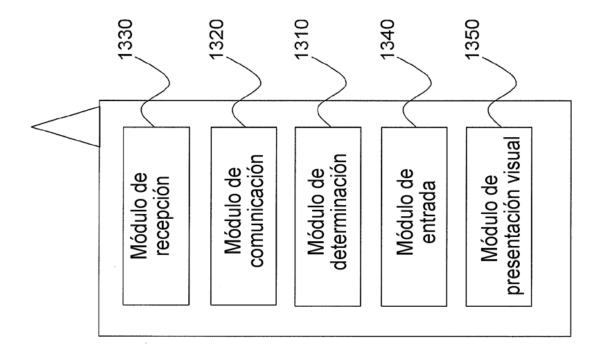

la figura 13 es un diagrama de bloques de un dispositivo inalámbrico a modo de ejemplo, según determinadas realizaciones; y

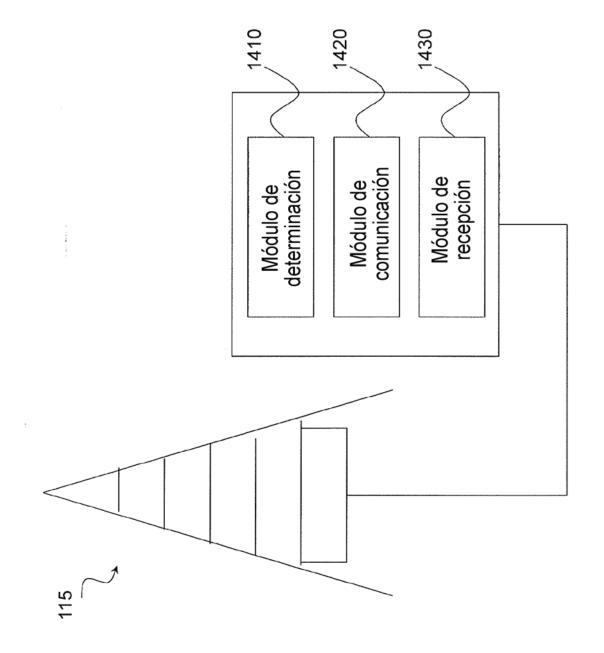

15 la figura 14 es un diagrama de bloques de un nodo de red a modo de ejemplo, según determinadas realizaciones.

#### Descripción detallada

30

35

40

45

50

55

60

65

Tal como se describió anteriormente, dado un código LDPC dedicado de tamaño de código (k, n), es necesario un método de adaptación de velocidad simple y efectivo para el tamaño de código real (Ktx, Ntx) necesario para una transmisión particular. Algunos códigos LDPC perforan algunos bits sistemáticos por diseño para mejorar el rendimiento del código, de manera no relacionada con la adaptación de velocidad. Sin embargo, no está claro cómo realizar la adaptación de velocidad, por ejemplo, tal como se define en 802.11n, en este caso. La presente divulgación contempla diversas realizaciones que pueden proporcionar un método de adaptación de velocidad simple y efectivo para códigos LDPC, en el que se aplica abreviación, perforación y/o repetición.

En determinadas realizaciones, la adaptación de velocidad mediante abreviación y perforación puede aplicarse a un código madre con la mayor velocidad de código posible. Si el número de bits de paridad especificados por el código madre es aproximadamente igual al número de bits de paridad necesarios para el código deseado, la adaptación de velocidad puede lograrse principalmente mediante abreviación en lugar de perforación, con una menor pérdida de rendimiento como resultado.

Según una realización de ejemplo, se divulga un método de producción de un conjunto de bits codificados a partir de un conjunto de bits de información para la transmisión entre un primer nodo y un segundo nodo en un sistema de comunicaciones inalámbricas. El primer nodo genera un vector de palabra de código codificando el conjunto de bits de información con un código LDPC, en el que el vector de palabra de código se compone de bits sistemáticos y bits de paridad. El primer nodo realiza una adaptación de velocidad basada en memoria intermedia circular en el vector de palabra de código generado para producir los bits codificados para la transmisión, en el que la adaptación de velocidad basada en memoria intermedia circular comprende perforar una primera pluralidad de bits sistemáticos. En determinadas realizaciones, el código LDPC puede especificarse a través de una PCM. La primera pluralidad de bits sistemáticos que se perforan puede preceder, en el vector de la palabra de código, a una segunda pluralidad de bits sistemáticos que no se perforan.

En determinadas realizaciones, puede definirse una pluralidad de versiones de redundancia sobre la memoria intermedia circular de tal manera que los bits codificados para una retransmisión se leen de la memoria intermedia circular según una versión de redundancia correspondiente definida para la retransmisión. El primer nodo puede realizar una adaptación de velocidad basada en memoria intermedia circular en el vector de palabra de código generado para producir bits codificados para la retransmisión, en el que la adaptación de velocidad basada en memoria intermedia circular para la retransmisión comprende perforar la primera pluralidad de bits sistemáticos. La primera pluralidad de bits sistemáticos perforados para la retransmisión puede incluir un múltiplo par de Z bits sistemáticos, donde Z es un factor de elevación de la matriz de verificación de paridad.

En determinadas realizaciones, el primer nodo puede perforar la primera pluralidad de bits sistemáticos al omitir la escritura de la primera pluralidad de bits sistemáticos en una memoria intermedia circular. En determinadas realizaciones, el primer nodo puede perforar la primera pluralidad de bits sistemáticos omitiendo la primera pluralidad de bits sistemáticos al leer los bits codificados de una memoria intermedia circular.

Determinadas realizaciones de la presente divulgación pueden proporcionar una o más ventajas técnicas. Por ejemplo, en determinadas realizaciones, los métodos de adaptación de velocidad basada en memoria intermedia circular pueden diseñarse de tal manera que puede proporcionarse una matriz arbitraria (Ktx, Ntx) mediante un único procedimiento. Como otro ejemplo, en determinadas realizaciones puede que no haya necesidad de definir un procedimiento independiente para cada uno de los abreviación, perforación y repetición. Otras ventajas pueden resultar fácilmente evidentes para un experto en la técnica. Determinadas realizaciones pueden tener ninguna, algunas o todas las ventajas mencionadas.

La figura 2 es un diagrama de bloques que ilustra una realización de una red 100, según determinadas realizaciones.

La red 100 incluye uno o más UE(s) 110 (que pueden denominarse indistintamente dispositivos 110 inalámbricos) y uno o más nodos 115 de red. Los UE 110 pueden comunicarse con los nodos 115 de red a través de una interfaz inalámbrica. Por ejemplo, un UE 110 puede transmitir señales inalámbricas a uno o más de los nodos 115 de red, y/o recibir señales inalámbricas desde uno o más de los nodos 115 de red. Las señales inalámbricas pueden contener tráfico de voz, tráfico de datos, señales de control y/o cualquier otra información adecuada. En algunas realizaciones, un área de cobertura de señales inalámbricas asociada con un nodo 115 de red puede denominarse célula. En algunas realizaciones, los UE 110 pueden tener capacidad de dispositivo a dispositivo (D2D). Por tanto, los UE 110 pueden recibir señales desde y/o transmitir señales directamente a otro UE.

- 10 En determinadas realizaciones, los nodos 115 de red pueden interconectarse con un controlador de red radioeléctrica. El controlador de red radioeléctrica puede controlar nodos 115 de red y puede proporcionar determinadas funciones de gestión de recursos de radio, funciones de gestión de movilidad y/u otras funciones adecuadas. En determinadas realizaciones, las funciones del controlador de red radioeléctrica pueden incluirse en el nodo 115 de red. El controlador de red radioeléctrica puede interconectarse con un nodo de red central. En determinadas realizaciones, el controlador 15 de red radioeléctrica puede interconectarse con el nodo de red central a través de una red de interconexión. La red de interconexión puede referirse a cualquier sistema de interconexión capaz de transmitir audio, vídeo, señales, datos, mensajes o cualquier combinación de los anteriores. La red de interconexión puede incluir la totalidad o una parte de una red telefónica pública conmutada (RTPC), una red de datos pública o privada, una red de área local (LAN, por sus siglas en inglés), una red de área metropolitana (MAN, por sus siglas en inglés), una red de área amplia (WAN, por 20 sus siglas en inglés), una red local, regional o mundial de comunicación o informática, tal como Internet, una red alámbrica o inalámbrica, una Intranet empresarial o cualquier otro enlace de comunicación adecuado, incluyendo combinaciones de las mismas.

- En algunas realizaciones, el nodo de red central puede gestionar el establecimiento de sesiones de comunicación y otras funcionalidades diversas para los UE 110. Los UE 110 pueden intercambiar determinadas señales con el nodo de red central usando la capa de estrato sin acceso (NAS, por sus siglas en inglés). En la señalización NAS, las señales entre los UE 110 y el nodo de la red central pueden hacerse pasar de manera transparente a través de la red de acceso radioeléctrico (RAN, por sus siglas en inglés). En determinadas realizaciones, los nodos 115 de red pueden interconectarse con uno o más nodos de red a través de una interfaz internodo tal como, por ejemplo, una interfaz X2.

30

50

55

- Tal como se describió anteriormente, las realizaciones de ejemplo de la red 100 pueden incluir uno o más dispositivos 110 inalámbricos, y uno o más tipos diferentes de nodos de red capaces de comunicarse (directa o indirectamente) con dispositivos 110 inalámbricos.

- En algunas realizaciones, se usa el término no limitativo UE. Los UE 110 descritos en el presente documento pueden ser cualquier tipo de dispositivo inalámbrico capaz de comunicarse con los nodos 115 de red u otro UE a través de señales de radio. El UE 110 también puede ser un dispositivo de comunicación por radio, dispositivo de destino, UE D2D, UE de comunicación de tipo máquina o UE capaz de producir comunicación de máquina a máquina (M2M), UE de bajo coste y/o baja complejidad, un sensor equipado con UE, tableta, terminales móviles, teléfono inteligente, equipo incorporado en ordenador portátil (LEE, por sus siglas en inglés), equipo montado en ordenador portátil (LME), llaves USB, equipo local de cliente (CPE, por sus siglas en inglés), etc. El UE 110 puede funcionar con cobertura normal o cobertura mejorada con respecto a su celda que le da servicio. La cobertura mejorada puede denominarse indistintamente cobertura extendida. El UE 110 también puede funcionar en una pluralidad de niveles de cobertura (por ejemplo, cobertura normal, nivel de cobertura mejorado 1, nivel de cobertura mejorado 2, nivel de cobertura mejorado 3, etc.). En algunos casos, el UE 110 también puede funcionar en situaciones fuera de cobertura.

- Además, en algunas realizaciones, se usa la terminología genérica, "nodo de red". Puede ser cualquier tipo de nodo de red, que puede comprender una estación base (BS, por sus siglas en inglés), estación base de radio, nodo B, estación base (BS), nodo de radio de radio multiestándar (MSR, por sus siglas en inglés) tal como BS de MSR, nodo B evolucionado (eNB), gNB, controlador de red, controlador de red radioeléctrica (RNC, por sus siglas en inglés), controlador de estación base (BSC, por sus siglas en inglés), nodo de retransmisión, relé de control de nodo donante de relé, estación de transceptor base (BTS, por sus siglas en inglés), punto de acceso (AP, por sus siglas en inglés), punto de acceso radioeléctrico, puntos de transmisión, nodos de transmisión, unidad de radio remota (RRU, por sus siglas en inglés), cabezal de radio remoto (RRH, por sus siglas en inglés), nodos en un sistema de antenas distribuido (DAS, por sus siglas en inglés), entidad de coordinación multicelular/multidifusión (MCE, por sus siglas en inglés), nodo de red central (por ejemplo, centro de conmutación móvil (MSC, por sus siglas en inglés), entidad de gestión de movilidad (MME, por sus siglas en inglés), etc.), operaciones y gestión (O&M, por sus siglas en inglés), nodo de posicionamiento (por ejemplo, centro de localización móvil de servicio evolucionado (E-SMLC, por sus siglas en inglés)), minimización de las pruebas de campo (MDT, por sus siglas en inglés), o cualquier otro nodo de red adecuado.

- En determinadas realizaciones, se usa la terminología genérica "nodo". Puede ser cualquier clase de UE o nodo de red, tal como el UE 110 o nodo 115 de red descritos anteriormente.

- La terminología, tal como nodo de red y UE, debe considerarse no limitativa y, en particular, no implica una determinada relación jerárquica entre los dos. En general, "nodo de red" podría considerarse como dispositivo 1 (o un

primer nodo) y "UE" dispositivo 2 (o un segundo nodo), y estos dos dispositivos se comunican entre sí por algún canal de radio.

Las realizaciones de ejemplo del UE 110, los nodos 115 de red y otros nodos de red (tales como el controlador de red radioeléctrica o el nodo de red central) se describen con más detalle a continuación con respecto a las figuras 10-14.

5

10

15

20

25

40

45

50

55

60

65

Aunque la figura 2 ilustra una disposición particular de la red 100, la presente divulgación contempla que las diversas realizaciones descritas en el presente documento pueden aplicarse a una variedad de redes que tienen cualquier configuración adecuada. Por ejemplo, la red 100 puede incluir cualquier número adecuado de UE 110 y nodos 115 de red, así como cualquier elemento adicional adecuado para soportar la comunicación entre UE o entre un UE y otro dispositivo de comunicación (tal como un teléfono fijo). Además, aunque determinadas realizaciones pueden describirse como implementadas en una red de nueva radio (NR), las realizaciones pueden implementarse en cualquier tipo apropiado de sistema de telecomunicaciones que soporte cualquier norma de comunicación adecuado (incluyendo normas 5G) y que use cualquier componente adecuado, y sean aplicables a cualquier tecnología de acceso radioeléctrico (RAT, por sus siglas en inglés) o sistemas multi-RAT en los que un UE recibe y/o transmite señales (por ejemplo, datos). Por ejemplo, las diversas realizaciones descritas en el presente documento pueden ser aplicables a NR, evolución a largo plazo (LTE), LTE avanzado, 5G, UMTS, HSPA, GSM, cdma2000, WCDMA, WiMax, UMB, WiFi, 802.11n, otra tecnología de acceso radioeléctrico adecuada o cualquier combinación adecuada de una o más tecnologías de acceso radioeléctrico. Aunque determinadas realizaciones pueden describirse en el contexto de transmisiones inalámbricas en el enlace descendente (DL, downlink), la presente divulgación contempla que las diversas realizaciones son igualmente aplicables en el enlace ascendente (UL, uplink).

Tal como se describió anteriormente, dado un código LDPC dedicado de tamaño de código (k, n), es necesario un método de adaptación de velocidad simple y efectivo para el tamaño de código real (K<sub>Ix</sub>, N<sub>Ix</sub>) necesario para una transmisión particular (por ejemplo, entre un primer nodo y un segundo nodo en un sistema de comunicaciones inalámbricas, tal como un sistema NR). En determinadas realizaciones, se describe un método efectivo de adaptación de velocidad para códigos LDPC, en el que se aplica abreviación, perforación y/o repetición.

En determinadas realizaciones, un primer nodo (por ejemplo, uno de los nodos 115 de red descritos anteriormente) produce un conjunto de bits codificados a partir de un conjunto de bits de información para su transmisión a un segundo nodo (por ejemplo, uno de los UE 110 descritos anteriormente) en un sistema de comunicaciones inalámbricas. En determinadas realizaciones, el sistema de comunicaciones inalámbricas puede ser un sistema NR. El conjunto de bits de información puede estar asociado con una transmisión entre el primer nodo y el segundo nodo en el sistema de comunicaciones inalámbricas. Obsérvese que aunque determinadas realizaciones pueden describirse usando uno de los nodos 115 de red como el primer nodo y uno de los UE 110 como el segundo nodo, esto es sólo con propósitos de ejemplo y las diversas realizaciones descritas en el presente documento no se limitan a tal ejemplo. Más bien, la presente divulgación contempla que el primer nodo y el segundo nodo pueden ser entidades de red adecuadas.

En determinadas realizaciones, el primer nodo genera un vector de información a partir de un conjunto de bits de información. Para ilustrarlo, considérese el siguiente ejemplo. Supóngase para un conjunto de  $k_{tx}$  bits de información que la codificación del código LDPC puede realizarse usando el siguiente procedimiento, donde la matriz de verificación de paridad cuasicíclica H se compone de (n-k) filas y n columnas,  $m_b = m/Z$  y  $n_b = n/Z$ . En determinadas realizaciones, generar un vector de información a partir del conjunto de bits de información puede comprender unir (k -  $k_{tx}$ ) bits ficticios al conjunto de  $k_{tx}$  bits de información para producir un vector de información U de k bits. A los bits ficticios generalmente se les asigna un valor conocido de "0". La unión de bits ficticios a bits de información también puede denominarse abreviación del código. En determinadas realizaciones, la unión de bits ficticios al conjunto de bits de información puede comprender copiar el conjunto de bits de información en un vector más largo de longitud "bits de información + bits ficticios". En determinadas realizaciones, el primer nodo puede perforar los bits ficticios unidos (por ejemplo, al no escribir los bits ficticios unidos en la memoria intermedia circular o al no leer los bits ficticios unidos de la memoria intermedia circular).

El primer nodo genera un vector de palabra de código codificando el conjunto de bits de información con un código LDPC. El vector de palabra de código puede componerse de bits sistemáticos y bits de paridad. Los códigos LDPC considerados en este caso son códigos LDPC basados en un grafo prototipo cuasicíclico. Las PCM cuasicíclicas se dividen en subbloques cuadrados (submatrices) de tamaño Z × Z. Estas submatrices son o bien permutaciones cíclicas de la matriz identidad o bien submatrices nulas. Una matriz de permutación cíclica Pi se obtiene a partir de la matriz identidad Z × Z desplazando cíclicamente las columnas a la derecha en i elementos. La matriz P0 es la matriz identidad Z × Z. El código LDPC puede especificarse a través de una PCM. Los códigos LDPC cuasicíclicos se describen convenientemente a través de una matriz base, que es una matriz en la que cada número entero i indica la matriz de permutación cíclica Pi. La PCM se obtiene a partir de una matriz base seleccionando un tamaño de elevación Z y reemplazando cada entrada en la matriz base por la matriz Z × Z correspondiente.

Continuando con el ejemplo anterior, en determinadas realizaciones, el primer nodo codifica el vector de información U con la PCM H. La codificación genera un vector de palabra de código C de n bits. Normalmente, se usa codificación sistemática para que el vector de palabra de código C se componga de dos conjuntos de bits: [bits sistemáticos; bits de paridad]. En este ejemplo, el vector de bits sistemáticos de longitud k es igual al vector de información U. Los bits

sistemáticos de longitud k, k =  $k_b*Z$ , son  $k_b$  grupos de Z bits, [ $u_0$ ,  $u_1$ , ....  $u_{z-1}$ , |  $u_z$ ,  $u_{z+1}$ , ....  $u_{2z-1}$ , |...,  $u_{-(k_{b-1})*Z}$ ,  $u_{-(k_{b-1})*Z+1}$ , ....  $u_{-(k_b*Z-1)}$ ]. Los bits de paridad de longitud (n-k), m = n-k =  $m_b*Z$ , son  $m_b$  grupos de Z bits, [ $p_0$ ,  $p_1$ , ....  $p_{z-1}$ , |  $p_z$ ,  $p_{z+1}$ , ....  $p_{2z-1}$ , |...,  $p_{-(m_{b-1})*Z}$ ,  $p_{-(m_{b-1})*Z+1}$ , ....  $p_{-(m_{b-1})*Z+1}$ , .....  $p_{-(m_{b-1})*Z+1}$ , ....  $p_{-(m_{b-1})*Z+1}$ , ....  $p_{-(m_$

El primer nodo realiza una adaptación de velocidad basada en memoria intermedia circular en el vector de palabra de código generado para producir los bits codificados para la transmisión. La adaptación de velocidad basada en memoria intermedia circular puede comprender perforar una primera pluralidad de bits sistemáticos (por ejemplo, cuando se produce un vector de transmisión a partir del vector de palabra de código). Continuando con el ejemplo anterior, en determinadas realizaciones, el primer nodo realiza una adaptación de velocidad en el vector de palabra de código C, retira los (k - ktx) bits ficticios, y produce un vector de longitud ntx para la transmisión por el canal inalámbrico.

En la siguiente descripción de las figuras 3-8, se supone que al menos una parte de los [bits sistemáticos, bits de paridad] definidos por la PCM se escriben en una memoria intermedia circular. En los ejemplos de las figuras 3-8, la "memoria intermedia circular" usada para la adaptación de velocidad se presenta en un formato rectangular. Sin embargo, debe entenderse que el inicio de un nuevo ciclo cuando se llega al final del rectángulo significa que la memoria intermedia es circular. Además, obsérvese que la presentación de la memoria intermedia circular en formato rectangular es sólo con propósitos de ejemplo, y las diversas realizaciones descritas en el presente documento no se limitan a tal ejemplo.

En los ejemplos de las figuras 3-8, esos [bits sistemáticos, bits de paridad] definidos por la PCM que se escriben en la memoria intermedia circular rectangular se escriben a lo largo de filas, comenzando desde la esquina superior izquierda, terminando en la esquina inferior derecha. Como ejemplo, después de escribir los bits en el rectángulo, puede usarse para generar una palabra de código de longitud de bloque arbitraria  $n_{tx}$ . En tal situación, los  $n_{tx}$  bits se leen del rectángulo. Como otro ejemplo, después de escribir los bits en el rectángulo, puede usarse para generar retransmisiones que van a usarse en/para redundancia incremental. En tal situación, para la primera transmisión, se leen algunos bits. En caso de una segunda transmisión, se lee un número adicional de bits. Mientras que la lectura de cada retransmisión puede comenzar en cualquier parte de la memoria intermedia circular de forma rectangular, preferiblemente la lectura comienza cerca de donde terminó la lectura de la transmisión anterior. Esto puede generalizarse a más de una retransmisión.

Las figuras 3-8 a continuación ilustran diversas realizaciones de ejemplo de cómo los [bits sistemáticos, bits de paridad] se leen de la memoria intermedia circular rectangular para producir los  $n_{tx}$  bits para la transmisión (por ejemplo, a un segundo nodo). En determinadas realizaciones, el primer nodo puede contar  $n_{tx}$  bits del rectángulo y transmitirlos. En determinadas realizaciones, una o más reglas predefinidas pueden influir en cómo se leen los bits de la memoria intermedia circular rectangular para producir los  $n_{tx}$  bits para la transmisión. Como ejemplo, si  $n_{tx}$  es menor que el número total de bits en la memoria intermedia circular, entonces los bits que quedan en el rectángulo se perforan (es decir, no se transmiten). Como otro ejemplo, si  $n_{tx}$  es mayor que el número total de bits en la memoria intermedia circular, entonces el procedimiento de lectura inicia un nuevo ciclo y algunos bits en la memoria intermedia circular se repiten, lo que conduce al efecto de repetición de la adaptación de velocidad. Como todavía otro ejemplo, si los  $k_{tx}$  bits de información real se unen con  $(k - k_{tx})$  bits de valor conocido antes de la codificación con la PCM, entonces se logra la abreviación. En algunos casos, los  $(k - k_{tx})$  bits de abreviación pueden anteponerse delante de los  $k_{tx}$  bits de información real. En algunos casos, los  $(k - k_{tx})$  bits de abreviación pueden unirse al final de los  $k_{tx}$  bits de información real. Los bits abreviados se conocen y no portan información, por tanto, deben retirarse antes de la transmisión.

Como aún otro ejemplo, en los casos de una PCM en la que algunos de los bits de información se perforan por diseño, estos bits de información pueden quedar fuera de la memoria intermedia circular rectangular. En las figuras 3-8 a continuación, estos bits de información se denominan bits omitidos. Como otro ejemplo, en el caso de una PCM en la que algunos de los bits de información se perforan por diseño, combinado con abreviación, los bits perforados o bien pueden formar parte de los bits abreviados o bien no formar parte de los bits abreviados.

La figura 3 ilustra un ejemplo en el que los bits sistemáticos y los bits de paridad se leen a lo largo de columnas, de modo que también se implementa un intercalador de canales como parte del procedimiento de adaptación de velocidad, según determinadas realizaciones. La figura 3 ilustra una memoria 300 intermedia circular rectangular con Z columnas 305 y n<sub>b</sub> filas 310. Dentro de la memoria 300 intermedia circular rectangular, hay una pluralidad de bits 315 sistemáticos y una pluralidad de bits 320 de paridad. La pluralidad de bits 315 sistemáticos incluye bits 325 sistemáticos que no se omiten y una pluralidad de bits 330 sistemáticos que se omiten (es decir, se perforan). En el ejemplo de la figura 3, los bits se leen de la memoria 300 intermedia circular rectangular comenzando en el punto 335 de inicio. La flecha 340 ilustra el inicio de un nuevo ciclo que se produce cuando se alcanza el final de la memoria 300 intermedia circular rectangular.

Tal como se muestra en el ejemplo de la figura 3, puesto que hay  $Z^*n_b$  columnas (o bits de palabras de código) en H, un modo es formar un rectángulo 300 (de  $n_b$  filas \* Z columnas), y bits de perforación a lo largo de columnas. El efecto es perforar bits de manera uniforme de cada una de las filas de tamaño Z, y mantener aproximadamente la misma distribución de peso que la H original. Esto tiene el efecto de perforar un bit de cada uno del conjunto de  $n_b$  primero, donde cada conjunto tiene Z bits. En determinadas realizaciones, la pluralidad de bits 330 sistemáticos que se omiten

(es decir, se perforan) incluyen un múltiplo par de Z bits sistemáticos, donde Z es un factor de elevación de la PCM.

Tal como se ilustra en la figura 3, algunos de los bits 315 sistemáticos pueden perforarse (es decir, los bits 330 sistemáticos omitidos) para lograr un mejor rendimiento que la perforación de los bits 320 de paridad. Los bits sistemáticos perforados en la 1ª transmisión, o para un código de mayor velocidad, se mapean generalmente en un peso de columna alto. La ubicación 335 de inicio (x, y) puede elegirse de modo que se omita el grupo apropiado de bits sistemáticos (es decir, se perforen), mientras se mantiene el rendimiento de decodificación lo mejor posible.

Aunque la figura 3 ilustra bits 330 sistemáticos omitidos incluyendo en la memoria 300 intermedia circular rectangular, este es sólo un ejemplo no limitativo. En determinadas realizaciones, por ejemplo, los bits 330 sistemáticos omitidos pueden no escribirse en la memoria 300 intermedia circular. Puesto que el código está diseñado con el conocimiento de que los primeros bits sistemáticos se perforarán, en algunos casos estos bits no deben incluirse en absoluto en la memoria 300 intermedia circular. Puede ser más ventajoso repetir cualquiera de los bits ya transmitidos que transmitir los primeros bits sistemáticos diseñados para perforarse. Esto es una consecuencia del grado de nodo variable muy alto de los bits 330 sistemáticos perforados, lo que implica que estos nodos/bits tienen una alta conectividad con el resto del grafo y su valor puede deducirse a menudo a partir del valor de otros bits.

La figura 4 ilustra un ejemplo en el que los bits sistemáticos y los bits de paridad se leen a lo largo de filas, según determinadas realizaciones. La figura 4 ilustra una memoria 400 intermedia circular rectangular con Z columnas 405 y n<sub>b</sub> filas 410. Dentro de la memoria 400 intermedia circular rectangular, hay una pluralidad de bits 415 sistemáticos y una pluralidad de bits 420 de paridad. La pluralidad de bits 415 sistemáticos incluye bits 425 sistemáticos que no se omiten y una pluralidad de bits 430 sistemáticos que se omiten. En el ejemplo de la figura 4, los bits se leen de la memoria 400 intermedia circular rectangular comenzando en el punto 435 de inicio. La flecha 440 ilustra el inicio de un nuevo ciclo que se produce cuando se alcanza el final de la memoria 400 intermedia circular rectangular.

20

25

40

45

50

55

60

65

Tal como se indicó anteriormente, en el ejemplo mostrado en la figura 4, los bits 425 sistemáticos y los bits 420 de paridad se leen a lo largo de filas. Por tanto, no se implementa ningún efecto de intercalación de canales (en contraste con el ejemplo de la figura 3 descrito anteriormente).

30 Además, dado que la perforación de columnas de alto peso tienen menos impacto en el rendimiento, el patrón de perforación puede disponerse de modo que se perforen más bits de columna de alto peso que bits de columna de bajo peso. Sería posible buscar qué bits 420 de paridad perforar que tengan el menor impacto sobre el umbral. Los nodos en el grafo prototipo, que corresponde a la n<sub>b</sub> filas, pueden reordenarse entonces para que la perforación desde el final de la memoria 400 intermedia circular rectangular sea óptima.

La figura 5 ilustra un ejemplo en el que, cuando se alcanza el final de la memoria intermedia circular, se inicia un nuevo ciclo para los bits sistemáticos que se omitieron en una primera transmisión, según determinadas realizaciones. La figura 5 ilustra una memoria 500 intermedia circular rectangular con Z columnas 505 y n<sub>b</sub> filas 510. Dentro de la memoria 500 intermedia circular rectangular, hay una pluralidad de bits 515 sistemáticos y una pluralidad de bits 520 de paridad. La pluralidad de bits 515 sistemáticos incluye bits 525 sistemáticos que no se omiten en una primera transmisión y una pluralidad de bits 530 sistemáticos que se omiten en la primera transmisión. En el ejemplo de la figura 5, los bits se leen de la memoria 500 intermedia circular rectangular comenzando en el punto 535 de inicio. La flecha 540 ilustra el inicio de un nuevo ciclo que se produce cuando se alcanza el final de la memoria 500 intermedia circular rectangular.

Tal como se describió anteriormente, la figura 5 ilustra un ejemplo en el que, cuando se alcanza el final de la memoria 500 intermedia circular, se inicia un nuevo ciclo para los bits 530 sistemáticos que se omitieron en la primera transmisión (tal como se muestra con la flecha 540). En la realización de ejemplo de la figura 5, los bits 530 sistemáticos que se omitieron en la primera transmisión, o para la generación de una palabra de código de mayor velocidad, se incluyen en una retransmisión, o cuando se genera una palabra de código a baja velocidad.

En determinadas realizaciones, los bits pueden leerse de la memoria 500 intermedia circular rectangular de forma horizontal (es decir, a lo largo de filas), comenzando en el punto 535 de inicio.

La figura 6 ilustra un ejemplo en el que la memoria intermedia circular usa un subconjunto de bits codificados tal como se definen mediante la PCM, de modo que la velocidad de código usada para la transmisión real es mayor que la velocidad de código R de la PCM, según determinadas realizaciones. La figura 6 ilustra una memoria 600 intermedia circular rectangular con Z columnas 605, n<sub>b</sub> filas 610 y n<sub>b,1</sub> filas 615. Tal como se muestra en la figura 6, hay una pluralidad de bits 620 sistemáticos y una pluralidad de bits 625 de paridad. La pluralidad de bits 620 sistemáticos incluye bits 630 sistemáticos que no se omiten y una pluralidad de bits 635 sistemáticos que se omiten. La pluralidad de bits 625 de paridad incluye bits 640 de paridad que se perforan del código madre y bits 645 de paridad que no se perforan del código madre. En el ejemplo de la figura 6, los bits se leen de la memoria 600 intermedia circular rectangular comenzando en el punto 650 de inicio. La flecha 655 ilustra el inicio de un nuevo ciclo que se produce cuando se alcanza el final de la memoria 600 intermedia circular rectangular.

En la realización de ejemplo mostrada en la figura 6, algunos de los bits 625 de paridad generados a partir de la PCM

no se colocan en el rectángulo y se transmiten (es decir, bits de paridad que se perforan del código madre 640), pero se generan retransmisiones y velocidades de código más bajas leyendo de nuevo desde la parte superior izquierda del rectángulo (es decir, en el punto 650 de inicio). Esto puede ser útil, por ejemplo, si se prefiere una decodificación de menor complejidad, porque sólo se requiere una submatriz de la PCM para decodificar la transmisión en este caso.

5

10

15

20

25

30

35

40

45

En determinadas realizaciones, los bits pueden leerse de la memoria 600 intermedia circular rectangular en vertical (es decir, a lo largo de columnas), comenzando en el punto 650 de inicio.

La figura 7 ilustra un ejemplo en el que también se implementa abreviación como parte del procedimiento de adaptación de velocidad, según determinadas realizaciones. La figura 7 ilustra una memoria 700 intermedia circular rectangular con Z columnas 705 y n<sub>b</sub> filas 710. Dentro de la memoria 700 intermedia circular rectangular, hay una pluralidad de bits 715 sistemáticos y una pluralidad de bits 720 de paridad. La pluralidad de bits 715 sistemáticos incluye una pluralidad de bits 725 sistemáticos que se omiten, una pluralidad de bits 730 sistemáticos que no se omiten, y una pluralidad de bits 735 abreviados. En el ejemplo de la figura 7, los bits se leen de la memoria 700 intermedia circular rectangular comenzando en el punto de inicio 740. La flecha 745 ilustra el inicio de un nuevo ciclo que se produce cuando se alcanza el final de la memoria 700 intermedia circular rectangular.

Tal como se describió anteriormente, en la realización de ejemplo de la figura 7, también se implementa abreviación como parte del procedimiento de adaptación de velocidad. En el ejemplo de la figura 7, los bits 735 abreviados se eligen en primer lugar entre los bits 730 sistemáticos que no se omiten. En algunos casos, si el número de bits abreviados es mayor que el número de bits 730 sistemáticos que no se omiten, algunos de los bits 725 sistemáticos omitidos también se abreviarán. Los bits abreviados se establecen en un valor conocido y se omiten al leer la palabra de código que va a transmitirse (ya que se conocen en el receptor). El receptor (por ejemplo, un segundo nodo) inserta valores de fiabilidad infinita para los bits abreviados y calcula la fiabilidad para el resto de los bits usando un rectángulo similar. Según una realización alternativa de ejemplo, los bits pueden leerse de forma vertical, omitiéndose de nuevo los bits 735 abreviados y los bits 725 que están diseñados para omitirse.

La figura 8 ilustra un ejemplo en el que se aplica abreviación en primer lugar a aquellos bits sistemáticos que se omiten, y sólo a bits no omitidos si el número de bits abreviados es mayor que el número de bits omitidos, según determinadas realizaciones. La figura 8 ilustra una memoria 800 intermedia circular rectangular con Z columnas 805 y n₀ filas 810. Dentro de la memoria 800 intermedia circular rectangular, hay una pluralidad de bits 815 sistemáticos y una pluralidad de bits 820 de paridad. La pluralidad de bits 815 sistemáticos incluye una pluralidad de bits 825 abreviados, una pluralidad de bits 830 sistemáticos que se omiten, y una pluralidad de bits 835 sistemáticos que no se omiten. En el ejemplo de la figura 8, los bits se leen de la memoria 800 intermedia circular rectangular comenzando en el punto de inicio 840. La flecha 845 ilustra el inicio de un nuevo ciclo que se produce cuando se alcanza el final de la memoria 800 intermedia circular rectangular.

En la realización de ejemplo de la figura 8, los bits 825 de información abreviados se eligen en primer lugar de los bits 830 sistemáticos que se omiten, y sólo si es necesario abreviar más bits que el número de bits omitidos, se abrevian los otros bits 835 sistemáticos. En determinadas realizaciones, los bits pueden leerse de forma vertical.

En determinadas realizaciones, las diversas realizaciones descritas anteriormente con respecto a las figuras 3-8 pueden combinarse adicionalmente. La presente divulgación contempla que las diversas realizaciones de ejemplo descritas anteriormente pueden combinarse de cualquier manera adecuada. Por ejemplo, las realizaciones de ejemplo descritas anteriormente en relación con las figuras 7 y 8 pueden combinarse con la realización de ejemplo de la figura 5 de modo que los bits sistemáticos que se omiten al principio puedan incluirse en códigos de menor velocidad, o en retransmisiones. Sin embargo, obsérvese que los bits abreviados no se incluyen en una transmisión ya que los conoce el receptor.

La figura 9 es un diagrama de flujo de un método 900 en un primer nodo, según determinadas realizaciones. Más particularmente, el método 900 es un método de producción de un conjunto de bits codificados a partir de un conjunto de bits de información para la transmisión entre un primer nodo y un segundo nodo en un sistema de comunicaciones inalámbricas. El método 900 comienza en la etapa 904, en la que el primer nodo genera un vector de palabra de código codificando el conjunto de bits de información con un código de verificación de paridad de baja densidad, en el que el vector de palabra de código se compone de bits sistemáticos y bits de paridad. En determinadas realizaciones, el código LDPC puede especificarse a través de una PCM. El sistema de comunicaciones inalámbricas puede comprender un sistema NR.

En determinadas realizaciones, generar el vector de palabra de código codificando el conjunto de bits de información puede comprender unir bits ficticios al conjunto de bits de información, comprendiendo los bits ficticios bits de valor conocido, para producir un vector de información, y codificar el vector de información. Los bits ficticios unidos pueden comprender una segunda pluralidad de bits sistemáticos que está separada de la primera pluralidad perforada de bits sistemáticos. En determinadas realizaciones, el método puede comprender perforar los bits ficticios unidos. La perforación de los bits ficticios unidos puede comprender omitir la escritura de los bits ficticios unidos en la memoria intermedia circular. La perforación de los bits ficticios unidos puede comprender omitir los bits ficticios unidos cuando se leen los bits codificados de la memoria intermedia circular.

En la etapa 908, el primer nodo realiza una adaptación de velocidad basada en memoria intermedia circular en el vector de palabra de código generado para producir los bits codificados para la transmisión, en el que la adaptación de velocidad basada en memoria intermedia circular comprende perforar una primera pluralidad de bits sistemáticos. En determinadas realizaciones, la primera pluralidad de bits sistemáticos que se perforan puede preceder, en el vector de la palabra de código, a una segunda pluralidad de bits sistemáticos que no se perforan.

5

10

15

20

35

En determinadas realizaciones, puede definirse una pluralidad de versiones de redundancia por la memoria intermedia circular de tal manera que los bits codificados para una retransmisión se leen de la memoria intermedia circular según una versión de redundancia correspondiente definida para la retransmisión. El método 900 puede comprender realizar una adaptación de velocidad basada en memoria intermedia circular en el vector de palabra de código generado para producir bits codificados para la retransmisión, en el que la adaptación de velocidad basada en memoria intermedia circular para la retransmisión comprende perforar la primera pluralidad de bits sistemáticos. La primera pluralidad de bits sistemáticos perforados para la retransmisión puede incluir un múltiplo par de Z bits sistemáticos, donde Z es un factor de elevación de la matriz de verificación de paridad.

En determinadas realizaciones, perforar la primera pluralidad de bits sistemáticos puede comprender omitir la escritura de la primera pluralidad de bits sistemáticos en una memoria intermedia circular. En determinadas realizaciones, perforar la primera pluralidad de bits sistemáticos puede comprender omitir la primera pluralidad de bits sistemáticos cuando se leen los bits codificados de una memoria intermedia circular. En determinadas realizaciones, la primera pluralidad de bits sistemáticos perforados puede incluir un múltiplo par de Z bits sistemáticos, donde Z es un factor de elevación de la matriz de verificación de paridad.

En determinadas realizaciones, realizar una adaptación de velocidad basada en memoria intermedia circular en el vector de palabra de código generado puede comprender leer los bits sistemáticos y los bits de paridad fuera de una memoria intermedia circular para producir el vector de transmisión para la transmisión por un canal inalámbrico. La lectura de los bits sistemáticos y los bits de paridad de la memoria intermedia circular para producir el vector de transmisión para la transmisión por el canal inalámbrico puede comprender, si el número de bits del vector de transmisión es mayor que el número total de bits en la memoria intermedia circular, repetir uno o más bits en la memoria intermedia circular iniciando un nuevo ciclo.

En determinadas realizaciones, puede omitirse que un subconjunto de los bits sistemáticos se escriba en la memoria intermedia circular. En determinadas realizaciones, puede omitirse que un subconjunto de los bits de paridad se escriba en la memoria intermedia circular.

En determinadas realizaciones, el método puede comprender perforar un subconjunto de los bits sistemáticos escritos en la memoria intermedia circular en una primera transmisión por el canal inalámbrico. El método puede comprender incluir el subconjunto de los bits sistemáticos que se perforaron en una retransmisión por el canal inalámbrico.

En determinadas realizaciones, el método puede comprender perforar bits a lo largo de columnas de tal manera que se perforen bits de manera uniforme de cada una de una pluralidad de filas y se mantenga una distribución de peso de la matriz de verificación de paridad en la memoria intermedia circular. Los bits perforados pueden ser bits sistemáticos distintos de la primera pluralidad de bits sistemáticos. Los bits sistemáticos y los bits de paridad pueden leerse de tal manera que se implemente un intercalador de canales como parte de realizar la adaptación de velocidad basada en memoria intermedia circular en el vector de palabra de código generado. En determinadas realizaciones, los bits perforados pueden tener un mayor peso de columna que los bits no perforados. En determinadas realizaciones, los bits sistemáticos y los bits de paridad pueden leerse de tal manera que no se implemente ningún efecto de intercalación de canales.

50 En determinadas realizaciones, realizar una adaptación de velocidad basada en memoria intermedia circular en el vector de palabra de código generado puede comprender escribir al menos una parte de los bits sistemáticos y los bits de paridad tal como se definen mediante la PCM en una memoria intermedia circular rectangular, comprendiendo la memoria intermedia circular rectangular una o más filas y una o más columnas.

La figura 10 es un diagrama de bloques de un dispositivo 110 inalámbrico a modo de ejemplo, según determinadas realizaciones. El dispositivo 110 inalámbrico puede referirse a cualquier tipo de dispositivo inalámbrico que se comunique con un nodo y/o con otro dispositivo inalámbrico en un sistema de comunicación celular o móvil. Los ejemplos del dispositivo 110 inalámbrico incluyen un teléfono móvil, un teléfono inteligente, un PDA (asistente digital personal), un ordenador portátil (por ejemplo, tipo *laptop*, tableta), un sensor, un actuador, un módem, un dispositivo de comunicación de tipo máquina (MTC, por sus siglas en inglés) / dispositivo de máquina a máquina (M2M), equipo incorporado en ordenador portátil (LEE), equipo montado en ordenador portátil (LME), llaves USB, un dispositivo compatible con D2D u otro dispositivo que pueda proporcionar comunicación inalámbrica. Un dispositivo 110 inalámbrico también puede denominarse UE, una estación (STA), un dispositivo o un terminal en algunas realizaciones. El dispositivo 110 inalámbrico incluye el transceptor 1010, el conjunto 1020 de circuitos de procesamiento y la memoria 1030. En algunas realizaciones, el transceptor 1010 facilita la transmisión de señales inalámbricas y la recepción de señales inalámbricas desde el nodo 115 de red (por ejemplo, a través de la antena

1040), el conjunto 1020 de circuitos de procesamiento ejecuta instrucciones para proporcionar parte o la totalidad de la funcionalidad descrita anteriormente como proporcionada por el dispositivo 110 inalámbrico, y la memoria 1030 almacena las instrucciones ejecutadas por el conjunto 1020 de circuitos de procesamiento.

El conjunto 1020 de circuitos de procesamiento puede incluir cualquier combinación adecuada de hardware y software implementados en uno o más módulos para ejecutar instrucciones y manipular datos para realizar parte o la totalidad de las funciones descritas del UE 110, tales como las funciones del dispositivo 110 inalámbrico descrito anteriormente en relación con las figuras 1-9. En algunas realizaciones, el conjunto 1020 de circuitos de procesamiento puede incluir, por ejemplo, uno o más ordenadores, una o más unidades centrales de procesamiento (CPU), uno o más microprocesadores, una o más aplicaciones, uno o más circuitos integrados específicos de aplicación (ASIC), uno o más matrices de compuerta programables en campo (FPGA) y/u otra lógica.

La memoria 1030 puede hacerse funcionar generalmente para almacenar instrucciones, tales como un programa informático, software, una aplicación que incluye uno o más de lógica, reglas, algoritmos, código, tablas, etc. y/u otras instrucciones capaces de ejecutarse por el conjunto 1020 de circuitos de procesamiento. Los ejemplos de memoria 1030 incluyen memoria informática (por ejemplo, memoria de acceso aleatorio (RAM) o memoria de sólo lectura (ROM)), medios de almacenamiento masivo (por ejemplo, un disco duro), medios de almacenamiento extraíbles (por ejemplo, un disco compacto (CD) o un disco de vídeo digital (DVD)), y/o cualquier otro dispositivo de memoria volátil o no volátil, no transitoria y/o ejecutable por ordenador que almacene información, datos y/o instrucciones que puedan usarse por el conjunto 1020 de circuitos de procesamiento.

15

20

25

30

35

40

45

65

Otras realizaciones del dispositivo 110 inalámbrico pueden incluir componentes adicionales más allá de los mostrados en la figura 10 que pueden ser responsables de proporcionar determinados aspectos de la funcionalidad del dispositivo inalámbrico, incluyendo cualquiera de las funcionalidades descritas anteriormente y/o cualquier funcionalidad adicional (incluyendo cualquier funcionalidad necesaria para soportar la solución descrita anteriormente). Sólo como ejemplo, el dispositivo 110 inalámbrico puede incluir dispositivos y circuitos de entrada, dispositivos de salida y una o más unidades o circuitos de sincronización, que pueden formar parte del conjunto 1020 de circuitos de procesamiento. Los dispositivos de entrada incluyen mecanismos para la entrada de datos en el dispositivo 110 inalámbrico. Por ejemplo, los dispositivos de entrada pueden incluir mecanismos de entrada, tales como un micrófono, elementos de entrada, un elemento de presentación visual, etc. Los dispositivos de salida pueden incluir mecanismos para emitir datos en formato de audio, vídeo y/o copia impresa. Por ejemplo, los dispositivos de salida pueden incluir un altavoz, un elemento de presentación visual, etc.

La figura 11 es un diagrama de bloques de un nodo 115 de red a modo de ejemplo, según determinadas realizaciones. El nodo 115 de red puede ser cualquier tipo de nodo de red radioeléctrica o cualquier nodo de red que se comunique con un UE y/o con otro nodo de red. Los ejemplos del nodo 115 de red incluyen un eNodoB, un gNB, un nodo B, una estación base, un punto de acceso inalámbrico (por ejemplo, un punto de acceso Wi-Fi), un nodo de baja potencia, una estación de transceptor base (BTS), relé, relé de control de nodo donante, puntos de transmisión, nodos de transmisión, unidad de RF remota (RRU), cabezal de radio remoto (RRH), nodo de radio de radio multiestándar (MSR) tal como BS de MSR, nodos en sistema de antenas distribuido (DAS), O&M, OSS, SON, nodo de posicionamiento (por ejemplo, E-SMLC), MDT o cualquier otro nodo de red adecuado. Los nodos 115 de red pueden desplegarse por la totalidad de la red 100 como un despliegue homogéneo, un despliegue heterogéneo o un despliegue mixto. Un despliegue homogéneo puede describir generalmente un despliegue compuesto por el mismo tipo (o similar) de nodos 115 de red y/o tamaños de celda y cobertura y distancias entre sitios similares. Una implementación heterogénea puede describir generalmente despliegues que usan una variedad de tipos de nodos 115 de red que tienen diferentes tamaños de celda, potencias de transmisión, capacidades y distancias entre sitios. Por ejemplo, un despliegue heterogéneo puede incluir una pluralidad de nodos de baja potencia colocados por la totalidad de un diseño de macrocelda. Los despliegues mixtos pueden incluir una mezcla de partes homogéneas y partes heterogéneas.

El nodo 115 de red puede incluir uno o más del transceptor 1110, el conjunto 1120 de circuitos de procesamiento, la memoria 1130 y la interfaz 1140 de red. En algunas realizaciones, el transceptor 1110 facilita la transmisión de señales inalámbricas y la recepción de señales inalámbricas desde el dispositivo 110 inalámbrico (por ejemplo, a través de la antena 1150), el conjunto 1120 de circuitos de procesamiento ejecuta instrucciones para proporcionar parte o la totalidad de la funcionalidad descrita anteriormente como proporcionada por un nodo 115 de red, la memoria 1130 almacena las instrucciones ejecutadas por el conjunto 1120 de circuitos de procesamiento, y la interfaz 1140 de red comunica señales a los componentes de la red final, tal como una pasarela, un conmutador, enrutador, Internet, red telefónica pública conmutada (RTPC), nodos de red central o controladores 130 de red radioeléctrica, etc.

El conjunto 1120 de circuitos de procesamiento puede incluir cualquier combinación adecuada de hardware y software implementados en uno o más módulos para ejecutar instrucciones y manipular datos para realizar parte o la totalidad de las funciones descritas del nodo 115 de red, tales como las descritas anteriormente en relación con las figuras 1-9. En algunas realizaciones, el conjunto 1120 de circuitos de procesamiento puede incluir, por ejemplo, uno o más ordenadores, una o más unidades centrales de procesamiento (CPU), uno o más microprocesadores, una o más aplicaciones y/u otra lógica.

La memoria 1130 puede hacerse funcionar generalmente para almacenar instrucciones, tales como un programa

informático, software, una aplicación que incluye uno o más de lógica, reglas, algoritmos, código, tablas, etc. y/u otras instrucciones capaces de ejecutarse por el conjunto 1120 de circuitos de procesamiento. Los ejemplos de la memoria 1130 incluyen una memoria informática (por ejemplo, memoria de acceso aleatorio (RAM) o memoria de sólo lectura (ROM)), medios de almacenamiento masivo (por ejemplo, un disco duro), medios de almacenamiento extraíbles (por ejemplo, un disco compacto (CD) o un disco de vídeo digital (DVD)), y/o cualquier otro dispositivo de memoria volátil o no volátil, no transitoria, legible por ordenador y/o ejecutable por ordenador que almacene información.

5

10

15

20

35

40

45

60

65

En algunas realizaciones, la interfaz 1140 de red está acoplada de manera comunicativa al conjunto 1120 de circuitos de procesamiento y puede referirse a cualquier dispositivo adecuado que pueda hacerse funcionar para recibir la entrada para el nodo 115 de red, enviar la salida desde el nodo 115 de red, realizar el procesamiento adecuado de la entrada o salida o ambos, comunicarse con otros dispositivos, o cualquier combinación de los anteriores. La interfaz 1140 de red puede incluir el hardware apropiado (por ejemplo, puerto, módem, tarjeta de interfaz de red, etc.) y software, incluyendo capacidades de conversión de protocolo y procesamiento de datos, para comunicarse a través de una red.

Otras realizaciones del nodo 115 de red pueden incluir componentes adicionales más allá de los mostrados en la figura 11 que pueden ser responsables de proporcionar determinados aspectos de la funcionalidad del nodo de red radioeléctrica, incluyendo cualquiera de las funcionalidades descritas anteriormente y/o cualquier funcionalidad adicional (incluyendo cualquier funcionalidad necesaria para soportar las soluciones descritas anteriormente). Los diferentes tipos diversos de nodos de red pueden incluir componentes que tienen el mismo hardware físico pero configurados (por ejemplo, mediante programación) para soportar diferentes tecnologías de acceso radioeléctrico, o pueden representar componentes físicos parcial o totalmente diferentes.

La figura 12 es un diagrama de bloques de un ejemplo de controlador de red radioeléctrica o nodo 130 de red central, según determinadas realizaciones. Los ejemplos de nodos de red pueden incluir un centro de conmutación móvil (MSC), un nodo de soporte GPRS de servicio (SGSN), una entidad de gestión de movilidad (MME), un controlador de red radioeléctrica (RNC), un controlador de estación base (BSC), etc. El controlador de red radioeléctrica o el nodo 130 de red central incluye el conjunto 1220 de circuitos de procesamiento, la memoria 1230 y la interfaz 1240 de red. En algunas realizaciones, el conjunto 1220 de circuitos de procesamiento ejecuta instrucciones para proporcionar parte o la totalidad de la funcionalidad descrita anteriormente como proporcionada por el nodo de red, la memoria 1230 almacena las instrucciones ejecutadas por el conjunto 1220 de circuitos de procesamiento, y la interfaz 1240 de red comunica señales a cualquier nodo adecuado, tal como una pasarela, un conmutador, enrutador, Internet, una red telefónica pública conmutada (RTPC), nodos 115 de red, controladores de red radioeléctrica o nodos 130 de red central, etc.

El conjunto 1220 de circuitos de procesamiento puede incluir cualquier combinación adecuada de hardware y software implementados en uno o más módulos para ejecutar instrucciones y manipular datos para realizar parte o la totalidad de las funciones descritas del controlador de red radioeléctrica o nodo 130 de red central. En algunas realizaciones, el conjunto 1220 de circuitos de procesamiento puede incluir, por ejemplo, uno o más ordenadores, una o más unidades centrales de procesamiento (CPU), uno o más microprocesadores, una o más aplicaciones y/u otra lógica.

La memoria 1230 puede hacerse funcionar generalmente para almacenar instrucciones, tales como un programa informático, software, una aplicación que incluye uno o más de lógica, reglas, algoritmos, código, tablas, etc. y/u otras instrucciones capaces de ejecutarse por el conjunto 1220 de circuitos de procesamiento. Los ejemplos de memoria 1230 incluyen una memoria informática (por ejemplo, memoria de acceso aleatorio (RAM) o memoria de sólo lectura (ROM)), medios de almacenamiento masivo (por ejemplo, un disco duro), medios de almacenamiento extraíbles (por ejemplo, un disco compacto (CD) o un disco de vídeo digital (DVD)), y/o cualquier otro dispositivo de memoria volátil o no volátil, no transitoria, legible por ordenador y/o ejecutable por ordenador que almacene información.

En algunas realizaciones, la interfaz 1240 de red está acoplada de manera comunicativa al conjunto 1220 de circuitos de procesamiento y puede referirse a cualquier dispositivo adecuado que pueda hacerse funcionar para recibir la entrada para el nodo de red, enviar la salida desde el nodo de red, realizar el procesamiento adecuado de la entrada o salida o ambos, comunicarse con otros dispositivos, o cualquier combinación de los anteriores. La interfaz 1240 de red puede incluir el hardware apropiado (por ejemplo, puerto, módem, tarjeta de interfaz de red, etc.) y software, incluyendo capacidades de conversión de protocolo y procesamiento de datos, para comunicarse a través de una red.

Otras realizaciones del nodo de red pueden incluir componentes adicionales más allá de los mostrados en la figura 12 que pueden ser responsables de proporcionar determinados aspectos de la funcionalidad del nodo de red, incluyendo cualquiera de las funcionalidades descritas anteriormente y/o cualquier funcionalidad adicional (incluyendo cualquier funcionalidad necesaria para soportar la solución descrita anteriormente).

La figura 13 es un diagrama de bloques esquemático de un dispositivo inalámbrico a modo de ejemplo, según determinadas realizaciones. El dispositivo 110 inalámbrico puede incluir uno o más módulos. Por ejemplo, el dispositivo 110 inalámbrico puede incluir un módulo 1310 de determinación, un módulo 1320 de comunicación, un módulo 1330 de recepción, un módulo 1340 de entrada, un módulo 1350 de presentación visual y cualquier otro módulo adecuado. En algunas realizaciones, uno o más del módulo 1310 de determinación, el módulo 1320 de

comunicación, el módulo 1330 de recepción, el módulo 1340 de entrada, el módulo 1350 de presentación visual, o cualquier otro módulo adecuado pueden implementarse usando uno o más procesadores, tales como el conjunto 1020 de circuitos de procesamiento descrito anteriormente en relación con la figura 10. En determinadas realizaciones, las funciones de dos o más de los diversos módulos pueden combinarse en un único módulo. El dispositivo 110 inalámbrico puede realizar los métodos de adaptación de velocidad para los códigos LDPC descritos anteriormente en relación con las figuras 1-9.

El módulo 1310 de determinación puede realizar las funciones de procesamiento del dispositivo 110 inalámbrico. En determinadas realizaciones, el dispositivo 110 inalámbrico puede realizar las funciones del primer nodo descrito anteriormente en relación con las figuras 1-9. En tal situación, el módulo 1310 de determinación puede generar un vector de palabra de código codificando el conjunto de bits de información con un código de verificación de paridad de baja densidad, en el que el vector de palabra de código se compone de bits sistemáticos y bits de paridad. Como parte de la generación del vector de la palabra de código codificando el conjunto de bits de información, el módulo 1310 de determinación puede unir bits ficticios al conjunto de bits de información, comprendiendo los bits ficticios bits de valor conocido, para producir un vector de información, y codificar el vector de información. En determinadas realizaciones, el módulo 1310 de determinación puede perforar los bits ficticios unidos. Como parte de la perforación de los bits ficticios unidos, el módulo 1310 de determinación puede omitir la escritura de los bits ficticios unidos en la memoria intermedia circular. Como parte de la perforación de los bits ficticios unidos, el módulo 1310 de determinación puede omitir los bits ficticios unidos al leer los bits codificados de la memoria intermedia circular.

20

25

5

10

15

Como otro ejemplo, el módulo 1310 de determinación puede realizar una adaptación de velocidad basada en memoria intermedia circular en el vector de palabra de código generado para producir los bits codificados para la transmisión, en el que la adaptación de velocidad basada en memoria intermedia circular comprende perforar una primera pluralidad de bits sistemáticos. Como otro ejemplo, el módulo 1310 de determinación puede realizar una adaptación de velocidad basada en memoria intermedia circular en el vector de palabra de código generado para producir bits codificados para una retransmisión, en el que la adaptación de velocidad basada en memoria intermedia circular para la retransmisión comprende perforar la primera pluralidad de bits sistemáticos.

30

Como otro ejemplo, el módulo 1310 de determinación puede perforar la primera pluralidad de bits sistemáticos al omitir la escritura de la primera pluralidad de bits sistemáticos en una memoria intermedia circular. Como otro ejemplo, el módulo 1310 de determinación puede perforar la primera pluralidad de bits sistemáticos omitiendo la primera pluralidad de bits sistemáticos al leer los bits codificados de una memoria intermedia circular.

35

Como otro ejemplo, el módulo 1310 de determinación puede realizar una adaptación de velocidad basada en memoria intermedia circular en el vector de palabra de código generado leyendo los bits sistemáticos y los bits de paridad fuera de una memoria intermedia circular para producir el vector de transmisión para la transmisión por un canal inalámbrico. Al leer los bits sistemáticos y los bits de paridad fuera de la memoria intermedia circular para producir el vector de transmisión para la transmisión por el canal inalámbrico, el módulo 1310 de determinación puede repetir, si el número de bits del vector de transmisión es mayor que el número total de bits en la memoria intermedia circular, uno o más bits en la memoria intermedia circular iniciando un nuevo ciclo.

40

Como otro ejemplo, el módulo 1310 de determinación puede perforar un subconjunto de los bits sistemáticos escritos en la memoria intermedia circular en una primera transmisión por el canal inalámbrico, e incluir el subconjunto de los bits sistemáticos que se perforaron en una retransmisión por el canal inalámbrico. El módulo 1310 de determinación puede perforar bits a lo largo de columnas de tal manera que se perforen bits de manera uniforme de cada una de una pluralidad de filas y se mantenga una distribución de peso de la matriz de verificación de paridad en la memoria intermedia circular.

45

50

Como otro ejemplo, el módulo 1310 de determinación puede leer los bits sistemáticos y los bits de paridad de modo que se implemente un intercalador de canales como parte de realizar la adaptación de velocidad basada en memoria intermedia circular en el vector de palabra de código generado. Como otro ejemplo, el módulo 1310 de determinación puede leer los bits sistemáticos y los bits de paridad de modo que no se implemente ningún efecto de intercalación de

55

Como otro ejemplo, el módulo 1310 de determinación puede realizar una adaptación de velocidad basada en memoria intermedia circular en el vector de palabra de código generado escribiendo al menos una parte de los bits sistemáticos y los bits de paridad tal como se definen mediante la matriz de verificación de paridad en una memoria intermedia circular rectangular, comprendiendo la memoria intermedia circular rectangular una o más filas y una o más columnas.