# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

11) Número de publicación: 2 788 664

51 Int. Cl.:

**H03M 13/11** (2006.01) **H03M 13/03** (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

**T3**

(86) Fecha de presentación y número de la solicitud internacional: 25.08.2014 PCT/CN2014/085132

(87) Fecha y número de publicación internacional: 27.08.2015 WO15123979

96 Fecha de presentación y número de la solicitud europea: 25.08.2014 E 14882882 (5)

(97) Fecha y número de publicación de la concesión europea: 11.03.2020 EP 3110009

(54) Título: Procedimiento de codificación, procedimiento de descodificación, dispositivo de codificación y dispositivo de descodificación para códigos LDPC estructurados

(30) Prioridad:

21.02.2014 CN 201410061163

Fecha de publicación y mención en BOPI de la traducción de la patente: **22.10.2020**

(73) Titular/es:

ZTE CORPORATION (100.0%) ZTE Plaza, Keji Road South, Hi-Tech Industrial Park, Nanshan Shenzhen, Guangdong 518057, CN

(72) Inventor/es:

XU, JUN; LI, LIGUANG; YUAN, ZHIFENG; XU, JIN y TIAN, KAIBO

(74) Agente/Representante:

**UNGRÍA LÓPEZ, Javier**

## **DESCRIPCIÓN**

Procedimiento de codificación, procedimiento de descodificación, dispositivo de codificación y dispositivo de descodificación para códigos LDPC estructurados

#### Campo de la técnica

5

10

15

20

25

30

35

40

45

60

La presente invención se refiere a un sistema de comunicación digital y, más particularmente, a un procedimiento de codificación, procedimiento de descodificación, dispositivo de codificación y dispositivo de descodificación para LDPC estructurados.

#### Antecedentes de la técnica relacionada

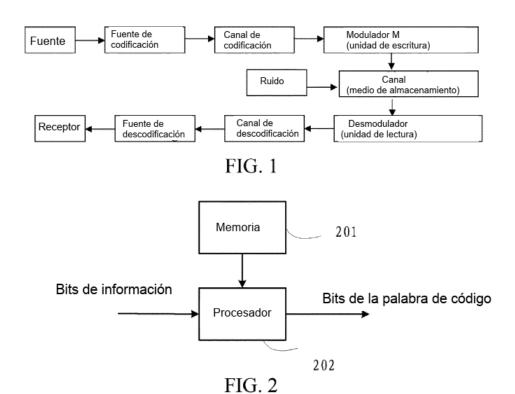

Con el desarrollo de la comunicación digital inalámbrica y el surgimiento de varios servicios con alta velocidad y ráfagas fuertes, cada vez hay más demanda de tecnología de codificación de corrección de errores propuesta por las personas. La figura 1 muestra un sistema de comunicación digital típico. Los códigos de comprobación de paridad de baja densidad (LDPC) son un tipo de código de bloque lineal que se puede definir mediante una matriz de comprobación de paridad muy dispersa o un gráfico bipartito. La LDPC fue descubierta inicialmente por Gallager y por ello se denomina códigos Gallager. Después de décadas de silencio, con el desarrollo de hardware informático y las teorías relativas, MacKay y Neal redescubrieron la LDPC y demostraron que la LDPC tiene un rendimiento cercano al límite de Shannon. La última investigación muestra que la LDPC tiene las siguientes ventajas: baja complejidad de descodificación, ser capaz de codificar en tiempo lineal, tener un rendimiento cercano al límite de Shannon, ser capaz de descodificar en paralelo y superior a los códigos Turbo en el escenario de códigos de gran tamaño.

Los códigos de LDPC son un tipo de códigos de bloque lineal basados en una matriz de comprobación de paridad dispersa y la codificación y descodificación de baja complejidad se logran simplemente utilizando la dispersidad de la matriz de comprobación de los códigos LDPC, haciendo que los códigos LDPC sean practicables. Los códigos irregulares se refieren a los códigos de comprobación de paridad de baja densidad donde un peso de la hilera y un peso de la columna de una matriz de comprobación de paridad son totalmente diferentes y los pesos de la columna de una porción de bits de información de la matriz de comprobación de paridad también son diferentes. Los códigos irregulares se refieren a códigos de comprobación de paridad de baja densidad donde un peso de la fila y un peso de la columna de una matriz de comprobación de paridad son totalmente iguales, o los códigos de comprobación de paridad de baja densidad donde un peso de la fila y un peso de la columna de una porción de bits de información son totalmente iguales en una matriz de comprobación de paridad cuando una porción de bits de comprobación mantiene, de forma correspondiente, una estructura constante. En la literatura relevante, los códigos de paridad de baja densidad del segundo caso de códigos regulares se denominan códigos semi-regulares. La distribución del

La LDPC es un tipo especial de código de bloque lineal. En comunicación, se necesitan M bits de comprobación para garantizar cierta capacidad de corrección cuando se envía una palabra de código con una longitud de bloque de N bits, cada palabra de código tiene que cumplir  $\mathbf{H}\mathbf{x}^T = \mathbf{0}^T$ , en el presente documento H es una matriz de comprobación de paridad dimensional MxN en un campo binario. Todas las operaciones se realizan en un campo binario GF(2) y la suma y la resta en el presente documento son operaciones "XOR", y la multiplicación es la operación "Y".

número de potencia de la matriz base y la distribución del número de potencia de la matriz de comprobación de

#### LDPC estructurada

paridad son consistentes.

Se supone que una matriz de comprobación de paridad H de los códigos LDPC estructurados es una matriz (*Mbxz*) *x* (*Nbxz*) compuesta por matrices de bloques *MbxNb*, cada matriz de bloque es una matriz de permutación de base *zxz* con un número de potencia diferente o una matriz nula de *zxz*. Cuando la matriz de permutación base es una matriz identidad, las matrices de los bloques son matrices de desplazamiento cíclico de la matriz identidad (el valor predeterminado es el desplazamiento a la derecha en el presente documento). Cada matriz de bloque se puede identificar de forma única a través del número de potencia j, el número de potencia de la matriz identidad puede representarse como 0 y el número de potencia de una matriz generalmente se representa como -1. Por lo tanto, si cada matriz de bloques de H se reemplaza por su número de potencia, se puede obtener una matriz Hb de potencia *MbxNb*. En este caso, Hb se define como la matriz base de H y H se llama matriz de expansión de Hb. En la codificación práctica, z = \frac{longitud de la palabra de código}{número de columna Nb de la matriz básica}, y z se llama factor de expansión.

Por ejemplo, la matriz

se puede obtener extendiendo una matriz base Hb 2x4 y el siguiente parámetro z: Z = 3 y

$H_{b-} \begin{bmatrix} 0 & 1 & 0 & -1 \\ 2 & 1 & 2 & 1 \end{bmatrix}$

Por lo tanto, un codificador LDPC de la presente invención puede generarse de manera única por la matriz base Hb, el factor de expansión z y la matriz de permutación base seleccionada. En resumen, cada elemento en la matriz base Hb corresponde a una matriz cuadrada z\*z de la matriz de comprobación de paridad. En particular, en la matriz base, cada elemento que toma el valor de -1 corresponde a una matriz cuadrada z\*z cero y cada elemento que toma el valor de no -1 corresponde a una matriz cuadrada z\*z no cero (es decir, la matriz identidad o las matrices de desplazamiento cíclico de la matriz identidad). De acuerdo con la definición anterior de la matriz identidad, se puede ver que bajo la condición de que se determina un factor de expansión (un número entero z mayor que 1) y la matriz base y la matriz de comprobación de paridad son de la misma naturaleza.

#### Codificación de LDPC

5

20

25

30

35

40

Un procedimiento de codificación directa de los códigos de bloque del sistema es: una palabra de código x se divide en bits de información N-M y bits c de comprobación M, de forma correspondiente, una matriz de comprobación de paridad MxN H se divide en dos bloques con tamaños de Mx(N-M) y MxM correspondientes a los bits de información y los bits de comprobación respectivamente, a saber H=[A|B]. De acuerdo con Hxx = 0, se puede tener:

$$[A \mid B] \times \left[\frac{s}{c}\right] = 0$$

A continuación, se puede tener  $A \times s + B \times c = 0$  y derivar además  $c = B^{-1}As$ . Cuando el bloque B usa una estructura matricial especial, tal como una estructura triangular estrictamente inferior (matriz semialeatoria), estructura triangular inferior doble, etc.,  $B^{-1}$  tiene una forma muy simple, la parte c del bit de comprobación en las palabras de código se puede calcular directamente de acuerdo con la fórmula anterior y se puede garantizar que el codificador tenga una complejidad lineal.

El algoritmo de codificación de tiempo lineal de Richarson también se puede aplicar, la matriz de comprobación de paridad H tiene una estructura triangular cuasi inferior, suponiendo que H tiene la siguiente forma:

$$\mathbf{H} = \begin{pmatrix} \mathbf{A} & \mathbf{B} & \mathbf{T} \\ \mathbf{C} & \mathbf{D} & \mathbf{E} \end{pmatrix}$$

Se supone que las palabras de código codificadas son  $\mathbf{x} = (\mathbf{s}, \mathbf{p}_1, \mathbf{p}_2)$ , en el presente documento, s es la parte de bit del sistema de las palabras de código codificadas,  $\mathbf{p}_1$  y  $\mathbf{p}_2$  son la parte del bit de comprobación de las palabras de código, la longitud de  $\mathbf{p}_1$  es g y la longitud de  $\mathbf{p}_2$  es (m-g). En la fórmula anterior, las dimensiones de A son (m-g)x(n-m), las dimensiones de B son (m-g)xg, las dimensiones de T son (m-g)x(m-g), las dimensiones de C son gx(n-m), las dimensiones de D son gxg y las dimensiones de E son gx (m-g). Todas estas matrices son matrices dispersas y T es una matriz triangular inferior de la cual todos los elementos diagonales son 1. La parte del bit de comprobación se puede obtener de la siguiente fórmula:

$$\mathbf{p}_{1}^{T} = -\mathbf{\phi}^{-1}(-\mathbf{E}\mathbf{T}^{-1}\mathbf{A} + \mathbf{C})\mathbf{s}^{T}$$

$$\mathbf{p}_{2}^{T} = -\mathbf{T}^{-1}(\mathbf{A}\mathbf{s}^{T} + \mathbf{B}\mathbf{p}_{1}^{T})$$

en el presente documento,

5

10

$$\phi = -ET^{-1}B + D$$

Por lo tanto, el codificador de los códigos LDPC diseñado por la presente invención puede ser generado de manera única por la matriz H de comprobación de paridad LDPC, que en realidad determina no solo el rendimiento del descodificador de código LDPC sino también la complejidad, el espacio de almacenamiento y el retraso de procesamiento del codificador y descodificador de los códigos LDPC. Por lo tanto, lo más importante es buscar una estructura de matriz de comprobación de paridad adecuada de los códigos LDPC.

En una implementación específica, una función de codificación para obtener una palabra de código de N bits de acuerdo con los datos de origen de los bits N-M puede realizarse calculando con el procedimiento directo anterior, el 15 procedimiento de Richarson u otros procedimientos. De hecho, el codificador usa software o hardware para implementar las operaciones de multiplicación y suma de la matriz dispersa en la fórmula. Para la LDPC basada en la matriz identidad y la matriz de desplazamiento cíclico de la matriz identidad, la operación de multiplicación de la matriz dispersa puede estar constituida por varios registros de desplazamiento cíclico con z bits (z es el factor de expansión) y varios sumadores con z bits, y la operación de adición de la matriz dispersa puede ser realizada por varios sumadores anteriores con z bits, y los varios registros de desplazamiento cíclico con z bits z y varios sumadores con z bits constituyen un codificador LDPC implementado por un circuito de hardware.

#### Descodificación de LDPC

25

30

20

Una presentación gráfica de una matriz de comprobación de paridad LDPC es un gráfico bipartito. El gráfico bipartito es una correspondencia de uno a uno con la matriz de comprobación, una matriz de comprobación de paridad MxN H define la restricción para cada palabra de código de N bits que cumplen los conjuntos de comprobación de paridad M. Un gráfico bipartito incluye N nodos variables y M nodos de comprobación de paridad. Cuando la comprobación emésima se refiere al enésimo bit, esto es, un elemento Hm en la emésima fila y la enésima columna de la H, cuando n es igual a 1, habrá una línea de conexión para conectar el nodo de comprobación m y el nodo variable n. No hay conexión entre nodos de ningún tipo en el gráfico bipartito y el número de aristas en el gráfico bipartito es igual al número de elementos distintos de cero en la matriz de comprobación.

- 35 El mensaje que pasa el algoritmo de descodificación de LDPC, también llamado algoritmo de propagación de creencias (BP), asume que los nodos variables son independientes unos de otros, sin embargo, la existencia del círculo corto inevitablemente rompe la asunción de la independencia, lo que obviamente disminuirá el rendimiento de descodificación. De hecho, cuanto más largo sea el círculo más corto del gráfico bipartito correspondiente a la matriz de comprobación de paridad LDPC, esto es, cuanto mayor es el valor de la circunferencia, menor sea la información 40 de retroalimentación positiva transmitida desde el nodo variable a sí misma y mejor será el rendimiento de descodificación. Existe una relación entre la circunferencia de la matriz de comprobación H y la matriz base Hb y las conclusiones relacionadas se pueden obtener mediante la validación del razonamiento matemático y la simulación por ordenador.

- 45 Corrección de la matriz base

Si no se puede usar una misma matriz base para cada factor de expansión diferente, un descodificador/codificador LDPC necesita almacenar una matriz base para cada longitud de código diferente, por tanto, es necesario almacenar una gran cantidad de matrices base cuando hay una pluralidad de longitudes de código, por lo tanto, se ocupará un gran espacio de almacenamiento o el circuito de hardware se complicará.

La corrección utiliza el factor de expansión de otra longitud de código para corregir los elementos no negativos en la matriz base Hb, y el valor del elemento corregido debe ser menor que el valor del factor de expansión debajo de la longitud del código. El algoritmo de corrección puede ser mod, escalado + truncado o escalado + redondeo, etc. Suponiendo que Pi, j es el elemento no negativo en la fila i<sup>ésima</sup> y la columna j<sup>ésima</sup> de la matriz base, y P'i, j son los elementos corregidos, hay: Para un algoritmo mod:

$$P'_{ij} \equiv P_{ij} \mod \frac{n}{N}$$

60

50

55

Para un algoritmo de escalado + truncado:

$$P'_{ij} = [P_{ij} \times \frac{n}{2304}]$$

Para un algoritmo de escalado + redondeo:

$$P'_{ij} = \text{Redondeo}(P_{ij} \times \frac{n}{2304})$$

- en el presente documento, N es el número de columnas de la matriz base, y n es la longitud del código de los códigos de comprobación de paridad de baja densidad que generarán la matriz de comprobación de paridad. Mod es una operación mod, [] es una operación de truncado y Redondeo es una operación de redondeo. En este caso, se supone que la mayor longitud de códigos es 2304.

- 10 Por ejemplo, para códigos de comprobación de paridad de baja densidad con una longitud de código de 1152 bits, se supone que algún elemento no negativo de la matriz base es 93, entonces el resultado corregido es:

Para un algoritmo mod:

$$93 \mod \frac{1152}{24} = 93 \mod 48 = 45$$

15

Para un algoritmo de escalado + truncado:

$$[93 \times \frac{1152}{2304}] = [46,5] = 46$$

20

Para un algoritmo de escalado + redondeo:

Redondeo (93

$$\times \frac{1152}{2304}$$

) = Redondeo (46,5) = 47

Si la descodificación en capas popular más reciente se utiliza para LDPC, La lectura-escritura de la información de la razón logarítmica de verosimilitud afecta seriamente a la disposición de la cola de LDPC. En particular, en la alta tasa de bits, para una estructura de LDPC ordinaria, el descodificador necesita procesar una fila de la matriz base antes de comenzar la siguiente etapa de una cola, que necesita un largo tiempo de espera y si una etapa de una cola es particularmente larga, la eficiencia del descodificador se verá seriamente reducida.

30

35

El documento US 2009/0282315 A1 desvela sistemas de codificación LDPC para una extensión de capa física basada en ondas milimétricas de 60 GHz. La codificación LDPC en cooperación con el entrelazado de subportadoras, en el contexto de multiplexación por división de frecuencia ortogonal y el mapeo de símbolos apropiado se realiza de acuerdo con el procesamiento de transmisión como se puede realizar dentro de un dispositivo de comunicación. En un dispositivo de comunicación receptor, el procesamiento de recepción puede realizarse en una señal recibida en función del tipo de LDPC, entrelazado de subportadoras y mapeo de símbolos de los mismos.

# Sumario de la invención

40

Las realizaciones de la presente invención proporcionan un procedimiento de codificación, procedimiento de descodificación, dispositivo de codificación y dispositivo de descodificación para LDPC estructurado como se define en las reivindicaciones 1-13, que resuelven el problema existente de baja eficiencia de un descodificador/codificador.

Una realización de la presente invención proporciona además un programa informático, incluidas las instrucciones del programa, que, cuando lo ejecuta un dispositivo de codificación, habilite el dispositivo de codificación para implementar el procedimiento de codificación como se especifica en las reivindicaciones 1-3.

Una realización de la presente invención proporciona además un programa informático, incluidas las instrucciones del programa, que, cuando es ejecutado por un dispositivo de descodificación, permitir que el dispositivo de descodificación implemente el procedimiento de descodificación de las reivindicaciones 4-7.

La realización de la presente invención proporciona además una portadora que lleva uno cualquiera de los programas informáticos anteriores.

55

60

Las realizaciones de la presente invención proporcionan un procedimiento de codificación, procedimiento de descodificación, dispositivo de codificación y dispositivo de descodificación para códigos de LDPC estructurados. Al determinar una matriz base, utilizada para descodificar o codificar, que incluye K0 pares adyacentes superiores e inferiores, de acuerdo con la matriz base y el factor de expansión correspondiente a la matriz base, se completa la descodificación o codificación, Se realiza la codificación y descodificación LDPC a la alta velocidad de canalización y se resuelve el problema existente de baja eficiencia de un descodificador/codificador.

## Breve descripción de los dibujos

La figura 1 es un diagrama de módulo de un sistema de comunicación digital;

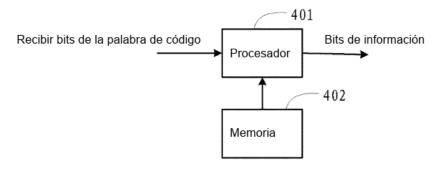

la figura 2 es un diagrama esquemático de una estructura de un codificador de códigos LDPC proporcionado en una primera realización de la presente invención;

5

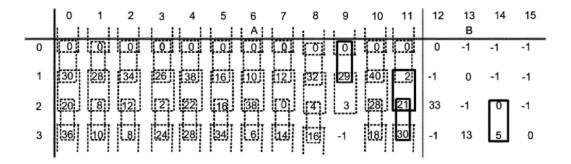

la figura 3 es un diagrama esquemático de una matriz base utilizada en la primera realización de la presente invención;

10

la figura 4 es un diagrama esquemático de una estructura de un descodificador de códigos LDPC proporcionado en una segunda realización de la presente invención;

la figura 5 es un diagrama esquemático de una matriz base utilizada en la segunda realización de la presente invención:

15

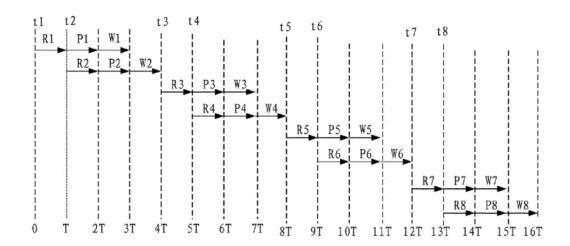

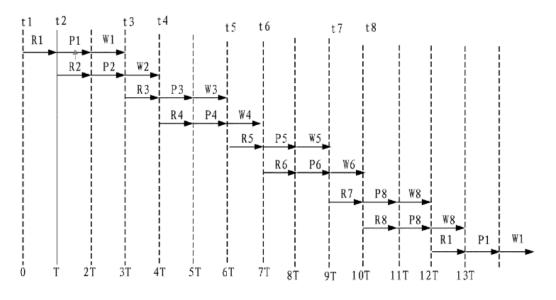

la figura 6 es un diagrama esquemático de una la cola de descodificación en capas convencional proporcionada en la segunda realización de la presente invención;

20

la figura 7 es un diagrama esquemático de una la cola de descodificación en capas de la presente invención proporcionada en la segunda realización de la presente invención;

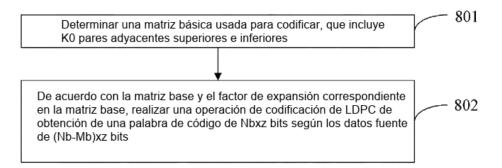

la figura 8 es un diagrama de flujo de un procedimiento de codificación para códigos LDPC estructurados proporcionado en una tercera realización de la presente invención;

25

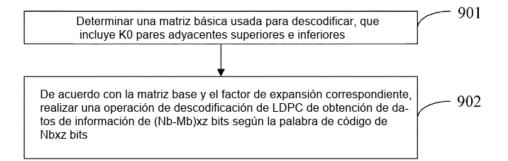

la figura 9 es un diagrama de flujo de un procedimiento de descodificación para códigos LDPC estructurados proporcionado en una cuarta realización de la presente invención;

la figura 10 es un diagrama esquemático de una estructura de un dispositivo de codificación para códigos LDPC estructurados proporcionados en una quinta realización de la presente invención; y

30

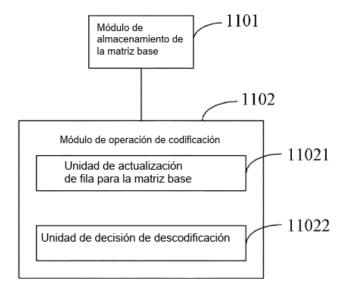

la figura 11 es un diagrama esquemático de una estructura de un dispositivo de descodificación para códigos LDPC estructurados proporcionados en la quinta realización de la presente invención.

# Realizaciones preferidas de la invención

35 Para una LDPC estructurada convencional, si se usa la descodificación en capas más popular recientemente, la lectura-escritura de la información de la razón logarítmica de verosimilitud afecta seriamente a la disposición de la cola de LDPC. En particular, en la alta tasa de bits, para una estructura de LDPC ordinaria, el descodificador necesita procesar una fila de la matriz base antes de comenzar la siguiente etapa de una cola. La eficiencia del descodificador se verá seriamente reducida si una etapa de una la cola es particularmente larga.

40

No obstante, el número de posibles patrones de combinación de matrices base es enorme y, en la técnica existente, no existe un procedimiento factible para reducir el tiempo de espera y no se obtiene una matriz base para satisfacer dicho requisito.

45 Con el fin de resolver el problema anterior, las realizaciones de la presente invención proporcionan un procedimiento de codificación, procedimiento de descodificación, dispositivo de codificación y dispositivo de descodificación para LDPC estructurados. En función de la practicabilidad, para varias longitudes de código diferentes con la misma velocidad de bits, las realizaciones de la presente invención usan la misma matriz base que generalmente se genera correspondiente al código más largo. Al mismo tiempo, la matriz base se corrige para diferentes longitudes de código, lo que hace que el descodificador/codificador generado sea adecuado para el caso de longitudes de código variables. Sin estar limitada a este punto, la presente invención también se aplica al caso de que cada longitud de código usa una matriz base.

50

55

En lo sucesivo, junto con los dibujos adjuntos, se describirán con detalle las realizaciones de la presente invención. Cabe señalar que en caso de no existir conflicto. las realizaciones en la presente invención y las características en las realizaciones pueden combinarse de forma arbitraria entre sí.

# Realización 1

- La realización de la presente invención proporciona un dispositivo de codificación para códigos de comprobación de 60 paridad de baja densidad (LDPC) estructurados en comunicación digital, cuya estructura se muestra en la figura 2, que incluye, al menos, un procesador 202 y una memoria 201.

- La memoria 201 está configurada para, al menos, almacenar una matriz base que se usa para codificar e incluye K0 65 pares adyacentes superiores e inferiores y parámetros.

Para cada matriz base  $H_b$ , si el número de diferentes K0 pares adyacentes superiores e inferiores, hay K1 pares adyacentes superiores e inferiores de un primer tipo y K2 pares adyacentes superiores e inferiores de un segundo tipo, en el presente documento K0 = K1 + K2, K0 es un número entero positivo mayor o igual a 6\*Mb, y K2 es un número entero positivo mayor o igual a 0\*Mb, y K2 es un número entero positivo mayor o igual a 0\*Mb, y K2 es un número entero positivo mayor o igual a 0\*Mb, y K2 es un número entero positivo mayor o igual a 0\*Mb, y K2 es un número entero positivo mayor o igual a 0\*Mb, y K2 es un número entero positivo mayor o igual a 0\*Mb, y K2 es un número entero positivo mayor o igual a 0\*Mb, y K2 es un número entero positivo mayor o igual a 0\*Mb, y K2 es un número entero positivo mayor o igual a 0\*Mb, y K2 es un número entero positivo mayor o igual a 0\*Mb, y K2 es un número entero positivo mayor o igual a 0\*Mb, y K2 es un número entero positivo mayor o igual a 0\*Mb, y K2 es un número entero positivo mayor o igual a 0\*Mb, y K2 es un número entero positivo mayor o igual a 0\*Mb, y K2 es un número entero positivo mayor o igual a 0\*Mb, y K2 es un número entero positivo mayor o igual a 0\*Mb, y K2 es un número entero positivo mayor o igual a 0\*Mb, y K2 es un número entero positivo mayor o igual a 0\*Mb, y K2 es un número entero positivo mayor o igual a 0\*Mb, y K2 es un número entero positivo mayor o igual a 0\*Mb, y K2 es un número entero positivo mayor o igual a 0\*Mb, y K2 es un número entero positivo mayor o igual a 0\*Mb, y K2 es un número entero positivo mayor o igual a 0\*Mb, y K2 es un número entero positivo mayor o igual a 0\*Mb, y K2 es un número entero positivo mayor o igual a 0\*Mb, y K2 es un número entero positivo mayor o igual a 0\*Mb, y K2 es un número entero positivo mayor o igual a 0\*Mb, y K2 es un número entero positivo mayor o igual a 0\*Mb, y K2 es un número entero positivo mayor o igual a 0\*Mb, y K2 es un número entero positivo m

Preferentemente, si K2 es mayor o igual a 3, para dos filas cualquiera adyacentes (la fila x1ª y la fila ((x1 + 1) mod Mb)<sup>ésima</sup>), el número de pares adyacentes del segundo tipo es como máximo 3, en el presente documento x1 y x2 toman el valor de 0 a Mb-1.

- En el presente documento, el par adyacente superior e inferior se define como un conjunto constituido por dos elementos {hbij, hb((i + i)mod Mb)j}} correspondiente a matrices cuadradas no nulas en cada matriz base Hb, esto es, un conjunto constituido por dos elementos adyacentes que corresponden a matrices cuadradas no nulas en alguna columna de una matriz base, en el presente documento, la última fila y la primera fila se definen como adyacentes, y la última fila se define como una fila anterior de la primera fila. Los pares adyacentes superiores e inferiores del primer tipo se definen como pares adyacentes superiores e inferiores que son congruentes con(hbij-hb((i++1)mod Mb)j) mod Q = a y los pares adyacentes superiores e inferiores del segundo tipo se definen como pares adyacentes superiores e inferiores del segundo tipo se definen como pares adyacentes superiores e inferiores del segundo tipo se definen como pares adyacentes superiores e inferiores del segundo tipo se definen como pares adyacentes

- El número total de elementos que corresponden a las matrices cuadradas no nulas en la columna j<sup>ésima</sup> de la matriz base Hb es L<sub>j</sub>, el primer elemento de arriba a abajo es 0, L<sub>j</sub> es un número entero positivo mayor o igual a 1, y j = 0, 1, ..., Nb-1. Debe observarse que la presente invención no se limita a tal manera. El último elemento también puede ser 0 o cualquier elemento también puede ser 0. De esta manera se garantiza que si se utiliza la descodificación en capas, no se puede usar una red inversa de desplazamiento cíclico, una sobrecarga de enrutamiento puede reducirse considerablemente y se obtiene un efecto beneficioso.

- El procesador 202 está configurado para determinar la matriz base y un factor de expansión z, y realizar una operación de codificación LDPC para obtener una palabra de código de Nbxz bits de acuerdo con los datos de origen de (Nb-Mb) × z bits.

- En el presente documento, hb<sub>ij</sub> representa un elemento en la fila i<sup>ésima</sup> y la columna j<sup>ésima</sup> de una matriz base, en el presente documento, a y b no son iguales, a y b son números enteros mayores o iguales a 0 y menores o iguales a Q-1, Q es un factor de multiplicación del factor de expansión z, el peso de la columna de la j<sup>ésima</sup> columna se refiere al número total de elementos correspondientes a matrices cuadradas no nulas en la j<sup>ésima</sup> columna de la H<sub>b</sub>, i es un índice de fila de la H<sub>b</sub>, j es un índice de columna de la H<sub>b</sub>, i = 0, 1, ..., Mb-1, j=0, 1, ..., Nb-1, z es el factor de expansión y z es un número entero positivo mayor o igual a 1.

Preferentemente, el valor de K2 generalmente toma cualquiera de los siguientes: 1, 2, 3, ... y 12.

25

55

60

El valor de Q = 2 y, para ejemplos que no forman parte de la invención, Q toma cualquiera de los siguientes: 3, 4, 5, 40 6, 7 y 8.

Lo siguiente describe una realización más específica. Una matriz base H<sub>b</sub>, como se muestra en la figura 3, cumple los requisitos anteriores.

- Para la matriz base mostrada en la figura 3, se establecen parámetros, tales como, la tasa de bits correspondiente a la matriz es 3/4, el número de filas de la matriz es Mb = 4, el número de columnas de la matriz es Nb = 16, Q = 2, K2 = 4, K0 = 47, K1 = 43, a = 0, d = 1. La matriz base corresponde al factor de expansión z = 42. El factor de expansión z = 42 = 2\*3\*7, por lo tanto, Q = 2 satisface el requisito de que Q es el factor de multiplicación del factor de expansión z.

- Para la matriz base  $H_b$  mostrada en la figura 3, si el número de diferentes K0 pares adyacentes superiores e inferiores = 47, hay K1 = 43 pares adyacentes superiores e inferiores del primer tipo y K2 = 3 pares adyacentes superiores e inferiores del segundo tipo. Los siguientes aparentemente se satisfacen: K0=K1+K2, K0 es un número entero positivo mayor que 24 y K2 es un número entero positivo mayor que 8.

- En el presente documento, los pares adyacentes superiores e inferiores del primer tipo se definen como pares adyacentes superiores e inferiores con  $(hb_{ij}-hb_{((i+1) \mod Mb)j})$  mod Q=0, como se muestra mediante un recuadro de línea discontinua en la figura 3, en el presente documento, un recuadro abierto de línea discontinua superior y un recuadro abierto de línea discontinua inferior de una columna constituyen un recuadro completo de línea discontinua. Los pares adyacentes superiores e inferiores del segundo tipo se definen como pares adyacentes superiores e inferiores con  $(hb_{ij}-hb_{((i+1) \mod Mb)j})$  mod Q=1, como se muestra mediante un recuadro de línea continua en la figura 3.

- En la matriz dada anteriormente, en la parte superior están los índices de columna, a la izquierda están los índices de fila, la parte A de la matriz es una parte sistemática de bits de la matriz, la parte B es una parte de bits de comprobación de la matriz. Los elementos, que toman el valor de -1 en la matriz, corresponden a matrices cuadradas nulas de zxz. Los elementos, que toman el valor de no -1, corresponden a matrices cuadradas no nulas

de zxz y las matrices cuadradas no nulas son matrices obtenidas desplazando cíclicamente la matriz identidad por el valor correspondiente.

De acuerdo con las características descritas, los pares adyacentes superiores e inferiores son un conjunto constituido por dos elementos adyacentes, correspondiente a matrices cuadradas no nulas, en alguna columna de una matriz base, específicamente como los 2 elementos que se muestran en el recuadro rectangular de la figura. El recuadro de línea discontinua representa pares adyacentes superiores e inferiores del primer tipo y, de forma correspondiente, a = 0. El recuadro de línea continua representa pares adyacentes superiores e inferiores del segundo tipo, y, de forma correspondiente, d = 1.

10

15

Se puede ver que hay 4 pares adyacentes superiores e inferiores del segundo tipo. En la matriz de paridad base anterior, para dos filas adyacentes, no hay más de 2 pares adyacentes superiores e inferiores del segundo tipo. Por ejemplo, para las filas 0ª y 1ª, solo hay un par adyacente superior e inferior del segundo tipo; para las filas 1ª y 2ª, solo hay un par adyacente superior e inferior del segundo tipo; para las filas 2ª y 3ª, hay dos pares adyacentes superiores e inferiores del segundo tipo; para las filas 3ª y 0°, no hay un par adyacente superior e inferior del segundo tipo.

20

Además, el primer elemento correspondiente a una matriz cuadrada distinta de cero en cada una de las columnas de la matriz base Hb es 0. En este caso, la red de desplazamiento cíclico solo necesita completar las diferencias de desplazamiento cíclico. Por ejemplo, para la primera columna, la red de desplazamiento cíclico solo necesita implementar desplazamientos de 30-0, 20-30, 36-20 y 0-36. Después de completar una iteración completa de LDPC, la información de una razón logarítmica de verosimilitud correspondiente a la primera matriz base se devuelve a una posición secuencial y se puede tomar una decisión firme, y, si es correcta, se envía a la salida y, si es incorrecta, la iteración continúa. En este caso, un descodificador en capas LDPC con la estructura matricial de la realización de la presente invención, no necesita la red inversa de desplazamiento cíclico. En comparación con las soluciones convencionales, el recorrido se reduce a la mitad.

25

30

Preferentemente, el codificador también tiene las siguientes características: el codificador incluye además un módulo de expansión, configurado para realizar una expansión en la matriz base de acuerdo con el factor de expansión y una matriz de permutación base para obtener una matriz de comprobación de paridad de los códigos de comprobación de paridad de baja densidad (Mxz) x (Nxz). El módulo de operación de descodificación realiza una operación de codificación basada en la matriz de comprobación de paridad obtenida por la expansión de la matriz

40

35

En la realización de la presente invención, se realiza una codificación LDPC en un bit de información a través de una estructura propuesta de la matriz base, que puede generar una palabra de código LDPC. Esta palabra de código LDPC se envía a un canal a través de módulos de modulación, etc. Después de recibir una señal, un extremo receptor realiza un procesamiento tal como desmodulación, etc., y genera una palabra de código LDPC recibida. La palabra de código LDPC recibida se envía a un descodificador LDPC. Por dicha palabra de código LDPC, se garantiza que la velocidad de la cola del descodificador alcanza el efecto de verse elevada, esto es, la velocidad de la cola del descodificador alcanza el efecto de verse elevada. Esto aumenta de forma eficaz la eficiencia de LDPC y acelera la velocidad de descodificación. Permitiendo no usar la red de desplazamiento cíclico inverso (para escribir una memoria), la estructura de la matriz base propuesta por la realización de la presente invención también puede reducir las redes de conmutación y reduce aún más la complejidad del hardware.

45

50

#### Realización 2

La realización de la presente invención proporciona un dispositivo de descodificación para códigos estructurados de comprobación de paridad de baja densidad (LDPC) en comunicación digital, cuya estructura se muestra en la figura 4, que incluye, al menos, un procesador 402 y una memoria 401.

La memoria 401 está configurada para, al menos, almacenar una matriz base que incluye K0 pares adyacentes superiores e inferiores y parámetros. La matriz base incluye las siguientes características:

Para cada matriz base H<sub>b</sub>, si el número de diferentes K0 pares adyacentes superiores e inferiores, hay K1 pares adyacentes superiores e inferiores de un primer tipo y K2 pares adyacentes superiores e inferiores de un segundo 55 tipo, en el presente documento K0 = K1 + K2, K0 es un número entero positivo mayor o igual a 6\*Mb, y K2 es un número entero positivo mayor o igual a 1 y menor o igual a 2\*Mb.

60

65

Preferentemente, si K2 es mayor o igual a 3, para dos filas cualquiera adyacentes (la fila x1ª y la fila ((x1 + 1) mod Mb) es número de pares adyacentes del segundo tipo es como máximo 3, en el presente documento x1 y x2 toman el valor de 0 a Mb-1.

El par adyacente superior e inferior se define como un conjunto constituido por dos elementos {hb<sub>ii</sub>, hb<sub>(ii + i)mod Mb)}}</sub> correspondiente a matrices cuadradas no nulas en cada matriz base H<sub>b</sub>, esto es, un conjunto constituido por dos elementos advacentes que corresponden a matrices cuadradas no nulas en alguna columna de una matriz base, en el presente documento, la última fila y la primera fila se definen como filas adyacentes, y la última fila se define como

una fila anterior de la primera fila. Los pares adyacentes superiores e inferiores del primer tipo se definen como pares adyacentes superiores e inferiores que son congruentes con (hb<sub>ii</sub>-hb<sub>((i++1)mod Mb))</sub>) mod Q = a y los pares adyacentes superiores e inferiores del segundo tipo se definen como pares adyacentes superiores e inferiores que son congruentes con  $(hb_{ij}-hb_{((i+1)mod\ Mb)j})\ mod\ Q=d.$

El número total de elementos que corresponden a las matrices cuadradas no nulas en la columna j<sup>ésima</sup> de la matriz base Hb es L<sub>i</sub>, el primer elemento de arriba a abajo es 0, L<sub>i</sub> es un número entero positivo mayor o igual a 1, y j = 0, 1, ..., Nb-1.

10

El procesador 402 está configurado para, de acuerdo con la matriz base y el factor de expansión correspondiente z, realizar una operación de descodificación LDPC para obtener los datos de información de (Nb-Mb)xz bits de acuerdo con la palabra de código de Nbxz bits.

15

En el presente documento,  $hb_{ij}$  representa un elemento en la fila  $i^{\acute{e}sima}$  y la columna  $j^{\acute{e}sima}$  de una matriz base, en el presente documento, a y d no son iguales, a y d son números enteros entre 0 y Q-1, Q es un factor de multiplicación del factor de expansión z. El peso de la columna de la  $j^{\text{ésima}}$  columna se refiere al número total de elementos correspondientes a matrices cuadradas no nulas en la  $j^{\text{ésima}}$  columna de la  $H_b$ , i es un índice de fila de la  $H_b$ , j es un índice de columna de la  $H_b$ , i = 0, 1, ..., Mb-1, j=0, 1, ..., Nb-1, z es el factor de expansión y z es un número entero positivo mayor o igual a 1.

20

Preferentemente, el valor de K2 generalmente toma uno de los siguientes: 1, 2, 3, ... y 12.

El valor de Q = 2 y, para ejemplos que no forman parte de la invención, Q toma uno de los siguientes: 3, 4, 5, 6, 7 y

25

Lo siguiente describe una realización más específica. Una matriz base H<sub>b</sub>, como se muestra en la figura 5, cumple con el requisito anterior.

30

35

Para la matriz base mostrada en la figura 5, se establecen parámetros, tales como, la tasa de bits correspondiente a la matriz es 3/4, el número de filas de la matriz es Mb = 4, el número de columnas de la matriz es Nb = 16, Q = 2, K2 = 4, K0 = 47, K1 = 43, a = 0, d = 1. La matriz base corresponde al factor de expansión z = 42. Para el factor de expansión z=42=2\*3\*7, por lo tanto, Q = 2 satisface el requisito de que Q es el factor de multiplicación del factor de

expansión z.

Para la matriz base H<sub>b</sub> mostrada en la figura 5, si el número de diferentes K0 pares adyacentes superiores e inferiores = 47, hay K1 = 43 pares adyacentes superiores e inferiores del primer tipo y K2 = 3 pares adyacentes superiores e inferiores del segundo tipo. Los siguientes aparentemente se satisfacen: K0=K1+K2, K0 es un número entero positivo mayor que 24 y K2 es un número entero positivo mayor que 8.

40

En el presente documento, los pares adyacentes superiores e inferiores del primer tipo se definen como pares adyacentes superiores e inferiores que son (hb<sub>ij</sub>-hb<sub>((j+1)mod Mb)j</sub>) mod Q = 0, como se muestra mediante un recuadro de línea discontinua en la figura donde un recuadro abierto de línea discontnua superior y un recuadro abierto de línea discontinua inferior de una columna constituyen un recuadro completo de línea discontinua. Los pares adyacentes superiores e inferiores del segundo tipo se definen como pares adyacentes superiores e inferiores que son (hb<sub>ii</sub>-

45

hb<sub>((i+1) mod Mb)i</sub>) mod 2 = 1, como se muestra mediante un recuadro de línea continua en la figura 5.

En la matriz dada anteriormente, en la parte superior están los índices de columna, a la izquierda están los índices 50

de fila, la parte A de la matriz es una parte sistemática de bits de la matriz, la parte B es una parte de bits de comprobación de la matriz. Los elementos, que toman el valor de -1 en la matriz, corresponden a matrices cuadradas nulas de zxz. Los elementos, que toman el valor de no -1, corresponden a matrices cuadradas no nulas de zxz y las matrices no nulas son matrices obtenidas mediante desplazamiento cíclico de la matriz identidad por el

valor correspondiente.

55

De acuerdo con las características descritas, los pares adyacentes superiores e inferiores son un conjunto constituido por dos elementos adyacentes que corresponden a matrices cuadradas no nulas en alguna columna de una matriz base, específicamente como 2 elementos mostrados en el recuadro rectangular en la figura 5. El recuadro de línea discontinua representa pares adyacentes superiores e inferiores del primer tipo y, de forma correspondiente, a = 0. El recuadro de línea continua representa pares adyacentes superiores e inferiores del segundo tipo, y, de forma correspondiente, d = 1.

60

65

Se puede ver que hay 4 pares adyacentes superiores e inferiores del segundo tipo. En la matriz de paridad base anterior, para dos filas adyacentes, no hay más de 2 pares adyacentes superiores e inferiores del segundo tipo. Por ejemplo, para las filas 0<sup>a</sup> y 1<sup>a</sup>, solo hay un par adyacente superior e inferior del segundo tipo; para las filas 1<sup>a</sup> y 2<sup>a</sup>, solo hay un par adyacente superior e inferior del segundo tipo; para las filas 2ª y 3ª, hay dos pares adyacentes superiores e inferiores del segundo tipo; para las filas 3ª y 0º, no hay un par adyacente superior e inferior del

segundo tipo.

Además, el primer elemento correspondiente a una matriz cuadrada distinta de cero en cada una de las columnas de la matriz base Hb es 0. En este caso, la red de desplazamiento cíclico solo necesita completar las diferencias de desplazamiento cíclico. Por ejemplo, para la primera columna, la red de desplazamiento cíclico solo necesita implementar desplazamientos de 30-0, 20-30, 36-20 y 0-36. Después de completar una iteración completa de LDPC, la información de una razón logarítmica de verosimilitud correspondiente a la primera matriz base se devuelve a una posición secuencial y se puede tomar una decisión firme, y, si es correcta, se envía a la salida y, si es incorrecta, la iteración continúa. En este caso, un descodificador en capas LDPC con la estructura matricial de la realización de la presente invención, no requiere la red inversa de desplazamiento cíclico. En comparación con las soluciones convencionales, el recorrido se reduce a la mitad. Adicionalmente, el procesador usa un algoritmo de propagación de creencias (BP) en capas y un algoritmo min-sum corregido para la descodificación para realizar una actualización de fila en la matriz base. En una iteración de número impar, además de actualizar la información extrínseca correspondiente a un elemento que no sean pares adyacentes del segundo tipo, el procesador solo actualiza la información extrínseca (nodo de comprobación de la información del nodo variable) correspondiente a un elemento en cada par adyacente del segundo tipo. En una iteración de número par, además de actualizar la información extrínseca correspondiente a elementos que no sean pares adyacentes del segundo tipo, el procesador solo actualiza la información extrínseca (nodo de comprobación de la información del nodo variable) correspondiente a otro elemento en cada par advacente del segundo tipo.

10

15

25

30

35

60

65

20 Lo siguiente ilustra los efectos beneficiosos de la descodificación que son causados por la estructura del código de la presente realización de la invención.

Si el grado de paralelismo del descodificador es paralelo = 21, y para una secuencia de bits de palabra de código, hay una memoria de razón logarítmica de verosimilitud (LLR) para cada zf = 42 bits, entonces hay 16 memorias LLR y cada memoria corresponde a una columna de una matriz base. Cada memoria LLR incluye número de palabra = zf/paralelo = 2 palabras, una palabra almacena bits impares entre 42 bits correspondientes a una columna de la matriz base y otra palabra almacena bits pares. En el presente documento, Zf es el factor de expansión.

Durante la descodificación del descodificador, para el número de capa de cada capa (de 0 al nivel máximo permitido por la descodificación), se seleccionan y actualizan 21 filas de la matriz de comprobación de paridad H de acuerdo con la siguiente fórmula:

índice de fila = índice de fila Hb\*zf + mod(mod número de capa, número de palabra:número de palabra:(índice de fila Hb+1)\*zf-1;

en el presente documento, mod número de capa = mod(número de capa,total de capas), índice de filaHb = fijo(mod número de capa \* paralelo/zf); Total de capas = Mb\*zf/paralelo = 8.

A un primer tiempo t0, el descodificador en capas realiza una actualización de fila en las filas 0, 2, ... y 40, y 40 completa la descodificación en capas de la primera capa; a un segundo tiempo t1, el descodificador realiza una actualización de fila en las filas 1, 3, ... y 41, y completa la descodificación en capas de la segunda capa; a un tercer tiempo t2, el descodificador realiza una actualización de fila en las filas 42, 44, ... y 82, y completa la descodificación en capas de la tercera capa; a un cuarto tiempo t3, el descodificador realiza una actualización de fila en las filas 43, 45, ... y 83, y completa la descodificación en capas de la cuarta capa; a un quinto tiempo t4, el descodificador realiza 45 una actualización de fila en las filas 84, 86, ... y 124, y completa la descodificación en capas de la quinta capa; a un sexto tiempo t5, el descodificador realiza una actualización de fila en las filas 85, 87, ... y 125, y completa la descodificación en capas de la sexta capa; a un séptimo tiempo t6, el descodificador realiza una actualización de fila en las filas 126, 128, ... y 166, y completa la descodificación en capas de la séptima capa; a un octavo tiempo t7, el descodificador realiza una actualización de fila en las filas 127, 129, ... y 167, y completa la descodificación en capas 50 de la octava capa. Por lo tanto, se completa una descodificación completa de los códigos LDPC. Si no hay convergencia, el proceso anterior se continúa repitiendo hasta que la descodificación tenga éxito o hasta que la descodificación falle y alcance el número máximo permitido.

Para un descodificador convencional, es necesario esperar a que la cola de descodificación de la segunda capa se 55 implemente completamente antes de comenzar la descodificación en capas de la tercera capa, hay un largo tiempo de espera. De manera similar, es necesario esperar a que la descodificación de la cola de la cuarta capa se implemente completamente antes de comenzar la descodificación en capas de la quinta capa, hay un largo tiempo de espera. De manera similar, es necesario esperar a que la cola de descodificación de la sexta capa se implemente completamente antes de comenzar la descodificación en capas de la séptima capa, hay un largo tiempo de espera. De manera similar, es necesario esperar a que la cola de descodificación de la sexta capa se implemente completamente antes de comenzar la descodificación en capas de la séptima capa, hay un largo tiempo de espera. Por analogía, el tiempo de espera genera un gran retraso en la cola de LDPC, lo que reduce en gran medida la velocidad de la descodificación de los códigos LDPC en capas. Como se muestra en la figura 6, suponiendo que, para cada capa LDPC, se usa un reloj para leer, un reloj para procesar y un reloj para escribir, y cada reloj ocupa un tiempo de T, entonces una descodificación LDPC completa necesita un tiempo de 16\*T.

Dado que el diseño de los autores evita que la palabra utilizada en una última canalización debe ser diferente de la palabra utilizada en una la cola siguiente al cruzar capas. Adicionalmente, se usa un proceso de tiempo compartido para una pequeña cantidad de colisión. Como se muestra en la figura 7, solo se necesita un tiempo de 13\*T. De hecho, como un todo, se puede ahorrar un tiempo de 4\*T para el tiempo de cada 16\*T durante la descodificación LDPC.

En la realización de la presente invención, el grado de paralelismo se puede seleccionar para que sea 7 y hay 6 palabras. Si las palabras impares se procesan primero y las palabras pares se procesan después, se realiza una disposición similar a la de la figura 4 y la figura 5. Como un todo, la LDPC necesita un tiempo de 32\*T y usando la descodificación de la presente invención, se puede ahorrar un tiempo de 12\*T. El efecto es más obvio.

En la realización de la presente invención, el grado de paralelismo se puede expandir a 42, se puede realizar una descodificación simultánea en las filas 0, 2, ..., 40, y las filas 42, 44, ..., 82, ya que estas filas requieren datos con la misma dirección. Además, la cola se puede organizar aún más, lo que no es un algoritmo de descodificación en capas simple, pero ahorra tiempo más obviamente.

En la realización de la presente invención, el grado de paralelismo se puede expandir a 84, se puede realizar una descodificación simultánea en las filas 0, 2, ..., 40, las filas 42, 44, ..., 82, las filas 84, 86, ..., 124, y las filas 126, 128, ..., 166, ya que estas filas requieren datos con la misma dirección. Además, la cola se puede organizar más, lo que no es un algoritmo de descodificación en capas simple, pero ahorra tiempo más obviamente.

Por lo tanto, la estructura en la realización de la presente invención puede soportar un paralelismo muy alto o relativamente flexible que satisfaga el requisito de descodificación de una velocidad súperalta, alcanzando así la velocidad de descodificación Gbps. En la realización, usando la estructura propuesta de la matriz base, se realiza la descodificación LDPC en los bits de información y el descodificador LDPC recibe la palabra de código LDPC. De este modo, el descodificador LDPC puede asegurar que se obtiene el efecto de que la velocidad de la cola de la descodificación se eleva, esto es, se consigue el efecto de que la velocidad de procesamiento del descodificador se eleva. La eficiencia de los códigos LDPC aumenta de forma eficaz y la velocidad de descodificación se acelera. Permitiendo no usar la red de desplazamiento cíclico inverso (para escribir una memoria), la estructura de la matriz base propuesta por la realización de la presente invención también puede reducir las redes de conmutación y asimismo reducir aún más la complejidad del hardware.

#### Realización 3

10

15

20

25

30

45

65

35 La realización de la presente invención proporciona un procedimiento de codificación para códigos LDPC estructurados y el proceso de codificación LDPC que se completa usando el procedimiento de codificación, es como se muestra en la figura 8. El procedimiento incluye las etapas siguientes.

En la etapa 801, es determinar una matriz base utilizada para codificar, que incluye K0 pares adyacentes superiores e inferiores.

En esta etapa, la matriz base incluye un bloque A de Mbx (Nb-Mb) correspondiente a bits sistemáticos y un bloque B de MbxMb correspondiente a bits de comprobación. La matriz base incluye K1 pares adyacentes superiores e inferiores de un primer tipo y K2 pares adyacentes superiores e inferiores de un segundo tipo, en el presente documento K0 = K1 + K2, K0 es un número entero positivo mayor o igual a 6\* Mb, K2 es un entero positivo mayor o igual a 0 y menor o igual a 2\*Mb. Los pares adyacentes superiores e inferiores son un conjunto constituido por dos elementos {hb<sub>ii</sub>, hb<sub>((i+1) mod Mb)}</sub> correspondiente a matrices cuadradas no nulas en cada matriz base.

Los pares adyacentes superiores e inferiores del primer tipo son pares adyacentes superiores e inferiores que son congruentes con  $((hb_{ij}-hb_{((i+1)mod\ Mb)j}))$  mod Q = a.

Los pares adyacentes superiores e inferiores del segundo tipo son pares adyacentes superiores e inferiores que son congruentes con  $(hb_{ij}-hb_{((i+1)mod\ Mb)j})$  mod Q = d.

En el presente documento, hb<sub>ij</sub> representa un elemento en la fila i<sup>ésima</sup> y la columna j<sup>ésima</sup> de la matriz base, en el presente documento, a y d no son iguales, a y d son números enteros mayores o iguales a 0 y menores o iguales a Q-1, Q es un factor de multiplicación de un factor de expansión z, un peso de la columna de la j<sup>ésima</sup> columna se refiere al número total de elementos correspondientes a matrices cuadradas no nulas en la j<sup>ésima</sup> columna de la matriz base, i es un índice de fila de la matriz base, j es un índice de columna de la matriz base, i = 0, 1, ..., Mb-1, j=0, 1, ..., Nb-1.

Si K2 es mayor o igual a 3, para dos filas cualquiera adyacentes (la fila  $x1^a$  y la fila  $((x1 + 1) \text{ mod Mb})^{\text{ésima}})$ , el número de pares adyacentes del segundo tipo es como máximo 3, en el presente documento, el índice de fila x1 toma el valor de 0 a Mb-1.

El valor de Q = 2 y, para ejemplos que no forman parte de la invención, Q toma cualquiera de los siguientes: 3, 4, 5,

11

6, 7 y 8.

El número total de elementos que corresponden a las matrices cuadradas no nulas en la columna jésima de la matriz base es Lj, el primer elemento de arriba a abajo es 0,  $L_j$  es un número entero positivo mayor o igual a 1, y j = 0, 1, ..., Nb-1.

El valor de K0 toma cualquiera de los siguientes: 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11 y 12.

10 En la etapa 802, de acuerdo con la matriz base y el factor de expansión correspondiente a la matriz base, se realiza una operación de codificación LDPC para obtener una palabra de código de Nbxz bits de acuerdo con los datos fuente de (Nb-Mb)xz bits.

En el presente documento, z es el factor de expansión y z es un número entero positivo mayor o igual a 1.

Realización 4

15

20

55

60

La realización de la presente invención proporciona un procedimiento de codificación para códigos LDPC estructurados y el proceso de codificación LDPC que se completa usando el procedimiento de codificación, es como se muestra en la figura 9. El procedimiento incluye las etapas siguientes.

En la etapa 901, es determinar una matriz base utilizada para descodificar, que incluye K0 pares adyacentes superiores e inferiores.

La matriz base incluye un bloque A de Mbx(Nb-Mb) correspondiente a bits sistemáticos y un bloque B de Mb × Mb correspondiente a bits de comprobación. La matriz base incluye K1 pares adyacentes superiores e inferiores de un primer tipo y K2 pares adyacentes superiores e inferiores de un segundo tipo, en el presente documento K0 = K1 + K2, K0 es un número entero positivo mayor o igual a 6\*Mb, y K2 es un número entero positivo mayor o igual a 1 y menor o igual a 2\*Mb.

Los pares adyacentes superiores e inferiores son un conjunto constituido por dos elementos  $\{hb_{ij}, hb_{((i+1) \mod Mb)j}\}$  correspondiente a matrices cuadradas no nulas en cada matriz base.

Los pares adyacentes superiores e inferiores del primer tipo son pares adyacentes superiores e inferiores que son congruentes con  $((hb_{ij}-hb_{((i+1)mod\ Mb)j})) \mod Q = a$ .

Los pares adyacentes superiores e inferiores del segundo tipo son pares adyacentes superiores e inferiores que son congruentes con  $(hb_{ij}-hb_{((i+1)mod\ Mb)i})$  mod Q = d.

En el presente documento, hb<sub>ij</sub> representa un elemento en la fila i<sup>ésima</sup> y la columna j<sup>ésima</sup> de la matriz base, en el presente documento, a y d no son iguales, a y d son números enteros mayores o iguales a 0 y menores o iguales a Q-1, Q es un factor de multiplicación de un factor de expansión z, un peso de columna de la columna jésima se refiere al número total de elementos correspondientes a la matriz cuadrada distinta de cero, en la columna jésima de la matriz base, i es un índice de fila de la matriz base, j es un índice de columna de la matriz base, i = 0, 1, ..., Mb-1, j=0, 1, ..., Nb-1.

Si K2 es mayor o igual a 3, para dos filas cualquiera adyacentes (la fila  $x1^a$  y la fila  $((x1 + 1) \text{ mod Mb})^{\text{ésima}})$ , el número de pares adyacentes del segundo tipo es como máximo 3. En esta etapa, x1 toma el valor de 0 a Mb-1.

El valor de Q = 2 y, para ejemplos que no forman parte de la invención, Q toma cualquiera de los siguientes: 3, 4, 5, 6, 7 y 8.

El número total de elementos que corresponden a las matrices cuadradas no nulas en la columna jésima de la matriz base es  $L_j$ , el primer elemento de arriba a abajo es 0,  $L_j$  es un número entero positivo mayor o igual a 1, y j = 0, 1, ..., Nh-1

En la etapa 902, de acuerdo con la matriz base y el factor de expansión correspondiente, se realiza una operación de descodificación LDPC para obtener los datos de información de (Nb-Mb)xz bits de acuerdo con la palabra de código de Nbxz bits.

En esta etapa, z es el factor de expansión y z es un número entero positivo mayor o igual a 1.

Esta etapa incluye específicamente lo siguiente.

1. Al usar un algoritmo de propagación de creencias (BP) en capas o un algoritmo min-sum corregido, se realiza una actualización de fila en la matriz base, que incluye:

en una iteración de número impar, además de actualizar la información extrínseca correspondiente a elementos que no sean pares adyacentes del segundo tipo, solo se actualiza la información extrínseca correspondiente a un elemento en cada par adyacente del segundo tipo,

en una iteración de número par, además de actualizar la información extrínseca correspondiente a elementos que no sean pares adyacentes del segundo tipo, solo se actualiza la información extrínseca correspondiente a otro elemento en cada par adyacente del segundo tipo, y

la información extrínseca es información de un nodo de comprobación a un nodo variable; y

2. se calcula una razón logarítmica de verosimilitud para una palabra de código utilizando la información extrínseca y se toma una decisión firme y se verifica si el resultado es correcto, y si es correcto, se emite la palabra de código correcta y, si está mal, se continúa un procesamiento de descodificación.

#### Realización 5

15

5

45

La realización de la presente invención proporciona un dispositivo de codificación para códigos LDPC estructurados y la estructura del dispositivo de codificación se muestra en la figura 10. El dispositivo de codificación incluye:

- un módulo de almacenamiento 1001 de la matriz base, configurado para determinar una matriz base utilizada para codificar, que incluye K0 pares adyacentes superiores e inferiores. En el presente documento, la matriz base incluye un bloque A de Mbx (Nb-Mb) correspondiente a bits sistemáticos y un bloque B de MbxMb correspondiente a bits de comprobación. La matriz base incluye K1 pares adyacentes superiores e inferiores de un primer tipo y K2 pares adyacentes superiores e inferiores de un segundo tipo, en el presente documento K0 = K1 + K2, K0 es un número entero positivo mayor o igual a 6\* Mb, K2 es un número entero positivo mayor o igual a 0 y menor o igual a 2\*Mb, los pares adyacentes superiores e inferiores son un conjunto constituido por dos elementos {hb<sub>ij</sub>, hb<sub>((i+1) mod Mb)j}</sub> correspondiente a matrices cuadradas no nulas en cada matriz base, esto es, un conjunto constituido por dos elementos adyacentes que corresponden a matrices cuadradas no nulas en alguna columna de la matriz base, en el presente documento, la última fila y la primera fila se definen como filas adyacentes, y la última fila se define como una fila anterior de la primera fila;

- los pares adyacentes superiores e inferiores del primer tipo son pares adyacentes superiores e inferiores que son congruentes con ((hb<sub>ij</sub>-hb<sub>((i+1)mod Mb)j</sub>) mod Q = a; los pares adyacentes superiores e inferiores del segundo tipo son pares adyacentes superiores e inferiores que son congruentes con (hb<sub>ij</sub>-hb<sub>((i+1)mod Mb)j</sub>) mod Q = d;

- En el presente documento, hb<sub>ij</sub> representa un elemento en la fila i<sup>ésima</sup> y la columna j<sup>ésima</sup> de la matriz base, en el presente documento, a y d no son iguales, a y d son números enteros mayores o iguales a 0 y menores o iguales a Q-1, Q es un factor de multiplicación de un factor de expansión z, un peso de la columna de la j<sup>ésima</sup> columna se refiere al número total de elementos correspondientes a matrices cuadradas no nulas en la j<sup>ésima</sup> columna de la matriz base, i es un índice de fila de la matriz base, j es un índice de columna de la matriz base, i = 0, 1, ..., Mb-1, 40 i=0, 1, ..., Nb-1; v

- un módulo de operación de codificación 1002, configurado para, de acuerdo con la matriz base y el factor de expansión correspondiente a la matriz base, realizar una operación de codificación LDPC para obtener una palabra de código de bits Nbxz de acuerdo con los datos fuente de (Nb-Mb)xz bits, en el presente documento, z es el factor de expansión y z es un número entero positivo mayor o igual a 1.

- Preferentemente, si K2 es mayor o igual a 3, para dos filas cualquiera adyacentes (la fila x1ª y la fila ((x1 + 1) mod Mb)<sup>ésima</sup>), el número de pares adyacentes del segundo tipo es como máximo 3, en el presente documento, el índice de fila x1 toma el valor de 0 a Mb-1.

- El valor de Q = 2 y, para ejemplos que no forman parte de la invención, Q toma cualquiera de los siguientes: 3, 4, 5, 6, 7 y 8.

Preferentemente, el número total de elementos que corresponden a las matrices cuadradas no nulas en la columna jésima de la matriz base es L<sub>j</sub>, el primer elemento de arriba a abajo es 0, L<sub>j</sub> es un número entero positivo mayor o igual a 1, y j = 0, 1, ..., Nb-1.

Preferentemente, el valor de K0 toma cualquiera de los siguientes: 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11 y 12.

- 60 La realización de la presente invención proporciona además un dispositivo de descodificación para códigos LDPC estructurados y la estructura del dispositivo de descodificación se muestra en la figura 11. El dispositivo de descodificación incluye:

- un módulo de almacenamiento 1101 de la matriz base, configurado para determinar una matriz base utilizada para descodificar, que incluye K0 pares adyacentes superiores e inferiores. En el presente documento, la matriz base incluye un bloque A de Mbx (Nb-Mb) correspondiente a bits sistemáticos y un bloque B de MbxMb

correspondiente a bits de comprobación. La matriz base incluye K1 pares adyacentes superiores e inferiores de un primer tipo y K2 pares adyacentes superiores e inferiores de un segundo tipo, en el presente documento K0 = K1 + K2, K0 es un número entero positivo mayor o igual a 6\*Mb, y K2 es un número entero positivo mayor o igual a 1 y menor o igual a 2\*Mb; los pares adyacentes superiores e inferiores se definen como un conjunto constituido por dos elementos {hbij, hb((i+1) mod Mb)j} correspondiente a matrices cuadradas no nulas en cada matriz base, esto es, un conjunto constituido por dos elementos adyacentes que corresponden a matrices cuadradas no nulas en alguna columna de la matriz base, en el presente documento, la última fila y la primera fila se definen como filas adyacentes, y la última fila se define como una fila anterior de la primera fila;

5

10

20

30

45

55

60

65

los pares adyacentes superiores e inferiores del primer tipo son pares adyacentes superiores e inferiores que son congruentes con ((hb<sub>ij</sub>-hb<sub>((i+1)mod Mb)j</sub>) mod Q = a;

los pares adyacentes superiores e inferiores del segundo tipo son pares adyacentes superiores e inferiores que son congruentes con  $(hb_{ij}-hb_{([i+1)mod\ Mb]i})\ mod\ Q=d;$

En el presente documento, hb<sub>ij</sub> representa un elemento en la fila i<sup>ésima</sup> y la columna j<sup>ésima</sup> de la matriz base, en el presente documento, a y d no son iguales, a y d son números enteros de 0 a Q-1, Q es un factor de multiplicación de un factor de expansión z, un peso de la columna de la j<sup>ésima</sup> columna se refiere al número total de elementos correspondientes a matrices cuadradas no nulas en la j<sup>ésima</sup> columna de la matriz base, i es un índice de fila de la matriz base, j es un índice de columna de la matriz base, i = 0, 1, ..., Mb-1, j=0, 1, ..., Nb-1;

un módulo de operación de descodificación 1102, configurado para, de acuerdo con la matriz base y el factor de expansión correspondiente, realizar una operación de descodificación LDPC para obtener los datos de información de (Nb-Mb)xz bits de acuerdo con una palabra de código de Nbxz bits, en el presente documento, z es el factor de expansión y z es un número entero positivo mayor o igual a 1.

Preferentemente, si K2 es mayor o igual a 3, para dos filas cualquiera adyacentes (la fila x1ª y la fila ((x1 + 1) mod Mb)<sup>ésima</sup>), el número de pares adyacentes del segundo tipo es como máximo 3. En el presente documento, el índice de fila x1 toma el valor de 0 a Mb-1.

El valor de Q = 2 y, para ejemplos que no forman parte de la invención, Q toma cualquiera de los siguientes: 3, 4, 5, 6, 7 y 8.

Preferentemente, el número total de elementos que corresponden a las matrices cuadradas no nulas en la columna jésima de la matriz base es  $L_j$ , el primer elemento de arriba a abajo es 0,  $L_j$  es un número entero positivo mayor o igual a 1, y j = 0, 1, ..., Nb-1.

Preferentemente, el módulo de operación de descodificación 1102 incluye: una unidad de actualización de filas para la matriz base 11021, configurado para: usar un algoritmo de BP en capas y un algoritmo min-sum corregido para realizar una actualización de fila en la matriz base, que incluye:

en una iteración de número impar, además de actualizar la información extrínseca correspondiente a elementos que no sean pares adyacentes del segundo tipo, solo se actualiza la información extrínseca correspondiente a un elemento en cada par adyacente del segundo tipo,

en una iteración de número par, además de actualizar la información extrínseca correspondiente a elementos que no sean pares adyacentes del segundo tipo, solo se actualiza la información extrínseca correspondiente a otro elemento en cada par adyacente del segundo tipo, y

la información extrínseca es información del nodo de comprobación al nodo variable; y

una unidad de decisión de descodificación 11022, configurado para calcular una razón logarítmica de verosimilitud para una palabra de código utilizando la información extrínseca y realizar una decisión firme y verificar si el resultado es correcto y, si es correcto, se envía la palabra de código correcta y, si es incorrecto, se continúa el procesamiento de descodificación.

Las realizaciones de la presente invención proporcionan un procedimiento de codificación, procedimiento de descodificación, dispositivo de codificación y dispositivo de descodificación para códigos de LDPC estructurados. Al determinar una matriz base utilizada para descodificar o codificar, que incluye K0 pares adyacentes superiores e inferiores, de acuerdo con la matriz base y el factor de expansión correspondiente a la matriz base, se completa la descodificación o codificación, se realiza la codificación y descodificación LDPC a la alta velocidad de la cola y se resuelve el problema existente de baja eficiencia de un descodificador/codificador. La matriz diseñada por la realización de la presente invención puede mejorar de forma revolucionaria la eficiencia del descodificador en combinación con un algoritmo de descodificación específico, que es significativa para el desarrollo y la aplicación de los códigos LDPC de baja complejidad y velocidad ultraalta. Las soluciones técnicas proporcionadas por las realizaciones de la presente invención pueden ser aplicables a una tecnología de codificación de corrección de errores para la transmisión de datos en un sistema de comunicación digital para obtener códigos LDPC cuya eficiencia se mejora y cuya complejidad se reduce, y particularmente aplicables a un escenario de velocidad ultraalta.

Los expertos en la técnica pueden entender que todas o parte de las etapas de las realizaciones mencionadas anteriormente pueden implementarse usando un proceso de programa informático y el programa informático puede almacenarse en un medio de almacenamiento legible por ordenador y ejecutarse en una plataforma de hardware adecuada (tal como un sistema, equipo, aparatos, dispositivo y así sucesivamente), y durante la ejecución, se incluye una de las etapas de la realización del procedimiento o una combinación de las mismas.

Como alternativa, todas o parte de las etapas de las realizaciones mencionadas anteriormente también se pueden implementar con circuitos integrados, estas etapas pueden hacerse en módulos de circuito integrado individuales respectivamente o una pluralidad de los módulos o etapas pueden hacerse en un solo módulo de circuito integrado para ser implementado. Por lo tanto, la presente invención no se limita a ninguna combinación específica de hardware y software.

Cada dispositivo/módulo funcional/unidad funcional en las realizaciones mencionadas anteriormente puede implementarse con dispositivos informáticos universales, pueden concentrarse en un único dispositivo informático o distribuirse en una red compuesta por una pluralidad de dispositivos informáticos.

Cuando cada dispositivo/módulo funcional/unidad funcional en las realizaciones mencionadas anteriormente se implementa en forma de módulo funcional de software y se vende o utiliza como un producto individual, pueden almacenarse en un medio de almacenamiento legible por ordenador. El medio de almacenamiento legible por ordenador mencionado anteriormente puede ser una memoria de solo lectura, disco magnético u óptico, y similares.

Cualquier persona familiarizada con el campo técnico de la técnica puede concebir fácilmente cambios o reemplazos dentro del alcance técnico desvelado en la presente invención y los cambios o reemplazos deben caer dentro del alcance de protección de la presente invención. Por lo tanto, el alcance de protección de la presente invención debe estar sujeto al alcance de protección de las reivindicaciones.

#### Aplicabilidad industrial

25

30 Usando la descodificación/codificación aplicable a los códigos LDPC estructurados en alas realizaciones de la presente invención, se realizan codificaciones y descodificaciones LDPC a velocidad de la cola alta.

#### **REIVINDICACIONES**

1. Un procedimiento de codificación para códigos de comprobación de paridad de baja densidad estructurados, LDPC, que comprende:

5

10

25

35

determinar (801) una matriz base MbxNb usada para codificar, donde la matriz base comprende un bloque A de Mbx(Nb-Mb) correspondiente a bits sistemáticos y un bloque B de MbxMb correspondiente a bits de comprobación, la matriz base tiene K0 pares adyacentes superiores e inferiores, los K0 pares adyacentes superiores e inferiores tienen K1 pares adyacentes superiores e inferiores de un primer tipo y K2 pares adyacentes arriba y abajo de un segundo tipo, donde K0 = K1 + K2, los pares adyacentes superiores e inferiores son un conjunto constituido por dos elementos {hb<sub>ii</sub>, hb<sub>((i+1) mod Mb)i</sub>} en la matriz base correspondiente a matrices cuadradas no nulas,

los pares adyacentes superiores e inferiores del primer tipo son pares adyacentes superiores e inferiores que son congruentes con  $(hb_{ij}-hb_{((i+1) \mod Mb)i}) \mod Q = a y$

- los pares adyacentes superiores e inferiores del segundo tipo son pares adyacentes superiores e inferiores que 15 son congruentes con  $(hb_{ij}-hb_{([i+1)mod\ Mb)j})$  mod Q=d donde  $hb_{ij}$  representa un elemento en la fila i  $e^{isima}$  y la columna  $e^{isima}$  de una matriz base y corresponde a una

- matriz cuadrada nula de zxz, una matriz identidad de zxz o una matriz de desplazamiento cíclico de una matriz identidad de zxz de una matriz de comprobación de paridad de un código LDPC estructurado, donde a y d no son iguales, a y d son números enteros mayores o iguales a 0 y menores o iguales a Q-1, Q es un factor del factor de

- 20 expansión z del código LDPC estructurado, i es un índice de fila de la matriz base, j es un índice de columna de la matriz base, i = 0, 1, ..., Mb-1, j=0, 1, ..., Nb-1; y

- de acuerdo con la matriz base y el factor de expansión z correspondiente a la matriz base, realizar (802) una operación de codificación LDPC para obtener una palabra de código de Nbxz bits basada en datos fuente de (Nb-Mb)xz bits, donde z es un número entero positivo mayor que 1, caracterizado por que

- K0 es un número entero positivo mayor o igual a 6\* Mb, K2 es un entero positivo mayor o igual a 0 y menor que 2\*Mb y Q es 2.

- 2. El procedimiento de acuerdo con la reivindicación 1, donde,

- si K2 es mayor o igual a 3, para cualquier fila x1<sup>a</sup> y fila ((x1 + 1) mod Mb)<sup>ésima</sup>, un número de pares adyacentes del 30 segundo tipo es como máximo 3, donde x1 = 0, 1, ..., Mb-1.

- 3. El procedimiento de acuerdo con la reivindicación 1, donde un número total de elementos en una columna jésima de la matriz base correspondiente a las matrices cuadradas no nulas es Li un primer elemento de arriba a abajo en la columna jésima de la matriz base es 0, Li es un número entero positivo mayor o igual a 1, y j = 0, 1, ..., Nb-1.

- 4. Un procedimiento de descodificación en capas para códigos de comprobación de paridad de baja densidad estructurados, LDPC, que comprende:

- 40 determinar (901) una matriz base MbxNb utilizada para descodificar, donde la matriz básica comprende un bloque A de Mbx (Nb-Mb) correspondiente a bits sistemáticos y un bloque B de MbxMb correspondiente a bits de comprobación, la matriz base tiene K0 pares adyacentes superiores e inferiores, los K0 pares adyacentes superiores e inferiores tienen K1 pares adyacentes superiores e inferiores de un primer tipo y K2 pares adyacentes arriba y abajo de un segundo tipo, donde K0 = K1 + K2, los pares adyacentes superiores e inferiores 45 son un conjunto constituido por dos elementos {hb<sub>ii</sub>, hb<sub>((i+1) mod Mb)i</sub>} en la matriz base correspondiente a matrices cuadradas no nulas.

- los pares adyacentes superiores e inferiores del primer tipo son pares adyacentes superiores e inferiores que son congruentes con  $(hb_{ij}-hb_{((i+1) \mod Mb)j}) \mod Q = a, y$

- los pares adyacentes superiores e inferiores del segundo tipo son pares adyacentes superiores e inferiores que 50

- son congruentes con  $(hb_{ij}-hb_{((i+1)mod\;Mb)j}) \mod Q = d$  donde  $hb_{ij}$  representa un elemento en la fila  $i^{\acute{e}sima}$  y la columna  $j^{\acute{e}sima}$  de una matriz base y corresponde a una matriz cuadrada nula de zxz, una matriz identidad de zxz o una matriz de desplazamiento cíclico de una matriz identidad de zxz de una matriz de comprobación de paridad de un código LDPC estructurado, donde a y d no son iguales, a y d son números enteros mayores o iguales a 0 y menores o iguales a Q-1, Q es un factor del factor de

- 55 expansión z del código LDPC estructurado, i es un índice de fila de la matriz base, j es un índice de columna de la matriz base, i = 0, 1, ..., Mb-1, j=0, 1, ..., Nb-1; y

- de acuerdo con la matriz base y un factor de expansión z correspondiente, realizar (902) una operación de descodificación LDPC para obtener datos de información de (Nb-Mb)xz bits basados en una palabra de código de Nbxz bits, donde z es un número entero positivo mayor que 1, caracterizado por que

- K0 es un número entero positivo mayor o igual a 6\* Mb, K2 es un entero positivo mayor o igual a 0 y menor que 60 2\*Mb y Q es 2.

- 5. El procedimiento de acuerdo con la reivindicación 4, donde,

- si K2 es mayor o igual a 3, para cualquier fila x1<sup>a</sup> y fila ((x1 + 1) mod Mb)<sup>ésima</sup>, un número de pares adyacentes del segundo tipo es como máximo 3, donde x1 = 0, 1, ..., Mb-1. 65

- 6. El procedimiento de acuerdo con la reivindicación 4, donde un número total de elementos en una columna jésima de la matriz base correspondiente a las matrices cuadradas no nulas es  $L_j$ , un primer elemento de arriba a abajo en la columna jésima de la matriz base es 0,  $L_j$  es un número entero positivo mayor o igual a 1, y j = 0, 1, ..., Nb-1.

- 7. El procedimiento de acuerdo con la reivindicación 4, donde la etapa de realizar una operación de descodificación LDPC comprende: usar una propagación de creencias en capas, BP, algoritmo y un algoritmo min-sum corregido para realizar una actualización de fila en la matriz base, que comprende:

- en una iteración LDPC de número impar, además de actualizar la información extrínseca correspondiente a elementos que no sean pares adyacentes del segundo tipo, solo actualizar la información extrínseca correspondiente a un elemento en cada par adyacente del segundo tipo.

- en una iteración LDPC de números pares, además de actualizar la información extrínseca correspondiente a elementos que no sean pares adyacentes del segundo tipo, solo actualizar la información extrínseca correspondiente a otro elemento en cada par adyacente del segundo tipo,

- donde la información extrínseca es información de un nodo de comprobación a un nodo variable; y calcular una razón logarítmica de verosimilitud para una palabra de código utilizando la información extrínseca y realizar una decisión firme, y comprobar si un resultado es correcto, y si es correcto, generar una palabra de código correcta y, si es incorrecto, continuar la descodificación LDPC.

- 8. Un dispositivo de codificación para códigos estructurados de comprobación de paridad de baja densidad, LDPC, que comprende:

25

45

55

60

- un módulo de almacenamiento de matriz base (1001), configurado para almacenar al menos una matriz base Mb × Nb utilizada para codificar, donde la matriz base comprende un bloque A de Mbx(Nb-Mb) correspondiente a bits sistemáticos y un bloque B de MbxMb correspondiente a bits de comprobación, la matriz base tiene K0 pares adyacentes superiores e inferiores, los K0 pares adyacentes superiores e inferiores tienen K1 pares adyacentes superiores e inferiores de un primer tipo y K2 pares adyacentes arriba y abajo de un segundo tipo, donde K0 = K1 + K2, los pares adyacentes superiores e inferiores son un conjunto constituido por dos elementos {hb<sub>ij</sub>, hb<sub>((i+1) mod Mb)i</sub>} en la matriz base correspondiente a matrices cuadradas no nulas,

- los pares adyacentes superiores e inferiores del primer tipo son pares adyacentes superiores e inferiores que son congruentes con (hb<sub>ii</sub>-hb<sub>((i+1) mod Mb)i)</sub>) mod Q = a, y

- los pares adyacentes superiores e inferiores del segundo tipo son pares adyacentes superiores e inferiores que son congruentes con  $(hb_{ij}-hb_{((i+1)mod\ Mb)j})\ mod\ Q=d$