# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11) Número de publicación: 2 791 781

61 Int. Cl.:

H04L 7/033 (2006.01) H04L 25/14 (2006.01) H04L 25/49 (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

T3

(86) Fecha de presentación y número de la solicitud internacional: 01.10.2014 PCT/US2014/058609

(87) Fecha y número de publicación internacional: 09.04.2015 WO15050980

(96) Fecha de presentación y número de la solicitud europea: 01.10.2014 E 14793347 (7)

(97) Fecha y número de publicación de la concesión europea: 18.03.2020 EP 3053296

(54) Título: Recuperación de datos y reloj de doble velocidad de transferencia de datos N-factorial

(30) Prioridad:

03.10.2013 US 201361886567 P 14.04.2014 US 201414252450

Fecha de publicación y mención en BOPI de la traducción de la patente: **05.11.2020**

(73) Titular/es:

QUALCOMM INCORPORATED (100.0%) 5775 Morehouse Drive San Diego, CA 92121-1714, US

(72) Inventor/es:

SENGOKU, SHOICHIRO

(74) Agente/Representante:

FORTEA LAGUNA, Juan José

## **DESCRIPCIÓN**

Recuperación de datos y reloj de doble velocidad de transferencia de datos N-factorial

[0001] La presente solicitud de patente reivindica prioridad a la solicitud provisional no. 61/886,567 titulada "N Factorial Clock and Data Recovery With Negative Hold Time Sampling [Recuperación de datos y reloj N-factorial con muestreo de tiempo de espera negativo]" presentada el 3 de octubre de 2013, y a la solicitud no provisional no. 14/252,450 titulada "N Factorial Dual Data Rate Clock and Data Recovery [Recuperación de datos y reloj de doble velocidad de transferencia de datos N-factorial]" presentada el 14 de abril de 2014.

#### **ANTECEDENTES**

#### Campo

20

25

30

35

40

45

50

55

60

65

15 **[0002]** La presente divulgación se refiere en general a una interfaz entre un procesador principal [host] y un dispositivo periférico tal como una cámara y, más particularmente, a mejorar la generación de reloj para la transferencia de datos de doble velocidad de transferencia de datos en una interfaz de comunicación de *N* hilos.

#### **Antecedentes**

[0003] Los fabricantes de dispositivos móviles, tales como teléfonos celulares, pueden obtener componentes de los dispositivos móviles de diversas fuentes, incluidos diferentes fabricantes. Por ejemplo, un procesador de aplicación en un teléfono celular puede obtenerse de un primer fabricante, mientras que la pantalla para el teléfono celular puede obtenerse de un segundo fabricante. El procesador de aplicaciones y una pantalla u otro dispositivo pueden interconectarse usando una interfaz física patentada o basada en normas. Por ejemplo, una pantalla puede proporcionar una interfaz que cumpla con la norma de interfaz de sistema de pantalla (DSI) especificada por la Alianza de la Interfaz de Procesador de la Industria Móvil (MIPI).

[0004] En un ejemplo, un sistema de transferencia de datos de múltiples señales puede emplear señalización diferencial de múltiples hilos, tal como la señalización diferencial de bajo voltaje (LVDS) trifásica o N-factorial (N!), la transcodificación (por ejemplo, la conversión de datos de digital a digital de un tipo de codificación a otro) puede realizarse para incorporar información de reloj de símbolos al provocar una transición de símbolo en cada ciclo de símbolo, en lugar de enviar información de reloj en carriles de datos separados (trayectos de transmisión diferenciales). Incorporar información de reloj mediante transcodificación es una forma efectiva de minimizar la distorsión entre las señales de reloj y de datos, así como eliminar la necesidad de un bucle de fase bloqueada (PLL) para recuperar la información de reloj de las señales de datos.

[0005] Las capacidades y la funcionalidad de los dispositivos móviles continúan creciendo y existe una demanda resultante de un ancho de banda cada vez mayor entre los componentes dentro de los dispositivos móviles y similares. En consecuencia, existe una necesidad continua de comunicaciones optimizadas en general y una confiabilidad mejorada de la transferencia de datos en enlaces de comunicación por cable de múltiples señales.

[0006] Se llama la atención sobre WO 2008/151251 A1, que está dirigido a técnicas para la codificación de múltiples hilos con un reloj incorporado. Un componente transmisor puede comprender al menos un módulo codificador para generar un conjunto de símbolos, estando representado cada símbolo por una combinación de niveles de señal en un conjunto de hilos. El componente transmisor también puede comprender al menos un módulo de señalización para transmitir uno o más de los símbolos sobre el conjunto de hilos de acuerdo con un reloj de transmisión. El componente transmisor puede comprender adicionalmente lógica de control para restringir la transmisión del primer y el segundo subconjuntos del conjunto de símbolos a las respectivas partes primera y segunda de un ciclo de reloj del reloj de transmisión, de modo que una señal diferencial entre al menos dos del conjunto de hilos exhibe un comportamiento de conmutación que tiene la misma frecuencia que el reloj de transmisión.

[0007] Se llama la atención sobre US 2008/212709 A1, que está dirigido a una interfaz en serie de alta velocidad. En un aspecto, la interfaz en serie de alta velocidad usa modulación trifásica para codificar conjuntamente datos e información de reloj. Por consiguiente, se elimina la necesidad de eliminar la distorsión de los circuitos en el extremo receptor de la interfaz, lo que se traduce en una reducción del tiempo de arranque del enlace y una mejora de la eficacia del enlace y del consumo de energía. En un ejemplo, la interfaz en serie de alta velocidad usa menos conductores de señal que los sistemas convencionales con conductores individuales para datos e información de reloj. En otro ejemplo, la interfaz en serie permite que los datos se transmitan a cualquier velocidad sin que el extremo receptor tenga ningún conocimiento previo de la velocidad de transmisión de datos. En otro aspecto, la interfaz en serie de alta velocidad usa modulación trifásica, codificada por polaridad, para codificar conjuntamente datos e información de reloj.

### Breve explicación

[0008] De acuerdo con la presente invención, se proporcionan un procedimiento y un aparato para la recuperación

de datos y reloj de doble velocidad de transferencia de datos N factorial, tal como se expone en las reivindicaciones independientes. Los modos de realización preferentes se describen en las reivindicaciones dependientes.

[0009] Los modos de realización divulgados en el presente documento proporcionan sistemas, procedimientos y aparatos relacionados con interfaces de múltiples hilos. Los sistemas, procedimientos y aparatos están relacionados con el uso de circuitos receptores que pueden extraer señales de reloj confiables para la recuperación de datos transmitidos usando sincronización de doble velocidad de transferencia de datos.

5

25

30

35

60

65

- [0010] En un aspecto de la divulgación, un procedimiento de comunicación de datos incluye recibir una secuencia de símbolos de una pluralidad de hilos de señal, siendo recibido cada símbolo en la secuencia de símbolos durante uno de un intervalo de transmisión impar o un intervalo de transmisión par, generar una primera señal de reloj de las transiciones en el estado de la señalización de la pluralidad de hilos que ocurren entre cada intervalo de transmisión impar y un intervalo de transmisión par consecutivo, generar una segunda señal de reloj de transiciones en el estado de la señalización de la pluralidad de hilos que ocurre entre cada intervalo de transmisión par y un intervalo de transmisión impar consecutivo, usar la primera señal de reloj para capturar un primer conjunto de símbolos, que incluye los símbolos en la secuencia de símbolos que se reciben en intervalos de transmisión pares, y usar la segunda señal de reloj para capturar un segundo conjunto de símbolos, que incluye los símbolos en la secuencia de símbolos que se reciben en intervalos de transmisión impar.

- 20 **[0011]** En un aspecto de la divulgación, cada intervalo de transmisión impar está precedido inmediatamente por un primer intervalo de transmisión par e inmediatamente sucedido por un segundo intervalo de transmisión par.

- **[0012]** En un aspecto de la divulgación, cada par de símbolos consecutivos recibidos en la secuencia de símbolos incluye un símbolo recibido durante un intervalo de transmisión impar y un símbolo recibido durante un intervalo de transmisión par.

- [0013] En un aspecto de la divulgación, la temporización de un primer flanco en la primera señal de reloj se basa en una primera transición que ocurre entre un primer símbolo y un segundo símbolo que se recibe inmediatamente después del primer símbolo. La temporización de un primer flanco en la segunda señal de reloj puede basarse en una segunda transición que ocurre entre el segundo símbolo y un tercer símbolo que se recibe inmediatamente después del segundo símbolo.

- [0014] En un aspecto de la divulgación, la temporización de un segundo flanco en la primera señal de reloj se basa en la temporización del primer flanco en la segunda señal de reloj. La temporización de un segundo flanco en la segunda señal de reloj puede basarse en la temporización de un tercer flanco en la primera señal de reloj, donde la temporización del tercer flanco en la primera señal de reloj se basa en una tercera transición que ocurre entre el tercer símbolo y un cuarto símbolo que se recibe inmediatamente después del tercer símbolo.

- [0015] En un aspecto de la divulgación, generar la primera señal de reloj incluye ignorar la segunda transición. La generación de la segunda señal de reloj puede incluir ignorar la primera transición.

- [0016] En un aspecto de la divulgación, cada par de símbolos consecutivos en la secuencia de símbolos incluye dos símbolos que están asociados con diferentes estados de señalización en la pluralidad de hilos de señal.

- 45 **[0017]** En un aspecto de la divulgación, recibir la secuencia de símbolos de la pluralidad de hilos de señal incluye recibir señales diferenciales de todas las combinaciones posibles de dos hilos de señal en la pluralidad de hilos de señal. Cada símbolo en la secuencia de símbolos puede codificarse en una combinación de estados de señalización de las señales diferenciales.

- 50 [0018] En un aspecto de la divulgación, recibir la secuencia de símbolos de la pluralidad de hilos de señal incluye recibir una señal trifásica de cada uno de los tres hilos de señal, donde cada uno de los tres hilos de señal está en un estado de la señalización diferente con respecto a los otros hilos de señal en cada intervalo de transmisión. Cada símbolo en la secuencia de símbolos puede codificarse en una combinación de estados de señalización de los tres hilos de señal.

55

- [0019] En un aspecto de la divulgación, un aparato incluye medios para recibir una secuencia de símbolos de una pluralidad de hilos de señal, donde cada símbolo en la secuencia de símbolos se recibe durante uno de un intervalo de transmisión impar o un intervalo de transmisión par, medios para generar una primera señal de reloj de las transiciones en el estado de la señalización de la pluralidad de hilos de señal que ocurren entre cada intervalo de transmisión impar y un intervalo de transmisión par consecutivo, medios para generar una segunda señal de reloj de las transiciones en el estado de la señalización de la pluralidad de hilos de señal que ocurre entre cada intervalo de transmisión par y un intervalo de transmisión impar consecutivo, medios para usar la primera señal de reloj para capturar un primer conjunto de símbolos, que incluye los símbolos en la secuencia de símbolos que se reciben en intervalos de transmisión pares, y medios para usar la segunda señal de reloj para capturar un segundo conjunto de símbolos, que incluye símbolos en la secuencia de símbolos que se reciben en intervalos de transmisión impares.

[0020] En un aspecto de la divulgación, un receptor incluye una pluralidad de circuitos de interfaz de línea configurados para recibir señales de una pluralidad de hilos de señal y un circuito CDR. El circuito CDR puede configurarse para recibir una secuencia de símbolos de la pluralidad de hilos de señal, donde cada símbolo en la secuencia de símbolos se recibe durante uno de un intervalo de transmisión impar o un intervalo de transmisión par, generar una primera señal de reloj de las transiciones en el estado de la señalización de la pluralidad de hilos de señal que ocurren entre cada intervalo de transmisión impar y un intervalo de transmisión par consecutivo, generar una segunda señal de reloj a partir de transmisión par y un intervalo de transmisión impar consecutivo, usar la primera señal de reloj para capturar un primer conjunto de símbolos que incluye símbolos en la secuencia de símbolos que se reciben en intervalos de transmisión impares.

[0021] En un aspecto de la divulgación, un medio de almacenamiento legible por procesador tiene una o más instrucciones almacenadas en el mismo. Las instrucciones pueden ser ejecutadas por al menos un circuito de procesamiento. Las instrucciones pueden hacer que el al menos un circuito de procesamiento reciba una secuencia de símbolos de una pluralidad de hilos de señal, donde cada símbolo en la secuencia de símbolos se recibe durante uno de un intervalo de transmisión impar o un intervalo de transmisión par, generar una primera señal de reloj de las transiciones en el estado de la señalización de la pluralidad de hilos de señal que ocurren entre cada intervalo de transmisión impar y un intervalo de transmisión par consecutivo, generar una segunda señal de reloj de las transiciones en el estado de la señalización de la pluralidad de hilos de señal que ocurren entre cada intervalo de transmisión par y un intervalo de transmisión impar consecutivo, usar la primera señal de reloj para capturar un primer conjunto de símbolos, que incluye los símbolos en la secuencia de símbolos que se reciben en intervalos de transmisión pares, y usar la segunda señal de reloj para capturar un segundo conjunto de símbolos, que incluye los símbolos en la secuencia de símbolos que se reciben en intervalos de transmisión impares.

#### **BREVE DESCRIPCIÓN DE LOS DIBUJOS**

### [0022]

5

10

15

20

25

35

40

45

60

65

La FIG. 1 representa un aparato que emplea un enlace de datos entre dispositivos de circuitos integrados (CI), que funciona selectivamente de acuerdo con una de una pluralidad de normas disponibles.

La FIG. 2 ilustra una arquitectura de sistema para un aparato que emplea un enlace de datos entre dispositivos de CI.

La FIG. 3 ilustra un ejemplo de una interfaz de N! multihilos básicos.

La FIG. 4 ilustra un ejemplo de un codificador de datos por polaridad de N fases.

La FIG. 5 ilustra la señalización en una interfaz codificada de N fases.

La FIG. 6 ilustra un decodificador de datos de polaridad trifásica.

La FIG. 7 ilustra un primer circuito de recuperación de datos y reloj de acuerdo con ciertos aspectos divulgados en el presente documento.

La FIG. 8 ilustra la temporización de ciertas señales generadas por el circuito de recuperación de datos y reloj de la FIG. 7.

La FIG. 9 ilustra un segundo circuito de recuperación de datos y reloj de acuerdo con ciertos aspectos divulgados en el presente documento.

La FIG. 10 es un diagrama de temporización que ilustra el funcionamiento del circuito de recuperación de datos y reloj de la FIG. 9.

La FIG. 11 es un diagrama de flujo que ilustra un procedimiento para comunicaciones de datos de acuerdo con ciertos aspectos divulgados en el presente documento.

La FIG. 12 es un diagrama que ilustra un ejemplo simplificado de una implementación de hardware para un aparato receptor de acuerdo con determinados aspectos divulgados en el presente documento.

### **DESCRIPCIÓN DETALLADA**

[0023] A continuación se describen diversos aspectos con referencia a los dibujos. En la siguiente descripción se exponen, para propósitos explicativos, numerosos detalles específicos para proporcionar un entendimiento absoluto de uno o más aspectos. Sin embargo, puede resultar evidente que dicho(s) aspecto(s) se puede(n) llevar a la práctica sin estos detalles específicos.

[0024] Tal y como se usan en esta solicitud, los términos "componente", "módulo", "sistema" y similares pretenden incluir una entidad relacionada con la informática, tal como, de forma no limitativa, hardware, firmware, una combinación de hardware y software, software o software en ejecución. Por ejemplo, un componente puede ser, de forma no limitativa, un proceso que se ejecuta en un procesador, un procesador, un objeto, un ejecutable, un hilo de ejecución, un programa y/o un ordenador. A modo de ilustración, tanto una aplicación que se ejecute en un dispositivo informático como el dispositivo informático pueden ser un componente. Uno o más componentes pueden residir dentro de un proceso y/o hilo de ejecución, y un componente puede estar ubicado en un ordenador y/o estar distribuido entre dos o más ordenadores. Además, estos componentes se pueden ejecutar desde diversos medios legibles por ordenador que tengan diversas estructuras de datos almacenadas en los mismos. Los componentes se pueden comunicar por medio de procesos locales y/o remotos, tales como de acuerdo con una señal que tiene uno o más paquetes de datos, tales como datos de un componente que interactúa con otro componente en un sistema local, un sistema distribuido y/o a través de una red, tal como Internet, con otros sistemas por medio de la señal.

5

10

25

30

35

40

45

50

55

60

65

[0025] Por otro lado, el término "o" pretende significar una "o" inclusiva en lugar de una "o" exclusiva. Es decir, a menos que se especifique de otro modo, o que resulte claro a partir del contexto, la frase "X emplea A o B" pretende querer decir cualquiera de las permutaciones incluyentes naturales. Es decir, la frase "X emplea A o B" se satisface en cualquiera de los siguientes casos: X utiliza A; X utiliza B; o X utiliza tanto A como B. Además, los artículos "un" y "uno/a", según se utilizan en esta solicitud y en las reivindicaciones adjuntas, deberían ser interpretados, en general, con el significado de "uno/a o más", a no ser que se especifique lo contrario o que resulte claro a partir del contexto que se orientan a una forma en singular.

[0026] Determinados aspectos de la invención se pueden aplicar a enlaces de comunicaciones implantados entre dispositivos electrónicos que son subcomponentes de un aparato móvil, tal como un teléfono, un dispositivo informático móvil, un electrodoméstico, componentes electrónicos de un automóvil, sistemas de aviónica, etc. Ejemplos de un aparato móvil incluyen un teléfono celular, un teléfono inteligente, un teléfono con protocolo de inicio de sesión (SIP), un ordenador portátil, un notebook, un netbook, un smartbook, un asistente digital personal (PDA), un radio vía satélite, un dispositivo de sistema de posicionamiento global (GPS), un dispositivo multimedia, un dispositivo de vídeo, un reproductor de audio digital (por ejemplo, un reproductor de MP3), una cámara, una consola de juegos, un dispositivo informático ponible (por ejemplo, un reloj inteligente, un dispositivo de salud o rastreador de actividad física, etc.), un electrodoméstico, un sensor, una máquina expendedora o cualquier otro dispositivo que funcione de manera similar.

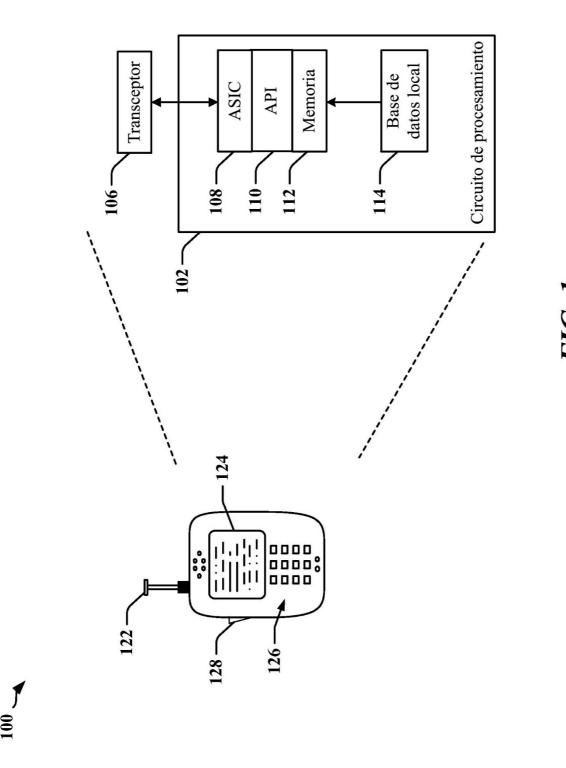

[0027] La FIG. 1 representa un aparato que puede emplear un enlace de comunicación entre dispositivos de CI. En un ejemplo, el aparato 100 puede incluir un dispositivo de comunicación inalámbrica que comunica a través de un transceptor de RF con una red de acceso por radio (RAN), una red de acceso central, Internet y/u otra red. El aparato 100 puede incluir un transceptor de comunicaciones 106 acoplado de manera operativa al circuito de procesamiento 102. El circuito de procesamiento 102 puede incluir uno o más dispositivos de CI, tales como un CI específico de la aplicación (ASIC) 108. El ASIC 108 puede incluir uno o más dispositivos de procesamiento, circuitos lógicos, etc. El circuito de procesamiento 102 puede incluir y/o acoplarse a un almacenamiento legible por procesador, tal como una memoria 112 que puede mantener instrucciones y datos que pueden ser ejecutados por el circuito de procesamiento 102. El circuito de procesamiento 102 puede ser controlado por uno o más entre un sistema operativo y una capa de interfaz de programación de aplicaciones (API) 110 que da soporte y permite la ejecución de módulos de software que residen en medios de almacenamiento, tales como el dispositivo de memoria 112 del dispositivo inalámbrico. El dispositivo de memoria 112 puede incluir memoria de sólo lectura (ROM) o memoria de acceso aleatorio (RAM), ROM programable borrable eléctricamente (EEPROM), tarjetas de memoria flash o cualquier dispositivo de memoria que pueda usarse en sistemas de procesamiento y plataformas informáticas. El circuito de procesamiento 102 puede incluir o acceder a una base de datos local 114 que puede mantener parámetros operativos y otra información usada para configurar y hacer funcionar el aparato 100. La base de datos local 114 puede implementarse usando uno o más entre un módulo de base de datos, memoria flash, medios magnéticos, EEPROM, medios ópticos, cinta, disco flexible o rígido, o similares. El circuito de procesamiento también puede estar acoplado operativamente a dispositivos externos, tales como una antena 122, una pantalla 124, controles de operador, tales como un botón 128 y un teclado numérico 126, entre otros componentes.

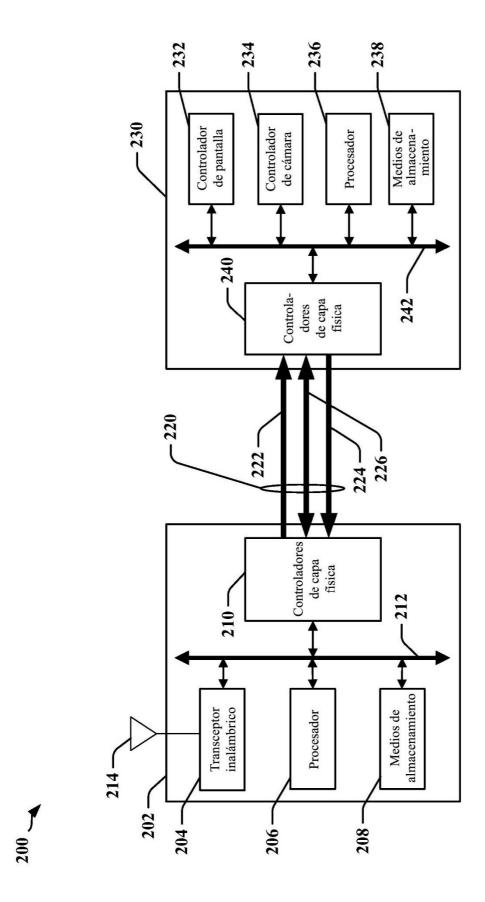

[0028] La FIG. 2 es un esquema de bloques 200 que ilustra ciertos aspectos de un aparato 200, tal como un aparato móvil que emplea un enlace de comunicación 220 para conectar varios subcomponentes. En un ejemplo, el aparato 200 incluye una pluralidad de dispositivos de CI 202 y 230 que intercambian datos e información de control a través de un enlace de comunicación 220. El enlace de comunicación 220 puede usarse para conectar los dispositivos de CI 202 y 222 que están ubicados muy cerca uno del otro, o que están ubicados físicamente en diferentes partes del aparato 200. En un ejemplo, el enlace de comunicación 220 puede proporcionarse en un portador de chips, sustrato o placa de circuito que lleva los dispositivos de CI 202 y 230. En otro ejemplo, un primer dispositivo de CI 202 puede estar ubicado en una sección de teclado numérico de un teléfono plegable, mientras que un segundo dispositivo de CI 230 puede estar ubicado en una sección de pantalla del teléfono plegable. En otro ejemplo, una parte del enlace de comunicación 220 puede incluir un cable o una conexión óptica.

[0029] El enlace de comunicación 220 puede proporcionar múltiples canales 222, 224 y 226. Uno o más canales 226 pueden ser bidireccionales y pueden funcionar en modos semidúplex y/o dúplex completo. Uno o más canales 222 y

224 pueden ser unidireccionales. El enlace de comunicación 220 puede ser asimétrico, proporcionando un mayor ancho de banda en una dirección. En un ejemplo descrito en el presente documento, un primer canal de comunicaciones 222 puede denominarse enlace directo 222, mientras que un segundo canal de comunicaciones 224 puede denominarse enlace inverso 224. El primer dispositivo de Cl 202 puede designarse sistema principal o transmisor, mientras que el segundo dispositivo de Cl 230 puede designarse como un sistema cliente o receptor, incluso si ambos dispositivos de Cl 202 y 230 están configurados para transmitir y recibir en el enlace de comunicaciones 222. En un ejemplo, el enlace directo 222 puede funcionar a una velocidad de transferencia de datos más alta cuando se comunican datos desde un primer dispositivo de Cl 202 a un segundo dispositivo de Cl 230, mientras que el enlace inverso 224 puede funcionar a una velocidad de transferencia de datos más baja cuando se comunican datos desde el segundo dispositivo de Cl 230 al primer dispositivo de Cl 202.

10

15

20

25

30

35

40

45

50

55

[0030] Los dispositivos de CI 202 y 230 pueden incluir cada uno un procesador u otro circuito o dispositivo de procesamiento y/o informático 206, 236. En un ejemplo, el primer dispositivo de CI 202 puede realizar funciones principales del aparato 200, incluido el mantenimiento de comunicaciones inalámbricas a través de un transceptor inalámbrico 204 y una antena 214, mientras que el segundo dispositivo de CI 230 puede admitir una interfaz de usuario que gestiona o hace funcionar un controlador de pantalla 232. En el ejemplo, el segundo dispositivo de CI 230 puede adaptarse para controlar las operaciones de una cámara o dispositivo de entrada de video usando un controlador de cámara 234. Otras características admitidas por uno o más de los dispositivos de CI 202 y 230 pueden incluir un teclado numérico, un componente de reconocimiento de voz y otros dispositivos de entrada o salida. El controlador de pantalla 232 puede incluir circuitos y controladores de software que admiten pantallas tales como un panel de pantalla de cristal líquido (LCD), una pantalla táctil, indicadores, etc. Los medios de almacenamiento 208 y 238 pueden incluir dispositivos de almacenamiento transitorios y/o no transitorios adaptados para mantener instrucciones y datos usados por los respectivos procesadores 206 y 236, y/u otros componentes de los dispositivos de CI 202 y 230. La comunicación entre cada procesador 206, 236 y sus correspondientes medios de almacenamiento 208 y 238 y otros módulos y circuitos puede ser facilitada por uno o más buses 212 y 242, respectivamente.

[0031] El enlace inverso 224 puede funcionar de la misma manera que el enlace directo 222, y el enlace directo 222 y el enlace inverso 224 pueden ser capaces de transmitir a velocidades comparables o a velocidades diferentes, donde la velocidad puede expresarse como velocidad de transferencia de datos y/o velocidades de reloj. Las velocidades de transferencia de datos directa e inversa pueden ser sustancialmente iguales o diferentes en orden de magnitud, dependiendo de la aplicación. En algunas aplicaciones, un solo enlace bidireccional 226 puede admitir comunicaciones entre el primer dispositivo de CI 202 y el segundo dispositivo de CI 230. El enlace directo 222 y/o el enlace inverso 224 pueden configurarse para funcionar en un modo bidireccional cuando, por ejemplo, los enlaces directo e inverso 222 y 224 comparten las mismas conexiones físicas y funcionan de manera semidúplex. En un ejemplo, el enlace de comunicación 220 puede hacerse funcionar para comunicar control, instrucciones y otra información entre el primer dispositivo de CI 202 y el segundo dispositivo de CI 230, de acuerdo con una industria u otra norma.

[0032] En un ejemplo, los enlaces directo e inverso 222 y 224 pueden configurarse o adaptarse para admitir un controlador LCD de 80 tramas por segundo de amplia gama de gráficos de vídeo (WVGA) sin una memoria intermedia de tramas, suministrando datos de píxel a 810 Mbps para actualizar la pantalla. En otro ejemplo, los enlaces directo e inverso 222 y 224 pueden configurarse o adaptarse para permitir comunicaciones entre memoria de acceso aleatorio dinámico (DRAM), tal como memoria de acceso aleatorio dinámico síncrono de doble velocidad de transferencia de datos (SDRAM). Los dispositivos de codificación 210 y/o 230 pueden codificar múltiples bits por transición de reloj, y se pueden usar múltiples conjuntos de hilos para transmitir y recibir datos desde la SDRAM, señales de control, señales de dirección, etc.

[0033] Los enlaces directo e inverso 222 y 224 pueden cumplir, o ser compatibles, con los estándares industriales específicos de la aplicación. En un ejemplo, el estándar MIPI define interfaces de capa física entre un dispositivo de CI de procesador de aplicación 202 y un dispositivo de CI 230 que admite la cámara o pantalla en un dispositivo móvil. El estándar MIPI incluye especificaciones que rigen las características operativas de los productos que cumplen con las especificaciones MIPI para dispositivos móviles. El estándar MIPI puede definir interfaces que emplean buses paralelos de semiconductores complementarios de óxido de metal (CMOS).

**[0034]** El enlace de comunicación 220 de la FIG. 2 puede implementarse como un bus cableado que incluye una pluralidad de hilos de señal (denotados como *N* hilos). Los *N* hilos pueden configurarse para transportar datos codificados en símbolos, donde la información del reloj está incorporada en una secuencia de los símbolos transmitidos a través de la pluralidad de hilos. Ejemplos de técnicas de codificación que se utilizan con interfaces de *N* hilos incluyen la codificación *N*-factorial (*NI*), y la codificación de *N* fases.

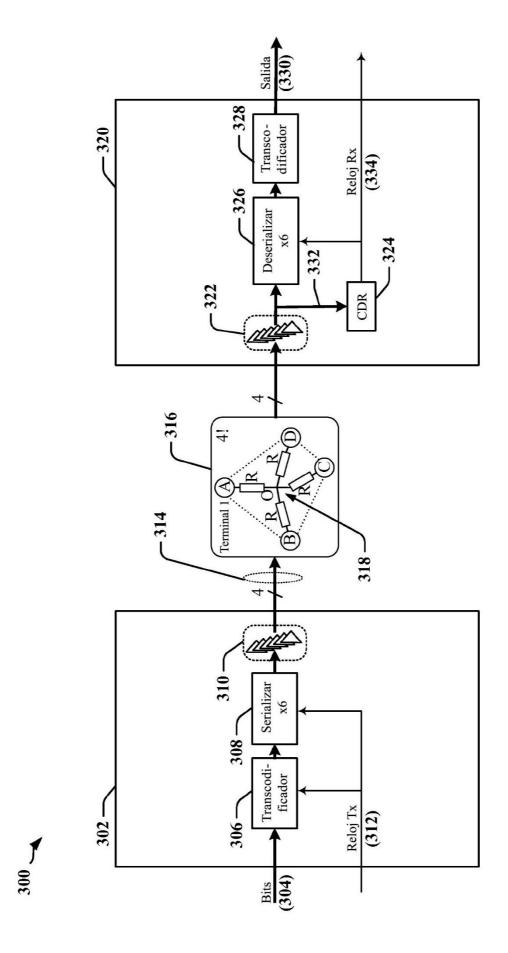

60 [0035] La FIG. 3 es un diagrama que ilustra un ejemplo de codificación N! usada en una interfaz de N hilos 300 proporcionada entre dos dispositivos 302 y 320. En un transmisor 302, se puede usar un transcodificador 306 para codificar datos 304 e información de reloj en símbolos que se transmitirán a través de un conjunto de N hilos 314. La información del reloj puede obtenerse de un reloj de transmisión 312 y puede codificarse en una secuencia de símbolos transmitida en κC₂ señales diferenciales a través de los N hilos 314 asegurando que se produce una transición del estado de la señalización en al menos una de las κC₂ señales entre símbolos consecutivos. Cuando la codificación N! se usa para accionar los N hilos 314, cada bit de un símbolo se transmite como una señal diferencial por uno de un

conjunto de controladores de línea diferencial 310, donde los controladores diferenciales en el conjunto de controladores de la línea 310 están acoplados a diferentes pares de los N hilos. El número de combinaciones disponibles de pares de hilos ( $NC_2$ ) determina el número de señales que pueden transmitirse a través de los N hilos 314. El número de bits de datos 304 que pueden codificarse en un símbolo puede calcularse en función del número de estados de la señalización disponibles para cada intervalo de transmisión de símbolo.

**[0036]** Una impedancia de terminación (típicamente resistiva) acopla cada uno de los *N* hilos 314 a un punto central común 318 en una red de terminación 316. Se apreciará que el estado de la señalización de los *N* hilos 314 refleja una combinación de las corrientes en la red de terminación 316 atribuidas a los controladores diferenciales 310 acoplados a cada hilo. Se apreciará, además, que el punto central 318 es un punto nulo, por lo que las corrientes en la red de terminación 316 se cancelan entre sí en el punto central.

10

15

20

25

30

35

40

45

50

55

60

[0037] El esquema de codificación N! no necesita usar un canal de reloj separado y/o una decodificación sin retorno a cero porque al menos una de las »C2 señales en el enlace pasa entre símbolos consecutivos. Efectivamente, cada transcodificador 306 asegura que se produzca una transición entre cada par de símbolos transmitidos en los N hilos 314 produciendo una secuencia de símbolos en la que cada símbolo es diferente de su símbolo predecesor inmediato. En el ejemplo representado en la FIG. 3, se proporcionan cuatro hilos (N=4), y los 4 hilos pueden transportar  ${}_4C_2 = 6$ señales diferenciales. El transcodificador 306 puede emplear un esquema de correlación para generar símbolos sin procesar para la transmisión en los N hilos 314. El transcodificador 306 puede correlacionar bits de datos 304 con un conjunto de números de transición. Los números de transición se pueden usar para seleccionar símbolos sin procesar para la transmisión en función del valor del símbolo inmediatamente anterior, de modo que el símbolo sin procesar seleccionado sea diferente del símbolo sin procesar anterior. El serializador 308 puede serializar los símbolos sin procesar para obtener una secuencia de símbolos para la transmisión a través de los N hilos 314. En un ejemplo, se puede usar un número de transición para buscar un valor de datos correspondiente al segundo de los símbolos sin procesar consecutivos con referencia al primero de los símbolos sin procesar consecutivos. En el receptor 320, un transcodificador 328 puede emplear una correlación para determinar un número de transición que caracteriza una diferencia entre un par de símbolos sin procesar consecutivos en una tabla de búsqueda, por ejemplo. Los transcodificadores 306, 328 funcionan sobre la base de que cada par consecutivo de símbolos sin procesar incluye dos símbolos diferentes.

**[0038]** El transcodificador 306 en el transmisor 302 puede seleccionar entre N! - 1 estados de la señalización disponibles en cada transición de símbolo. En un ejemplo, un sistema 4! proporciona 4! - 1 = 23 estados de la señalización para el siguiente símbolo a transmitir en cada transición de símbolo. La tasa de bits se puede calcular como  $\log_2(estados\_disponibles)$  por ciclo de reloj de transmisión.

**[0039]** De acuerdo con ciertos aspectos divulgados en el presente documento, la señalización de la doble velocidad de transferencia de datos (DDR) puede emplearse para aumentar el ancho de banda de la interfaz al transmitir dos símbolos en cada período del reloj de transmisión 312. Las transiciones de símbolos se producen tanto en el flanco ascendente como en el flanco descendente del reloj de transmisión en un sistema que utiliza sincronización de la velocidad de transferencia de datos doble (DDR). El total de estados disponibles en el ciclo del reloj de transmisión es  $({}_{N}C_{2}-1)^{2}=(23)^{2}=529$  y el número de bits de datos 304 que pueden transmitirse por símbolo puede calcularse como  $log_{2}(529)=9.047$  bits.

[0040] Un dispositivo receptor 320 recibe la secuencia de símbolos usando un conjunto de receptores de línea 322 donde cada receptor en el conjunto de receptores de línea 322 determina las diferencias en los estados de la señalización en un par de los N hilos 314. En consecuencia, se utilizan  $_NC_2$  receptores, donde N representa el número de hilos. Los  $_NC_2$  receptores 322 producen un número correspondiente de símbolos sin procesar como salidas. En el ejemplo de 4 hilos representado, las señales recibidas en los 4 hilos 314 son procesadas por 6 receptores ( $_4C_2 = 6$ ) para producir una señal de símbolo sin procesar 332 que se proporciona a un CDR 324 y a un deserializador 326. La señal de símbolo sin procesar 332 es representativa del estado de la señalización de los N hilos 314, y el CDR 324 puede procesar la señal de símbolo sin procesar 332 para generar una señal de reloj de recepción 334 que puede ser usada por el deserializador 326.

[0041] La señal de reloj de recepción 334 puede ser una señal de reloj DDR que puede ser usada por un circuito externo para procesar los datos recibidos 330 proporcionados por el transcodificador 328. El transcodificador 328 decodifica un bloque de símbolos recibidos del deserializador 326 comparando cada símbolo con su predecesor inmediato. El transcodificador 328 produce datos de salida 330 correspondientes a los datos 304, proporcionados al transmisor 302.

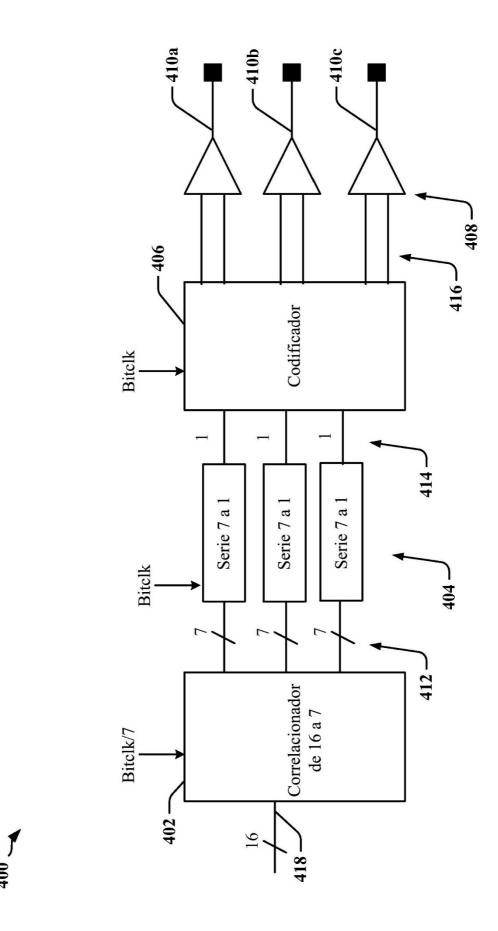

**[0042]** Algunas otras interfaces de varios hilos utilizan la codificación de *N* fases para transmitir datos a través de una pluralidad de hilos. La FIG. 4 es un diagrama 400 que ilustra un ejemplo de un transmisor de codificación por polaridad de *N* fases, *M* hilos configurado para *M*=3 y *N*=3. Los principios y técnicas divulgados para codificadores trifásicos de tres hilos se pueden aplicar en otras configuraciones de codificadores por polaridad de *N* fases y *M* hilos.

65 **[0043]** Cuando se usa la codificación por polaridad de *N* fases, los conectores tales como los hilos de señal 410a, 410b y 410c en un bus de *M* hilos pueden no accionarse, accionarse positivo o accionarse negativo. Un hilo de señal

no accionado 410a, 410b o 410c puede estar en un estado de alta impedancia. Un hilo de señal no accionado 410a, 410b o 410c puede ser arrastrado o accionarse al menos parcialmente hacia un nivel de voltaje que se encuentra sustancialmente a medio camino entre los niveles de voltaje positivo y negativo provistos en los hilos de señal accionados. Un hilo de señal no accionado 410a, 410b o 410c puede no tener corriente que fluya a través de él. En el ejemplo ilustrado en la FIG. 4, un conjunto de controladores 408 puede controlar el estado de cada hilo de señal 410a, 410b y 410c para cada intervalo de transmisión de símbolos, de modo que cada hilo de señal 410a, 410b y 410c puede estar en uno de los tres estados (denotados como +1, - 1 y 0) para un símbolo transmitido. En un ejemplo, los controladores 408 pueden incluir controladores de modo actual a nivel de unidad. En otro ejemplo, los controladores 408 pueden accionar voltajes de polaridad opuesta en dos señales 410a y 410b, mientras que la tercera señal 410c está a alta impedancia y/o está puesta a tierra. Para cada intervalo de transmisión de símbolos, al menos una señal está en el estado no accionado (0), mientras que la cantidad de señales positivas (estado +1) es igual a la cantidad de señales negativas (estado -1), de modo que la suma de la corriente que fluye al receptor es siempre cero. Para cada par de intervalos de transmisión de símbolos consecutivos, al menos un hilo de señal 410a, 410b o 410c tiene un estado diferente en los dos intervalos de transmisión de símbolos.

[0044] En el ejemplo representado en la FIG. 4, los datos de 16 bits 418 se introducen en un correlacionador 402, que correlaciona los datos de entrada 418 con 7 símbolos 412 para transmitir secuencialmente a través de los hilos de señal 410a, 410b y 410c. Los 7 símbolos 412 pueden ser serializados, usando convertidores de paralelo a serie 404, por ejemplo. Un codificador trifásico de 3 hilos 406 recibe los 7 símbolos 412 producidos por el correlacionador un símbolo a la vez y calcula el estado de cada hilo de señal 410a, 410b y 410c para cada intervalo de símbolo. El codificador 406 selecciona los estados de los hilos de señal 410a, 410b y 410c basándose en el símbolo de entrada y los estados anteriores de los hilos de señal 410a, 410b y 410c.

**[0045]** El uso de la codificación de N fases y M hilos permite que se codifique una cantidad de bits en una pluralidad de símbolos, donde los bits por símbolo no son un número entero. En el ejemplo sencillo de sistema de 3 hilos, hay 3 combinaciones disponibles de 2 hilos, que pueden accionares simultáneamente, y 2 posibles combinaciones de polaridad en el par de hilos accionados, produciendo 6 posibles estados. Puesto que cada transición se produce a partir de un estado actual, 5 de los 6 estados están disponibles en cada transición. Se requiere que cambie el estado de al menos un hilo en cada transición. Con 5 estados, pueden codificarse  $\log_2(5) \cong 2,32$  bits por símbolo. En consecuencia, un correlacionador puede aceptar una palabra de 16 bits y convertirla en 7 símbolos ya que 7 símbolos que transportan 2,32 bits por símbolo pueden codificar 16,24 bits. En otras palabras, una combinación de siete símbolos que codifica cinco estados tiene  $5^7$  (78.125) permutaciones. En consecuencia, los 7 símbolos se pueden usar para codificar las  $2^{16}$  (65.536) permutaciones de 16 bits.

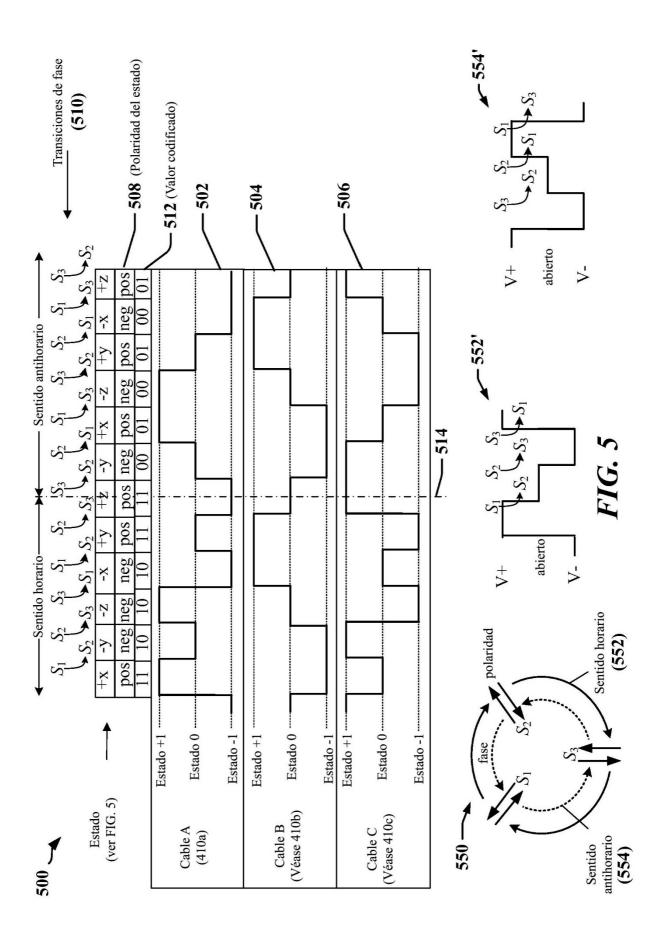

[0046] La FIG. 5 ilustra un ejemplo de señalización 500 que emplea un esquema de codificación de datos de modulación trifásica basado en el diagrama de transición de estado circular 550. De acuerdo con el esquema de codificación de datos, una señal trifásica puede rotar en dos direcciones y puede transmitirse en tres conductores 410a, 410b y 410c. Cada una de las tres señales se acciona independientemente en los conductores 410a, 410b, 410c. Cada una de las tres señales incluye la señal trifásica, estando la señal en cada conductor 410a, 410b y 410c desfasada 120 grados con respecto a las señales en los otros dos conductores 410a, 410b y 410c. En cualquier momento, cada uno de los tres conductores 410a, 410b, 410c está en un estado diferente de los estados {+1, 0, -1}. En cualquier momento, cada uno de los tres conductores 410a, 410b, 410c en un sistema de 3 hilos está en un estado diferente al de los otros dos hilos. Sin embargo, cuando se usan más de tres conductores o hilos, dos o más pares de hilos pueden estar en el mismo estado. El esquema de codificación ilustrado también codifica información en la polaridad de los dos conductores 410a, 410b y/o 410c que son accionados de forma activa a los estados +1 y -1. La polaridad se indica en 508 para la secuencia de estados representados.

[0047] En cualquier estado de fase en el ejemplo ilustrado de tres hilos, exactamente dos de los conductores 410a, 410b, 410c llevan una señal que es efectivamente una señal diferencial para ese estado de fase, mientras que el tercer conductor 410a, 410b o 410c no está accionado. El estado de fase para cada conductor 410a, 410b, 410c puede determinarse por la diferencia de voltaje entre el conductor 410a, 410b o 410c y al menos otro conductor 410a, 410b y/o 410c, o por la dirección del flujo de corriente, o la ausencia de flujo de corriente, en el conductor 410a, 410b o 410c. Como se muestra en el diagrama de transición de estado 550, se definen tres estados de fase (S<sub>1</sub>, S<sub>2</sub> y S<sub>3</sub>). Una señal puede fluir en sentido horario desde el estado de fase S<sub>1</sub> al estado de fase S<sub>2</sub>, del estado de fase S<sub>2</sub> al estado de fase S<sub>3</sub>, y/o del estado de fase S<sub>3</sub> al estado de fase S<sub>1</sub> al estado de fase S<sub>2</sub>, y/o del estado de fase S<sub>2</sub> al estado de fase S<sub>1</sub>. Para otros valores de N, las transiciones entre los N estados pueden definirse opcionalmente de acuerdo con un diagrama de estado correspondiente para obtener la rotación circular entre las transiciones de estado.

[0048] En el ejemplo de un enlace de comunicaciones trifásico de tres hilos, se pueden usar rotaciones en sentido horario (S<sub>1</sub> a S<sub>2</sub>), (S<sub>2</sub> a S<sub>3</sub>) y/o (S<sub>3</sub> a S<sub>1</sub>) en una transición de estado para codificar un 1 lógico, mientras que se pueden usar rotaciones en sentido antihorario (S<sub>1</sub> a S<sub>3</sub>), (S<sub>3</sub> a S<sub>2</sub>) y/o (S<sub>2</sub> a S<sub>1</sub>) en la transición de estado para codificar un 0 lógico. En consecuencia, se puede codificar un bit en cada transición controlando si la señal está "girando" en sentido horario o antihorario. Por ejemplo, un 1 lógico puede codificarse cuando los tres hilos 410a, 410b, 410c pasan del estado de fase S<sub>1</sub> al estado de fase S<sub>2</sub> y un 0 lógico puede codificarse cuando los tres hilos 410a, 410b, 410c pasan del estado de fase S<sub>1</sub> al estado de fase S<sub>3</sub>. En el ejemplo sencillo de tres hilos representado, la dirección de rotación

puede determinarse fácilmente en función de cuál de los tres hilos 410a, 410b, 410c no está accionado antes y después de la transición.

[0049] La información también puede codificarse en la polaridad de los conductores accionados 410a, 410b, 410c o en la dirección del flujo de corriente entre dos conductores 410a, 410b, 410c. Las señales 502, 504 y 506 ilustran los niveles de voltaje aplicados a los conductores 410a, 410b, 410c, respectivamente en cada estado de fase en un enlace trifásico de tres hilos. En cualquier momento, un primer conductor 410a, 410b, 410c está acoplado a un voltaje positivo (+V, por ejemplo), un segundo conductor 410a, 410b, 410c está acoplado a un voltaje negativo (-V, por ejemplo), mientras que el tercer conductor 410a, 410b, 410c puede estar en circuito abierto o de otro modo no accionado. Como tal, un estado de codificación de polaridad puede determinarse por el flujo de corriente entre el primer y el segundo conductores 410a, 410b, 410c. En algunos modos de realización, se pueden codificar dos bits de datos en cada transición de fase. Un decodificador puede determinar la dirección de rotación de fase de la señal para obtener el primer bit, y el segundo bit puede determinarse en función de la diferencia de polaridad entre dos de las señales 502, 504 y 506. El decodificador que tiene una dirección de rotación determinada puede determinar el estado de fase actual y la polaridad del voltaje aplicado entre los dos conectores activos 410a, 410b y/o 410c, o la dirección del flujo de corriente a través de los dos conductores activos 410a, 410b y/o 410c.

**[0050]** En el ejemplo del enlace trifásico de tres hilos descrito en el presente documento, un bit de datos puede codificarse en la rotación, o cambio de fase en un enlace trifásico de 3 hilos, y un bit adicional puede codificarse en la polaridad de los dos hilos accionados. En ciertos modos de realización, se pueden codificar más de dos bits en cada transición de un sistema de codificación trifásico de 3 hilos permitiendo la transición a cualquiera de los estados posibles desde un estado actual. Dadas tres fases rotacionales y dos polaridades para cada fase, se definen 6 estados, de modo que hay 5 estados disponibles desde cualquier estado actual. En consecuencia, puede haber  $\log_2(5) \cong 2,32$  bits por símbolo (transición) y el correlacionador puede aceptar una palabra de 16 bits y convertirla en 7 símbolos.

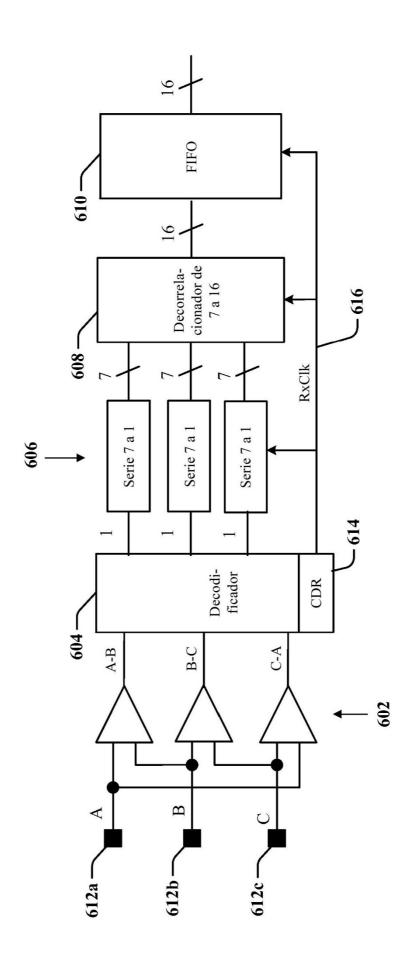

[0051] La FIG. 6 es un dibujo esquemático de bloques 600 que ilustra un ejemplo de un receptor en una interfaz trifásica. Los comparadores 602 y el decodificador 604 están configurados para proporcionar una representación digital del estado de cada una de las tres líneas de transmisión 612a, 612b y 612c, así como el cambio en el estado de las tres líneas de transmisión en comparación con el estado transmitido en el período de símbolo anterior. Como puede verse en el ejemplo ilustrado, el voltaje de cada conector 612a, 612b o 612c se puede comparar con los voltajes de los otros dos conectores 612a, 612b y/o 612c para determinar el estado de cada conector 612a, 612b o 612c, de modo que se puede detectar y decodificar la aparición de una transición mediante el decodificador 604 basándose en las salidas de los comparadores 602. Siete estados consecutivos se ensamblan mediante convertidores serie a paralelo 606, que producen conjuntos de 7 símbolos para ser procesados por el decorrelacionador 608 para obtener 16 bits de datos que pueden almacenarse temporalmente en el FIFO 610. El decodificador 604 puede incluir un circuito CDR 614 configurado para extraer un reloj de recepción 616 de transiciones en los estados de la señalización entre pares consecutivos de símbolos transmitidos.

40 **Tabla 1.**

|        | Amplitud del hilo |      |      | Diferencial Salida Rx |      |      | Salida digital del receptor |       |       |

|--------|-------------------|------|------|-----------------------|------|------|-----------------------------|-------|-------|

| Estado | Α                 | В    | С    | A-B                   | B-C  | C-A  | Rx_AB                       | Rx_BC | Rx_CA |

| +X     | +V                | 0    | +V/2 | +V                    | -V/2 | -V/2 | 1                           | 0     | 0     |

| -x     | 0                 | +V   | +V/2 | -V                    | +V/2 | +V/2 | 0                           | 1     | 1     |

| +y     | +V/2              | +V   | 0    | -V/2                  | +V   | -V/2 | 0                           | 1     | 0     |

| -y     | +V/2              | 0    | +V   | +V/2                  | -V   | +V/2 | 1                           | 0     | 1     |

| +Z     | 0                 | +V/2 | +V   | -V/2                  | -V/2 | +V   | 0                           | 0     | 1     |

| -z     | +V                | +V/2 | 0    | +V/2                  | +V/2 | -V   | 1                           | 1     | 0     |

[0052] La Tabla 1 ilustra el funcionamiento de los receptores diferenciales 602. En el ejemplo, los estados del hilo 522 pueden codificarse en la amplitud de voltaje en los tres hilos 612a, 612b y 612c de modo que el estado +1 de un hilo se represente como un voltaje +V voltios, el estado -1 del hilo es representado como 0 voltios y el estado no accionado se representa o se aproxima como +V/2 voltios. En particular, la Tabla 1 ilustra las salidas de los receptores diferenciales 602 para cada hilo 522 en el sistema de codificación de polaridad trifásica de 3 hilos. Un receptor/decodificador puede configurarse para emitir un código en la salida digital del receptor para cada símbolo decodificado.

**[0053]** Ciertas interfaces de *N* hilos pueden adaptarse para proporcionar un mayor ancho de banda mediante el uso de la sincronización DDR, por lo que se transmite un nuevo símbolo en los flancos ascendente y descendente de un reloj de transmisión. Sin embargo, los circuitos CDR convencionales pueden ser incapaces de responder a la sincronización DDR y/o los circuitos CDR convencionales pueden limitar la velocidad máxima de operación posible de una interfaz de *N*! hilos o de *N* fases.

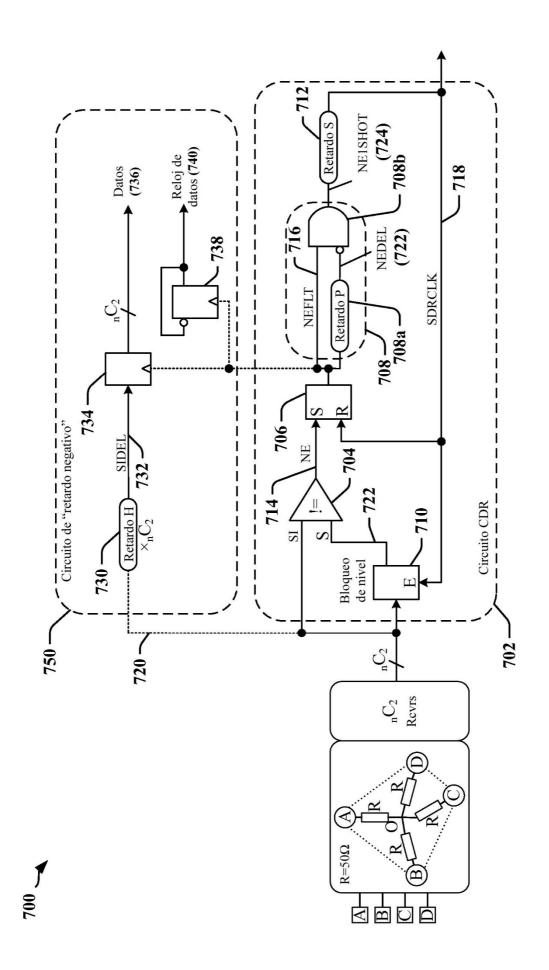

[0054] La FIG. 7 es un diagrama esquemático 700 que ilustra un ejemplo de un circuito CDR 702 que ilustra ciertos

9

50

55

45

5

10

15

20

25

30

35

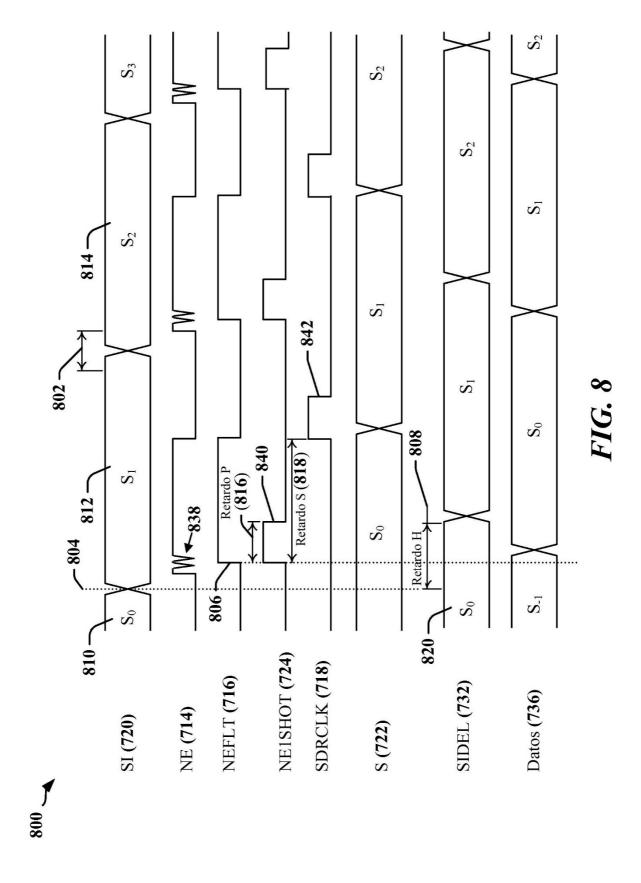

aspectos de la recuperación del reloj desde una interfaz de múltiples hilos, y la FIG. 8 muestra un ejemplo de temporización de ciertas señales generadas por el circuito CDR 702. El circuito CDR 702 puede usarse en un esquema de transmisión de datos de 4 hilos que incorpora información de reloj en símbolos transmitidos, por ejemplo. El circuito CDR 702 incluye un comparador 704, un circuito de bloqueo de establecimiento-restablecimiento 706, un elemento de disparo único 708, un segundo dispositivo de retardo analógico 712 y un circuito de bloqueo de nivel 710. El comparador 704 puede comparar una primera instancia de la primera señal de transición de estado (SI) 720 y una instancia de nivel bloqueado de la primera señal de transición de estado (S) 722, y el comparador 704 emite una señal de comparación (señal NE) 714. El circuito de bloqueo de establecimiento-restablecimiento 706 puede recibir la señal NE 714 del comparador 704 y proporcionar una versión filtrada de la señal de comparación (señal NEFLT) 716. El primer dispositivo de retardo analógico 708a puede recibir la señal NEFLT 716 y producir una instancia retardada de la señal NEFLT 716 como la señal NEDEL 722. Un elemento de compuerta 708b recibe la señal NEFLT 716 y la señal NEDEL 722 y emite la señal NE1SHOT 724. La señal NE1SHOT 724 proporciona un pulso 840 (véase la FIG. 8) que se activa efectivamente por una transición entre los símbolos 810 y 812, donde el pulso tiene una duración 816 determinada por el primer elemento de retardo 708a. La señal de reloj (SDRCLK) 718 generada por el CDR 702 se obtiene a la salida de un segundo dispositivo de retardo analógico 712, que recibe y retarda la señal NE1SHOT 724. Por consiguiente, SDRCLK 718 incluye pulsos 842 que tienen la duración 816 determinada por el primer elemento de retardo 708a. El circuito de bloqueo de establecimiento-restablecimiento 706 se puede restablecer en función del estado del SDRCLK 718. El circuito de bloqueo de nivel 710 recibe la señal de transición SI 720 y emite la instancia de bloqueo de nivel de la señal de transición S 722, donde el circuito de bloqueo de nivel 710 se activa por un flanco en el SDRCLK 718.

10

15

20

25

30

35

40

45

50

55

60

65

[0055] En funcionamiento, cuando se produce una transición entre un símbolo actual (S<sub>0</sub>) 810 y un símbolo siguiente (S<sub>1</sub>) 812, el estado de la señal SI 720 comienza a cambiar. La señal NE 714 realiza una transición a alto cuando el comparador 704 detecta por primera vez una diferencia entre SI 720 y S 722, lo que hace que el circuito de bloqueo de establecimiento-restablecimiento 706 se establezca de forma asíncrona. En consecuencia, la señal NEFLT 716 pasa a un nivel alto, y este estado alto se mantiene hasta que el circuito de bloqueo de establecimiento-restablecimiento 706 se restablece cuando SDRCLK 718 se vuelve alto. El SDRCLK 718 pasa a un estado alto en respuesta retardada al aumento de la señal NEFLT 716, donde el retardo es atribuible al elemento de retardo analógico 712

[0056] A medida que se producen transiciones entre símbolos, pueden producirse uno o más estados intermedios o indeterminados en la señal SI 720 debido a la distorsión entre hilos, el sobreimpulso de la señal, el subimpulso de la señal, la diafonía, etc. Los estados intermedios en SI 720 pueden considerarse como datos no válidos, y estos estados intermedios pueden causar picos 838 en la señal NE 714 a medida que la salida del comparador 704 vuelve a un estado bajo durante cortos períodos de tiempo. Los picos 838 típicamente no afectan a la señal NEFLT 716 emitida por el circuito de bloqueo de establecimiento-restablecimiento 706, porque el circuito de bloqueo de establecimiento-restablecimiento 706 bloquea y/o filtra efectivamente los picos 838 en la señal NE 714 de la señal NEFLT 716.

[0057] El circuito 708 de un disparo emite un estado alto en la señal NE1SHOT 724 después del flanco ascendente de la señal NEFLT 716. El circuito 708 de un solo disparo mantiene la señal NE1SHOT 724 en un estado alto durante el período de retardo P 816 antes de que la señal NE1SHOT 724 regrese al estado bajo. El pulso resultante 740 en la señal NE1SHOT 724 se propaga a la señal SDRCLK 718 después del período de retardo S 818 causado por el elemento analógico de retardo S 712. El estado alto de la señal SDRCLK 718 restablece el circuito de bloqueo de establecimiento-restablecimiento 706, y la señal NEFLT 716 pasa a bajo. El estado alto de la señal SDRCLK 718 también habilita el circuito de bloqueo de nivel 710 y el valor de la señal SI 720 se emite como la señal S 722.

[0058] El comparador 704 detecta cuando la señal S 722 correspondiente al símbolo S<sub>1</sub> 812 coincide con el símbolo S<sub>1</sub> símbolo 812 en la señal SI 720, y la salida del comparador 704 acciona la señal NE 714 baja. El flanco posterior del pulso 840 en la señal NE1SHOT 724 se propaga a la señal SDRCLK 718 después del período de retardo S 818 causado por el elemento de retardo analógico S 712. Cuando se recibe un nuevo símbolo S<sub>2</sub> 814, la señal SI 720 comienza su transición al valor correspondiente al símbolo S<sub>2</sub> 814 después del flanco posterior 842 de la señal SDRCLK 718.

[0059] SDRCLK 718 puede proporcionarse como una salida para sincronizar una o más funciones de un dispositivo receptor. Como se analiza en el presente documento, el SDRCLK 718 incluye una secuencia de pulsos 842 que tiene un ancho de pulso 816 determinado por el primer elemento de retardo 708a, y la temporización de los pulsos 842 con respecto a las transiciones en la señal SI 720 puede determinarse por el segundo elemento de retardo 712. En algunos casos, se pueden proporcionar circuitos adicionales para mejorar el funcionamiento de un receptor que utiliza el circuito CDR 702. En un ejemplo, se puede emplear un circuito de retardo negativo 750 para proporcionar un tiempo de configuración mejorado para los registros 734 que capturan un símbolo de la señal SI 720.

**[0060]** En el circuito de retardo negativo 750,  $_{n}C_{2}$  elementos 730 retardan los datos en las señales SI 720 un período de retardo o valor H 808, produciendo una señal SI retardada (señal SIDEL) 732. Para un enlace de 4 hilos, se pueden usar  $_{n}C_{2} = _{4}C_{2} = 6$  elementos de retardo 730. La señal SIDEL 732 se muestrea mediante un registro o circuito de bloqueo de muestreo 734 que proporciona una salida de datos 736. El circuito de bloqueo de muestreo 734 está sincronizado por el flanco ascendente 806 de NEFLT 716, lo que indica, por ejemplo, que ha comenzado una transición

entre un primer símbolo (S<sub>0</sub>) 810 a un segundo símbolo (S<sub>1</sub>) 812. Como la señal SIDEL 732 retarda la señal SI 720 el período o valor de retardo 808, la señal NEFLT 716 hace que el registro 734 capture una versión retardada del primer símbolo (S<sub>0</sub>) 810. La duración del período o el valor de retardo H 808 proporcionado por los elementos de retardo 730 proporciona efectivamente un tiempo de retención negativo, y el período o el valor de retardo H 808 puede configurarse para satisfacer los requisitos de tiempo de espera o temporización especificados para el registro 734 y/u otros componentes del CDR 702 o circuito de retardo negativo 750.

5

10

45

50

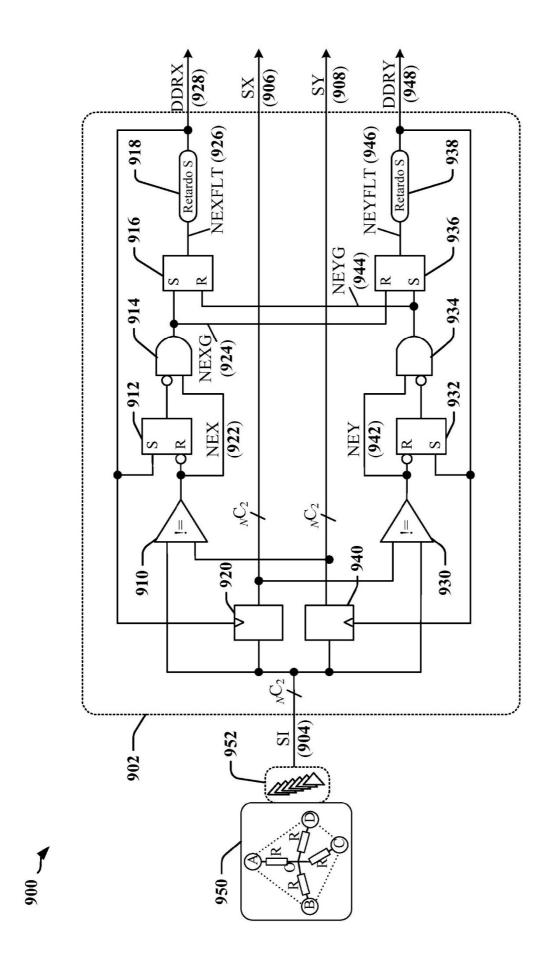

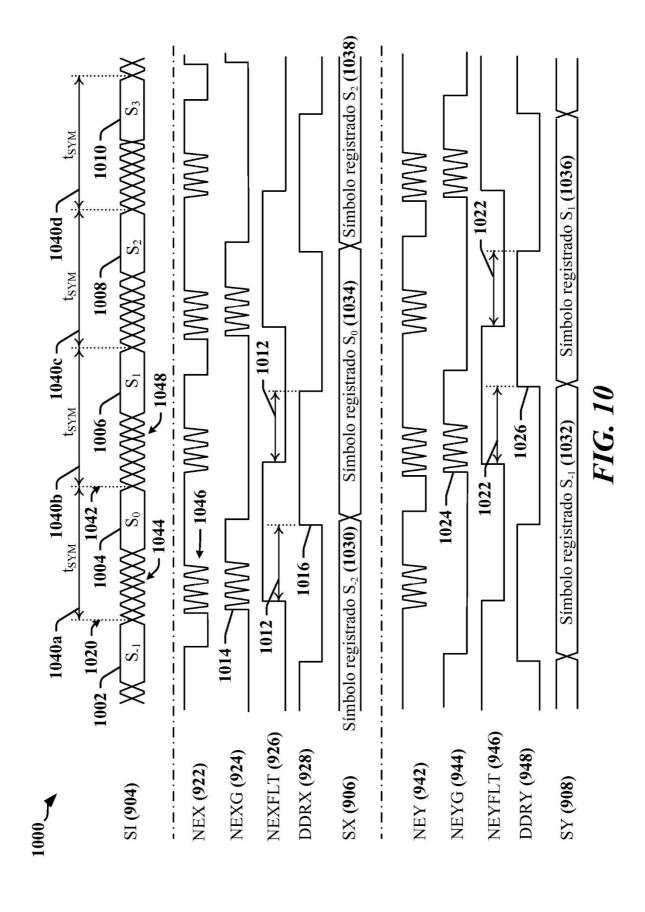

[0061] La FIG. 9 es un diagrama de bloques 900 que ilustra un circuito CDR 902 que está configurado de acuerdo con ciertos aspectos divulgados en el presente documento. La FIG. 10 es un diagrama de temporización 1000 que ilustra el funcionamiento del circuito CDR 902 en condiciones de funcionamiento típicas. El circuito CDR 902 se puede usar con una variedad de interfaces de varios hilos, incluidas las interfaces que usan codificación N!, codificación de N fases y otros esquemas de codificación que usan sincronización de transición de símbolos, incluidas las interfaces que emplean enlaces de comunicación de varios hilos de un solo extremo.

- [0062] En el ejemplo representado en la FIG. 9, el circuito CDR 902 está adaptado para extraer información de reloj de una secuencia de símbolos transmitidos a través de una interfaz N! 950, y para proporcionar un reloj X en la señal DDRX 928 y un reloj Y complementario en la señal DDRY 948. Un circuito externo puede usar un flanco ascendente de la señal DDRX 928 para leer o capturar símbolos pares registrados (SX) 906, mientras que un circuito externo puede usar un flanco ascendente de la señal DDRY 948 para leer o capturar símbolos impares registrados (SY) 908.

La señal DDRX 928 y la señal DDRY 948 pueden generarse a partir de transiciones detectadas entre símbolos sin procesar consecutivos en la señal de entrada (SI) 904. La información del reloj se codifica en las transiciones al final de los períodos de símbolos 1040a-1040d, que corresponden a los símbolos impares 1002, 1006, 1010 y los símbolos pares 1004, 1008.

- 25 [0063] Los símbolos de salida en SX 906 incluyen copias registradas 1034, 1038 de símbolos transmitidos en SI 904 durante los intervalos de transmisión pares ilustrados 1040a, 1040c. Por ejemplo, los símbolos S<sub>0</sub> y S<sub>2</sub> 1004, 1008 son capturados por un conjunto de circuitos de bloqueo o dispositivos de registro 920 del SI 904 y se proporcionan en SX 906 como símbolos S<sub>0</sub> y S<sub>2</sub> registrados 1034, 1038, respectivamente. Los símbolos de salida en SY 908 son copias registradas 1032, 1036 de símbolos transmitidos en SI 904 durante intervalos de transmisión impares, incluidos los intervalos de transmisión impares ilustrados 1040b, 1040d. Por ejemplo, los símbolos S<sub>-1</sub> y S<sub>1</sub> 1002, 1006 son capturados por un conjunto de circuitos de bloqueo o dispositivos de registro 940 desde SI 904 y se proporcionan en SY 908 como símbolos S<sub>-1</sub> y S<sub>1</sub> registrados 1032, 1036, respectivamente. Los dispositivos de registro 920 y 940 proporcionan una versión estabilizada y retardada de los símbolos en SI 904.

- [0064] La generación de la señal DDRX 928 puede entenderse considerando el funcionamiento de ciertos circuitos del CDR 902 después de una transición entre un símbolo impar (S-1) 1002 y un siguiente símbolo par (S0) 1004. La transición se produce al principio 1020 de un período de transmisión de símbolos 1040a, cuando el símbolo S0 1004 puede ser inestable durante una parte 1044 del período de transmisión de símbolos 1040a, debido a diferencias en los tiempos de subida y bajada de los hilos de señal que llevan los símbolos en SI 904, por ejemplo. La lógica de comparación 910 detecta una diferencia entre S0 1004 y una copia registrada 1032 de S-1 1002 proporcionada en la señal SY 908, típicamente usando un comparador acoplado a la salida del comparador que recibe la copia registrada 1032 de S-1 1002 de los registros 940. El funcionamiento de los registros 940 está controlado por los circuitos que generan la señal DDRY 948, y estos registros 940 capturan los símbolos impares 1002, 1006 y proporcionan los símbolos registrados 1032, 1036.

- [0065] Cuando el símbolo actual 1004 es diferente de la copia registrada 1032 de S.1 1002, la señal NEX 922 emitida por la lógica de comparación 910 está en un estado lógico alto. En el primer período de símbolo 1040a, por ejemplo, la señal SY 908 refleja el símbolo registrado S.1 1032 emitido por los registros 940 y, en consecuencia, la lógica de comparación 910 que se utiliza para generar DDRX 928 compara el valor de SI 904 con el símbolo registrado S.1 1032. Al comienzo del primer período de símbolo 1040a, el SI 904 está en un período de transición 1044, ya que cambia del símbolo S.1 1002 a S0 1004 y la señal NEX 922 emitida por la lógica de comparación 910 puede tener algunos picos de transición 1046 hasta que SI 904 logra estabilidad y refleja el verdadero valor de S0 1004, de modo que la señal NEX 922 emitida por la lógica de comparación 910 se encuentra en un estado lógico estable alto.

- [0066] Cuando la señal NEX 922 está en el estado lógico alto, la condición de reinicio se elimina de un primer circuito de bloqueo de establecimiento-restablecimiento 912. Sin embargo, la salida del primer circuito de bloqueo de establecimiento-restablecimiento 912 permanece en un estado lógico bajo porque la señal DDRX 928, que controla la entrada de establecimiento del primer circuito de bloqueo de establecimiento-restablecimiento 912, está en un estado lógico bajo al comienzo 1020 del período de transición 1044. Dado que la salida del primer circuito de bloqueo de establecimiento-restablecimiento 912 está en el estado lógico bajo, la compuerta de la lógica de compuerta 914 está habilitada y, por lo tanto, pasa la señal NEX 922 como la señal NEXG 924. La diferencia detectada por la lógica de comparación 910 entre los símbolos consecutivos S-1 1002 y S<sub>0</sub> 1004 provoca una transición 1014 en la señal NEXG 924 que establece un segundo circuito de bloqueo de establecimiento-restablecimiento 916 y restablece un circuito de bloqueo de establecimiento-restablecimiento 936 correspondiente en el circuito que genera la señal DDRY 948. La lógica de comparación 910 puede detectar una diferencia durante el período de transición 1044 entre los símbolos consecutivos S-1 1002 y S<sub>0</sub> 1004. Una señal NEYG 944 correspondiente controla la entrada de restablecimiento del

segundo circuito de bloqueo de establecimiento-restablecimiento 916, y la señal NEYG 944 está en el estado lógico bajo cuando la señal NEXG 924 está en el estado lógico alto. En consecuencia, la señal NEXFLT 926 proporcionada como la salida del segundo circuito de bloqueo de establecimiento-restablecimiento 916 se acciona en alto.

[0067] La señal DDRX 928 es una versión retardada de la señal NEXFLT 926, debido al retardo 1012 introducido por un primer elemento de retardo 918. El primer elemento de retardo 918 puede configurarse para proporcionar un flanco ascendente en la señal DDRX 928 que se produce después de que el símbolo actual 1004 ha sido estable durante un período de tiempo suficiente para satisfacer el tiempo mínimo de establecimiento especificado para los registros 920. La transición 1016 del estado lógico bajo al estado lógico alto en la señal DDRX 928 activa los registros 920 que capturan el símbolo sin procesar So 1004 de SI 904. La presencia del estado lógico alto en la señal DDRX 928 establece el primer circuito de bloqueo de establecimiento-restablecimiento 912, forzando así la salida de la lógica de compuerta 914 al estado lógico bajo. Se apreciará que la salida del primer circuito de bloqueo de establecimientorestablecimiento 912 puede configurarse para priorizar la entrada de establecimiento sobre la entrada de restablecimiento. Cuando se establece el primer circuito de bloqueo de establecimiento-restablecimiento 912, la señal NEXG 924 se establece en bajo, pero el segundo circuito de bloqueo de establecimiento-restablecimiento 916 mantiene su salida en el estado lógico alto hasta que se restablece mediante el circuito que genera la señal DDRY 948. Como se verá, el restablecimiento del segundo circuito de bloqueo de establecimiento-restablecimiento 916 ocurre cuando la señal NEYG 944 pasa al estado lógico alto después de la detección de una transición desde un símbolo par 1004, 1008 a un símbolo impar 1006, 1010. En consecuencia, la señal NEXFLT 926 permanece en el estado lógico alto durante una duración (tsym) equivalente a aproximadamente un período de transmisión de símbolos.

10

15

20

25

40

45

50

55

60

65

[0068] La transición de la señal DDRX 928 al estado lógico bajo es retardada por el primer elemento de retardo 918 con respecto a la transición correspondiente de la señal NEXFLT 926. La señal DDRX 928 permanece en el estado lógico alto durante una duración ( $t_{\text{SYM}}$ ) equivalente a aproximadamente un período de transmisión de símbolos, que comienza en un punto 1016 cuando  $S_0$  1004 es estable y cae cuando  $S_1$  1006 es estable. En consecuencia, la lógica de comparación 910 no detecta ninguna diferencia entre sus entradas cuando se libera la entrada de establecimiento del primer circuito de bloqueo de 912 y se restablece el primer circuito de bloqueo de 912, habilitando así la lógica de compuerta 914 y la detección de la transición entre  $S_1$  1006 y  $S_2$  1008.

[0069] El circuito que genera la señal DDRX 928 ignora efectivamente la transición entre S<sub>0</sub> 1004 y S<sub>1</sub> 1006, pero está habilitado para responder a la transición entre S<sub>1</sub> 1006 y S<sub>2</sub> 1008 después de que la señal NEXFLT 926 y la señal DDRX 928 se hayan restablecido mediante el circuito que genera la señal DDRY 948. Como se puede ver en el diagrama de temporización 1000, la señal DDRX 926 resultante tiene un ciclo de trabajo aproximado del 50 % y los símbolos pares registrados 1030, 1034 y 1038 se pueden muestrear durante un período de tiempo que es aproximadamente equivalente a dos períodos de transmisión de símbolos (tsym).

[0070] La señal DDRY 948 se genera de una manera que refleja la manera de generar la señal DDRX 926. La generación de la señal DDRY 948 comienza después de una transición entre un símbolo par S<sub>0</sub> 1004 y el siguiente símbolo impar S<sub>1</sub> 1006. La transición ocurre al comienzo 1042 de un período de transmisión de símbolos 1040b, cuando el símbolo S<sub>1</sub> 1006 puede ser inestable durante una porción 1048 del período de transmisión de símbolos 1040b, debido a diferencias en los tiempos de subida y bajada de los hilos de señal que llevan los símbolos en SI 904, por ejemplo. La lógica de comparación 930 detecta una diferencia entre el S<sub>1</sub> 1006 y una copia registrada 1034 del S<sub>0</sub> 1004. La lógica de comparación 930 puede incluir una pluralidad de comparadores que reciben la copia registrada 1034 de S<sub>0</sub> 1004 de los registros 920. El funcionamiento de los registros 920 está controlado por los circuitos que generan la señal DDRX 928, y estos registros 920 capturan los símbolos pares 1004 y 1008 y proporcionan los símbolos registrados 1034 y 1038.

[0071] La lógica de comparación 930 produce una señal NEY 942 que está en el estado lógico alto cuando S<sub>1</sub> 1006 es diferente de la copia registrada 1034 de S<sub>0</sub> 1004. Cuando la señal NEY 942 está en el estado lógico alto, la condición de restablecimiento se elimina de un tercer circuito de bloqueo de establecimiento-restablecimiento 932. Sin embargo, la salida del tercer circuito de bloqueo de establecimiento 932 permanece baja porque la señal DDRY 948 que controla la entrada de establecimiento del tercer circuito de bloqueo de establecimiento-restablecimiento 932 está en un estado lógico bajo al comienzo 1042 del período de transición 1048. La salida lógica baja del tercer circuito de bloqueo de establecimiento-restablecimiento 932 habilita la lógica de compuerta 934, que por lo tanto pasa la señal NEY 942 como la señal NEYG 944. Por lo tanto, la diferencia detectada por la lógica de comparación 930 entre los símbolos consecutivos S<sub>0</sub> 1004 y S<sub>1</sub> 1006 provoca una transición 1024 en la señal NEYG 944 a un nivel lógico alto que establece un cuarto circuito de bloqueo de establecimiento-restablecimiento 936 y restablece el segundo circuito de bloqueo de establecimiento-restablecimiento 916 en el circuito que genera la señal DDRX 928. La señal NEXG 924 correspondiente controla la entrada de establecimiento del cuarto circuito de bloqueo de establecimiento-restablecimiento 936, y la señal NEXG 924 está en el estado lógico bajo cuando la señal NEYG 944 está en el estado lógico alto. En consecuencia, la señal NEYFLT 946 proporcionada como la salida del cuarto circuito de bloqueo de establecimiento-restablecimiento-restablecimiento 936 es accionada al estado lógico alto.

[0072] La señal DDRY 948 es una versión retardada de la señal NEYFLT 946, donde la señal DDRY 948 es retardada por el período de retardo 1022 introducido por el segundo elemento de retardo 938. El segundo elemento de retardo 938 puede configurarse para proporcionar un flanco ascendente en la señal DDRY 948 que se produce

después de que S<sub>1</sub> 1006 ha sido estable durante un período de tiempo suficiente para satisfacer el tiempo de establecimiento mínimo especificado para los registros 940. El segundo elemento de retardo 938 puede coincidir con el primer elemento de retardo 918 en la circuitería que genera la señal DDRX 928. La transición 1026 del estado lógico bajo al estado lógico alto en la señal DDRY 948 activa los registros 940, que capturan S<sub>1</sub> 1006 de SI 904. Un estado lógico alto en la señal DDRY 948 establece el tercer circuito de bloqueo de establecimiento-restablecimiento 932, forzando así la salida de la lógica de compuerta 934 al estado lógico bajo. Se apreciará que la salida del tercer circuito de bloqueo de establecimiento-restablecimiento 932 puede configurarse para priorizar la entrada de establecimiento sobre la entrada de restablecimiento. Cuando se establece el tercer circuito de bloqueo de establecimiento-restablecimiento 932, la señal NEYG 944 pasa a bajo, pero el cuarto circuito de bloqueo de establecimiento-restablecimiento 936 mantiene su salida en el estado lógico alto hasta que el circuito que genera la señal DDRX 928 restablece su salida. Como se describió anteriormente, el restablecimiento del cuarto circuito de bloqueo de establecimiento-restablecimiento 936 ocurre cuando la señal NEXG 924 pasa al estado lógico alto después de la detección de una transición desde un símbolo impar 1006 a un símbolo par 1008. Por consiguiente, la señal NEYFLT 946 permanece en el estado lógico alto durante la duración de aproximadamente un período de transmisión de símbolo (tsym).

10

15

20

25

30

35

40

45

50

55

60

65

[0073] La transición de la señal DDRY 948 al estado lógico bajo es retardada por el segundo elemento de retardo 938 con respecto a la transición correspondiente de la señal NEYFLT 946. La señal DDRY 948 permanece en el estado lógico alto durante la duración de aproximadamente un período de transmisión de símbolos (tsym), que comienza en un punto 1026 cuando S1 1006 es estable y cae cuando S2 1008 es estable. En consecuencia, los circuitos que generan la señal DDRY 948 ignoran efectivamente la transición entre S1 1006 y S2 1008, y responden a la siguiente transición después de que la señal NEYFLT 946 y la señal DDRY 948 han sido restablecidas por el circuito que genera la señal DDRX 928. Como se puede ver en el diagrama de temporización 1000, la señal DDRY 946 resultante tiene un ciclo de trabajo aproximado del 50 % y está aproximadamente desfasada 180° con la señal DDRX 926, y los símbolos impares registrados 1032 y 1036 están disponibles para muestreo durante aproximadamente dos períodos de transmisión de símbolos (tsym).

[0074] Después de un restablecimiento del sistema, uno o más de los registros 920, 940 y los circuitos de bloqueo de establecimiento-restablecimiento 912, 916, 932, 936 pueden inicializarse para garantizar que el circuito CDR 902 alcance una condición operativa de "estado estable" y produzca un reloj de salida confiable señales 928 y 948. En un ejemplo, el circuito CDR 902 puede inicializarse controlando la condición de inicio del segundo y cuarto circuitos de bloqueo de establecimiento-restablecimiento 916 y 936 que producen esa señal DDRX 928 y la señal DDRY 948, respectivamente. Un restablecimiento del sistema puede hacer que el primer circuito de bloqueo de establecimientorestablecimiento 916 se mantenga en una condición de "Restablecimiento" forzado durante un período de tiempo que excede el período de retardo (Retardo S 1012) proporcionado por el primer elemento de retardo 918, mientras que causa el segundo circuito de bloqueo de establecimiento-restablecimiento 936 se mantendrá en una condición forzada de "Establecimiento" durante un período de tiempo que excede el período de retardo (Retardo S 1022) proporcionado por el segundo elemento de retardo 938. En el punto en que se elimina la condición de restablecimiento del sistema, la señal NEXFLT 926 y la señal DDRX 928 están en el estado lógico bajo, mientras que la señal NEYFLT 946 y la señal DDRY 948 están en el estado lógico alto. Durante al menos la duración del Retardo S 1022, la salida del tercer circuito de bloqueo de establecimiento-restablecimiento 932 se fuerza al estado lógico alto, haciendo que la lógica de compuerta 934 bloquee la señal NEY 942. La señal NEY 942 se pasa solo después de que el cuarto circuito de bloqueo de establecimiento-restablecimiento 936 se restablece mediante el funcionamiento del circuito que genera la señal DDRX 928, y la señal DDRY 948 pasa a bajo posteriormente después de expirar el Retardo S 1022 asociado con el elemento de retardo 938. Se apreciará que la señal NEYG 944 está en el estado lógico bajo hasta que la señal DDRY 948 haya pasado al estado lógico bajo y la lógica de comparación 930 haya detectado una diferencia entre el valor del símbolo capturado por los registros 920 y el valor del símbolo sin procesar actual en SI 904.

[0075] La señal DDRX 928 está en el estado lógico bajo cuando se elimina el restablecimiento del sistema, y permanece en el estado lógico bajo durante al menos el período de retardo proporcionado por el primer elemento de retardo 918. En consecuencia, la salida del primer circuito de bloqueo de establecimiento-restablecimiento 912 puede estar en el estado lógico bajo al eliminar el restablecimiento del sistema porque la señal DDRX 928 continúa manteniendo la entrada "Establecimiento" del primer circuito de bloqueo de establecimiento-restablecimiento 912 en una condición baja y el primer circuito de bloqueo de establecimiento-restablecimiento 912 puede haberse inicializado con su salida en el estado lógico bajo, o porque la lógica de comparación 910 puede haber restablecido el primer circuito de bloqueo de establecimiento-restablecimiento 912 durante el tiempo en que se aplicó el restablecimiento del sistema. Incluso si la salida del primer circuito de bloqueo de establecimiento-restablecimiento 912 está en el estado lógico alto después de que se elimine el restablecimiento del sistema, la primera detección de la diferencia entre el valor almacenado en los registros de símbolo impar 940 y el símbolo actual en SI 904 por la lógica de comparación 910 restablece el primer circuito de bloqueo de establecimiento-restablecimiento 912, permitiendo que la señal NEX 922 controle el valor de NEXG 924. Cuando la lógica de comparación 910 detecta una diferencia entre el valor almacenado en los registros de símbolos impares 940 y el símbolo actual en SI 904, se establece el segundo circuito de bloqueo de establecimiento-restablecimiento 916 y se libera el cuarto circuito de bloqueo de establecimiento-restablecimiento 936, causando así que la señal DDRX 928 pase al estado lógico alto y la señal DDRY 948 pase al estado lógico bajo después del período de retardo S 1022. El flanco ascendente de la señal DDRX 928 activa los registros de símbolos pares 912 para capturar el símbolo actual en SI 904. En este punto, el CDR 902 procede como

se describe para la operación en estado estacionario.

[0076] Se apreciará que el CDR 902 puede configurarse para provocar otras preconfiguraciones de condiciones iniciales de los registros 920, 940 y/o de los circuitos de bloqueo de establecimiento-restablecimiento 912, 916, 932, 936 en respuesta a un restablecimiento del sistema. Por ejemplo, se puede usar una estrategia de arranque diferente si el primer y segundo elementos de retardo 918 y 938 proporcionan períodos de retardo sustancialmente diferentes, si se desean diferentes ciclos de trabajo para las señales DDRX y DDRY 928, 948 y/o se basan en otros requisitos, incluidos los requisitos relacionados con las señales de reloj o control proporcionadas a circuitos y dispositivos externos.

10

5

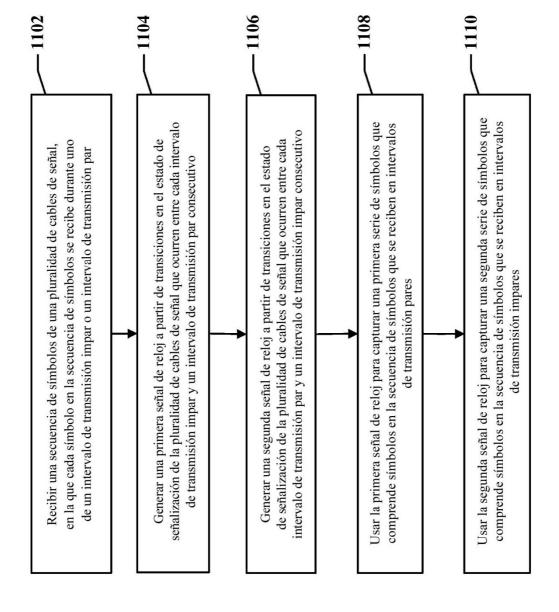

[0077] La FIG. 11 es un diagrama de flujo 1100 que ilustra un procedimiento para comunicaciones de datos en un enlace de comunicaciones de *N* hilos. En la etapa 1102, se puede recibir una secuencia de símbolos de una pluralidad de hilos de señal. Cada símbolo en la secuencia de símbolos se recibe durante uno de un intervalo de transmisión impar o un intervalo de transmisión par.

15

[0078] En la etapa 1104, se puede generar una primera señal de reloj a partir de transiciones en el estado de la señalización de la pluralidad de hilos de señal que ocurren entre cada intervalo de transmisión impar y un intervalo de transmisión par consecutivo.

20

[0079] En la etapa 1106, se genera una segunda señal de reloj a partir de transiciones en el estado de la señalización de la pluralidad de hilos de señal que se producen entre cada intervalo de transmisión par y un intervalo de transmisión impar consecutivo.

25

**[0080]** En la etapa 1108, la primera señal de reloj puede usarse para capturar un primer conjunto de símbolos que incluye símbolos en la secuencia de símbolos recibidos en intervalos de transmisión pares.

30

**[0081]** En la etapa 1110, la segunda señal de reloj puede usarse para capturar un segundo conjunto de símbolos que incluye símbolos en la secuencia de símbolos recibidos en intervalos de transmisión impares.

[0082] Cada intervalo de transmisión impar puede estar precedido inmediatamente por un primer intervalo de transmisión par e inmediatamente sucedido por un segundo intervalo de transmisión par.

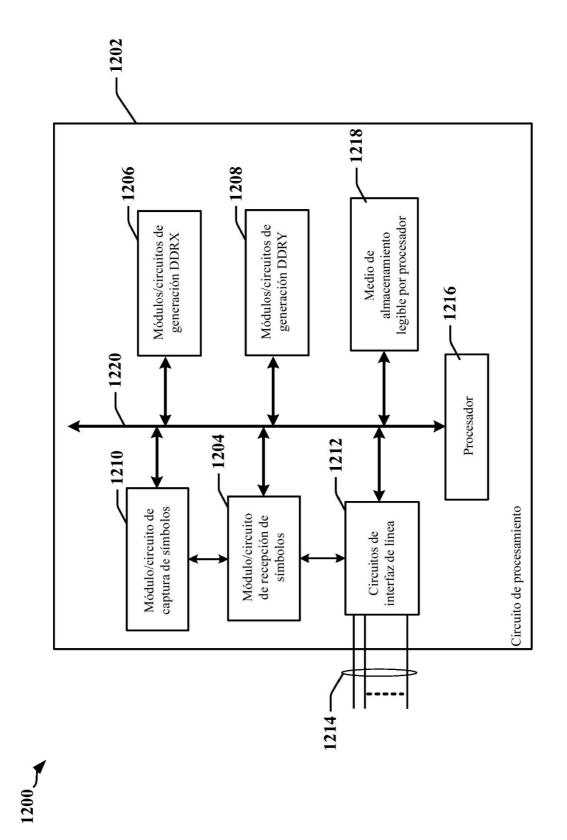

35