# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11) Número de publicación: 2 797 150

51 Int. CI.:

**G06T 3/00** (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

T3

86) Fecha de presentación y número de la solicitud internacional: 02.12.2016 PCT/US2016/064769

(87) Fecha y número de publicación internacional: 20.07.2017 WO17123341

(96) Fecha de presentación y número de la solicitud europea: 02.12.2016 E 16816537 (1)

(97) Fecha y número de publicación de la concesión europea: 11.03.2020 EP 3403236

(54) Título: Sistemas y procedimientos para renderizar múltiples niveles de detalle

(30) Prioridad:

12.01.2016 US 201614993760

Fecha de publicación y mención en BOPI de la traducción de la patente: **01.12.2020**

(73) Titular/es:

QUALCOMM INCORPORATED (100.0%) 5775 Morehouse Drive San Diego, CA 92121-1714, US

(72) Inventor/es:

NGUYEN, PHI HUNG **y** BI, NING

(74) Agente/Representante:

FORTEA LAGUNA, Juan José

#### **DESCRIPCIÓN**

Sistemas y procedimientos para renderizar múltiples niveles de detalle

#### 5 CAMPO DE LA DIVULGACIÓN

[0001] La presente divulgación se refiere en general a dispositivos electrónicos. Más específicamente, la presente divulgación se refiere a sistemas y procedimientos para renderizar múltiples niveles de detalle.

#### 10 ANTECEDENTES

15

25

30

35

50

[0002] Algunos dispositivos electrónicos (por ejemplo, teléfonos inteligentes, ordenadores, televisores, automóviles, sistemas de videojuegos, reproductores multimedia, cámaras, teléfonos celulares, cámaras personales, descodificadores, proyectores, monitores, etc.) muestran imágenes. Por ejemplo, un teléfono inteligente puede capturar y/o procesar imágenes fijas y/o de vídeo. El procesamiento de imágenes puede requerir una cantidad relativamente grande de tiempo, memoria y recursos energéticos. Los recursos demandados pueden variar de acuerdo con la complejidad del procesamiento.

[0003] El procesamiento de grandes cantidades de datos de imágenes puede ser particularmente difícil. Por ejemplo, grandes cantidades de datos de imágenes pueden requerir cantidades relativamente grandes de recursos, como energía, tiempo, ancho de banda del procesador, memoria y/o costes monetarios. Como puede observarse a partir de este análisis, pueden ser beneficiosos los sistemas y procedimientos que mejoren el procesamiento de imágenes.

#### **BREVE EXPLICACIÓN**

[0004] Se describe un dispositivo electrónico. El dispositivo electrónico incluye un procesador configurado para renderizar una primera zona de una imagen. El procesador también está configurado para renderizar una segunda zona de la imagen. La primera zona tiene un mayor nivel de detalle teselado que la segunda zona. El procesador está configurado además para presentar la primera zona y la segunda zona en al menos una ventana del vehículo. El dispositivo electrónico puede ser al menos parte de un módulo extraíble en un vehículo.

[0005] El dispositivo electrónico puede incluir al menos una pantalla. El procesador puede configurarse para enviar la primera zona y la segunda zona a la al menos una pantalla para presentar la primera zona y la segunda zona. La al menos una pantalla puede ser un proyector de ventana o un panel de pantalla de ventana integrado.

[0006] El procesador puede configurarse para presentar la primera zona en una primera ventana y presentar la segunda zona en una segunda ventana. La primera ventana puede ser un parabrisas delantero y la segunda ventana puede ser otra ventana de un vehículo.

[0007] El procesador puede configurarse para presentar la primera zona en una primera sección de una ventana y puede ser configurado para presentar la segunda zona en una segunda sección de la ventana. La primera sección puede ser una sección lateral de un parabrisas y la segunda sección puede ser otra sección lateral del parabrisas. La primera sección puede ser una primera barra horizontal a través de un parabrisas y la segunda sección puede ser una segunda barra horizontal a través del parabrisas.

[0008] El procesador puede configurarse para realizar seguimiento de los ojos. El procesador también puede configurarse para renderizar la primera zona y la segunda zona basándose en el seguimiento de los ojos. El procesador puede configurarse para realizar un seguimiento de los ojos para múltiples usuarios. El procesador puede priorizar la renderización de zonas basándose en el seguimiento de los ojos.

[0009] El procesador puede configurarse para renderizar una tercera zona. La tercera zona puede tener un nivel de detalle teselado más bajo que la primera zona y la segunda zona. El procesador puede configurarse para presentar la tercera zona en al menos una ventana del vehículo.

[0010] También se describe un procedimiento realizado por un dispositivo electrónico. El procedimiento incluye renderizar una primera zona de una imagen. El procedimiento también incluye renderizar una segunda zona de la imagen. La primera zona tiene un mayor nivel de detalle teselado que la segunda zona. El procedimiento incluye además presentar la primera zona y la segunda zona en al menos una ventana del vehículo.

[0011] También se describe un producto de programa informático. El producto de programa informático incluye un medio tangible no transitorio legible por ordenador con instrucciones. Las instrucciones incluyen código para hacer que un dispositivo electrónico renderice una primera zona de una imagen. Las instrucciones también incluyen código para hacer que el dispositivo electrónico renderice una segunda zona de la imagen. La primera zona tiene un mayor nivel de detalle teselado que la segunda zona. Las instrucciones incluyen además el código para hacer que el dispositivo electrónico presente la primera zona y la segunda zona en al menos una ventana del vehículo.

# 2

[0012] También se describe un aparato. El aparato incluye medios para renderizar una primera zona de una imagen. El aparato también incluye medios para renderizar una segunda zona de la imagen. La primera zona tiene un mayor nivel de detalle teselado que la segunda zona. El aparato incluye además medios para presentar la primera zona y la segunda zona en al menos una ventana del vehículo.

# **BREVE DESCRIPCIÓN DE LOS DIBUJOS**

5

65

|    | [0013] |                                                                                                                                                                                                              |

|----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10 |        | La Figura 1 es un diagrama de bloques que ilustra una configuración de un dispositivo electrónico en el que se pueden implementar sistemas y procedimientos para renderizar múltiples niveles de detalle;    |

| 15 |        | la Figura 2 es un diagrama de flujo que ilustra una configuración de un procedimiento para renderizar múltiples niveles de detalle;                                                                          |

|    |        | La Figura 3 es un diagrama de bloques que ilustra una configuración de un dispositivo electrónico en el que se pueden implementar sistemas y procedimientos para renderizar múltiples niveles de detalle;    |

| 20 |        | la Figura 4 es un diagrama que ilustra un ejemplo de una memoria intermedia de tramas no uniforme;                                                                                                           |

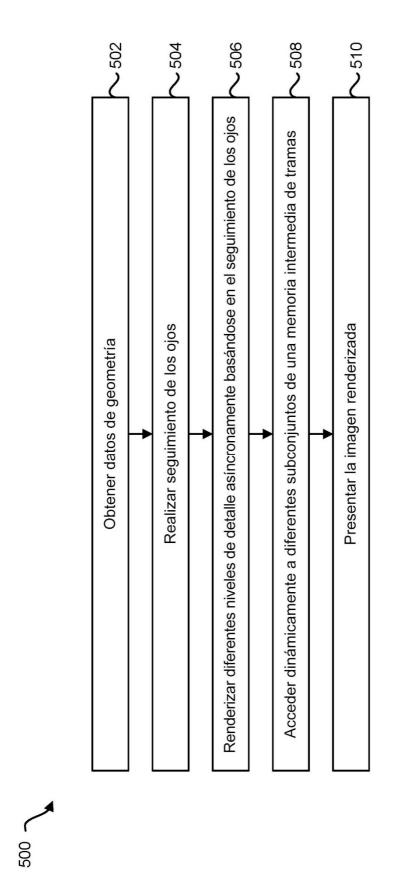

|    |        | la Figura 5 es un diagrama de flujo que ilustra una configuración más específica de un procedimiento para renderizar múltiples niveles de detalle;                                                           |

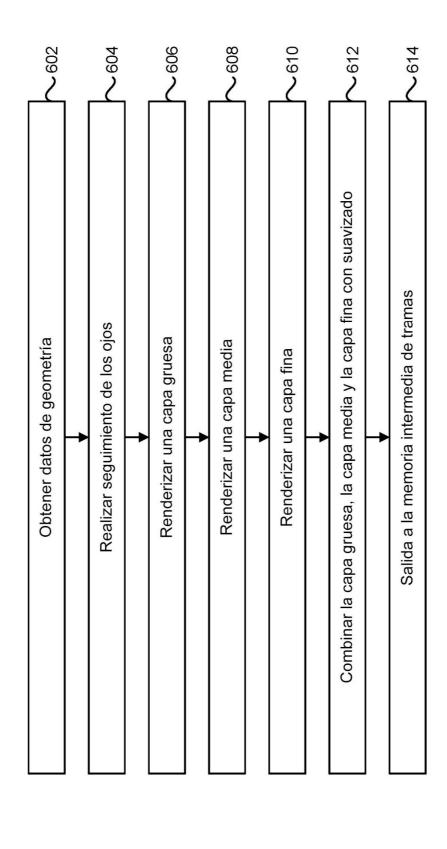

| 25 |        | la Figura 6 es un diagrama de flujo que ilustra un ejemplo de procedimiento para renderización con resolución variable;                                                                                      |

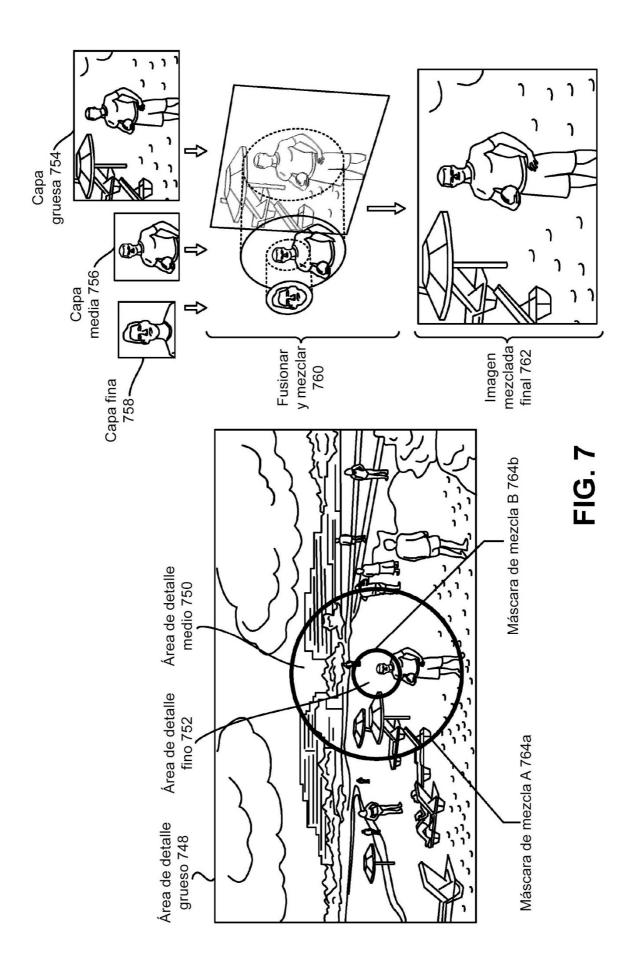

|    |        | la Figura 7 ilustra un ejemplo de renderización con resolución variable;                                                                                                                                     |

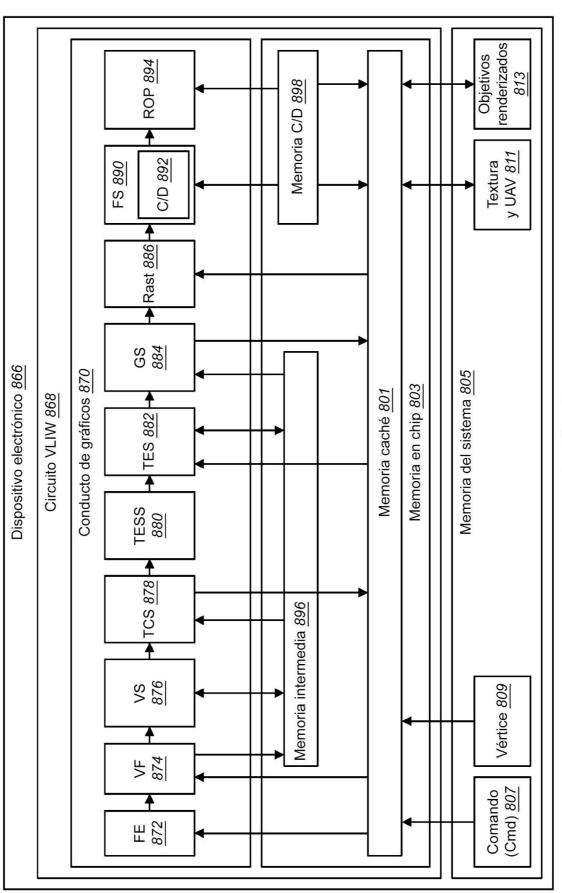

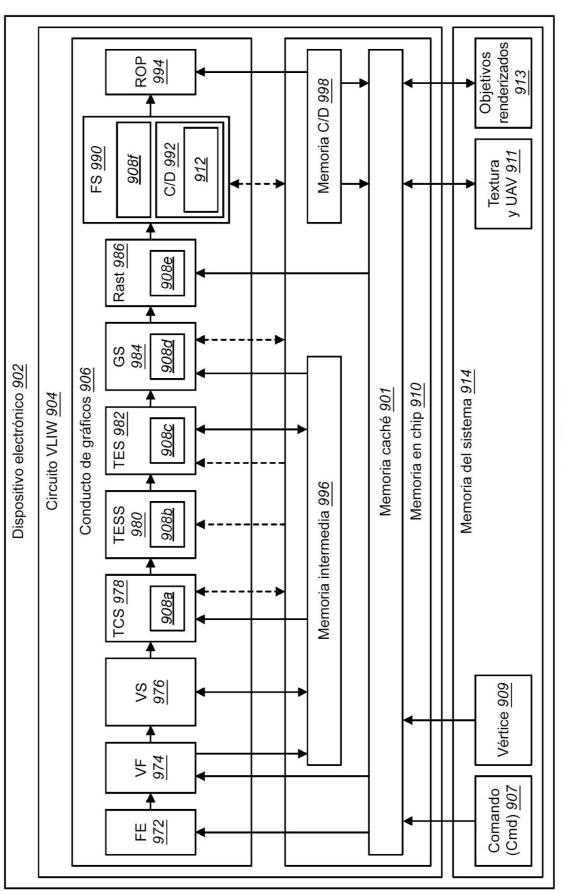

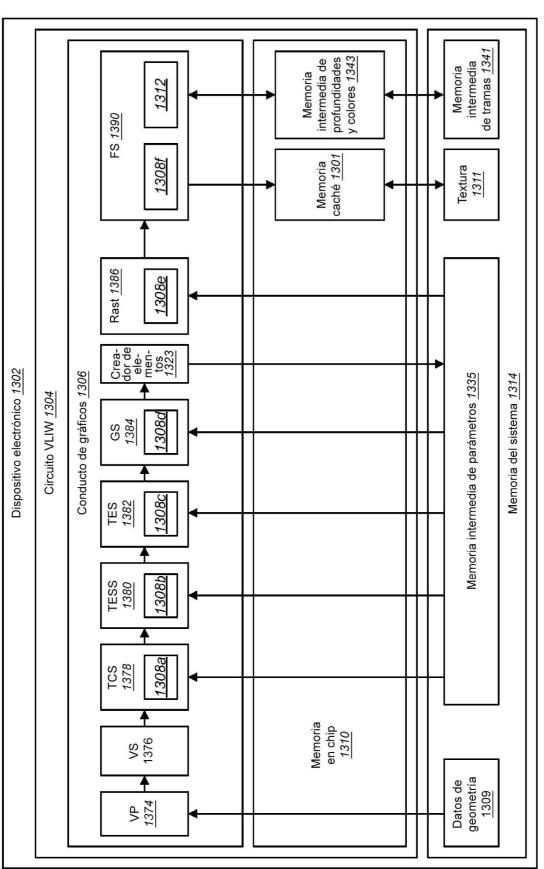

| 30 |        | la Figura 8 es un diagrama de bloques que ilustra un ejemplo de un dispositivo electrónico que incluye un circuito de palabra de instrucción muy larga (VLIW);                                               |

|    |        | la Figura 9 es un diagrama de bloques que ilustra un ejemplo de los sistemas y procedimientos divulgados en el presente documento implementados en la arquitectura descrita en relación con la Figura 8;     |

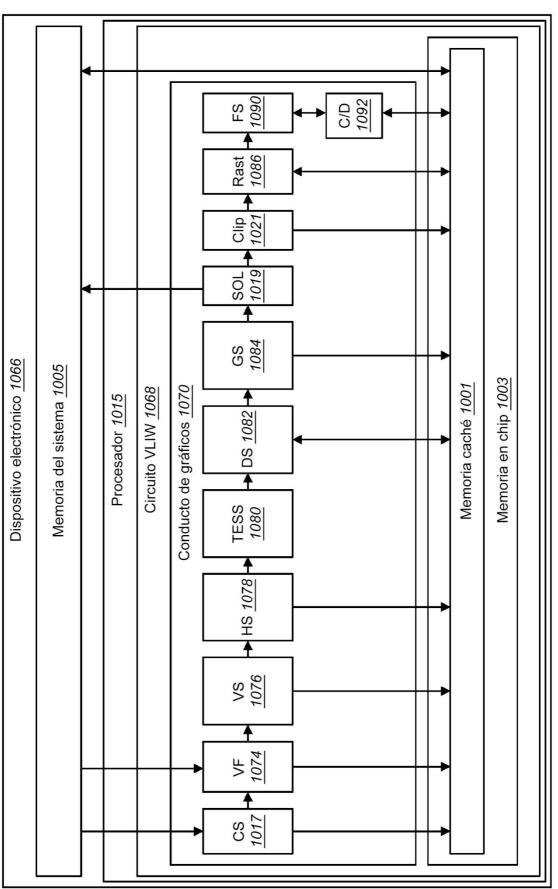

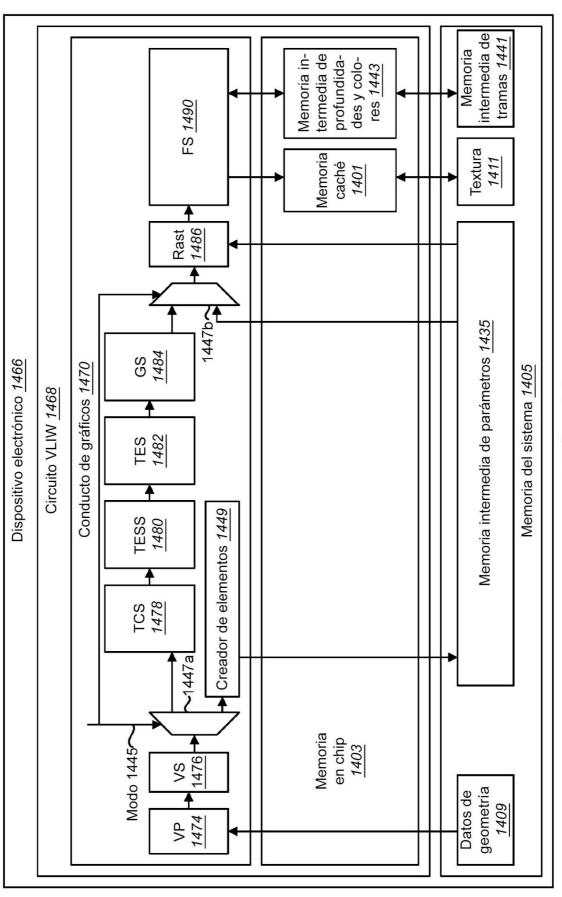

| 35 |        | la Figura 10 es un diagrama de bloques que ilustra otro ejemplo de un dispositivo electrónico que incluye un circuito de palabra de instrucción muy larga (VLIW);                                            |

| 40 |        | la Figura 11 es un diagrama de bloques que ilustra otro ejemplo de los sistemas y procedimientos divulgados en el presente documento implementados en la arquitectura descrita en relación con la Figura 10; |

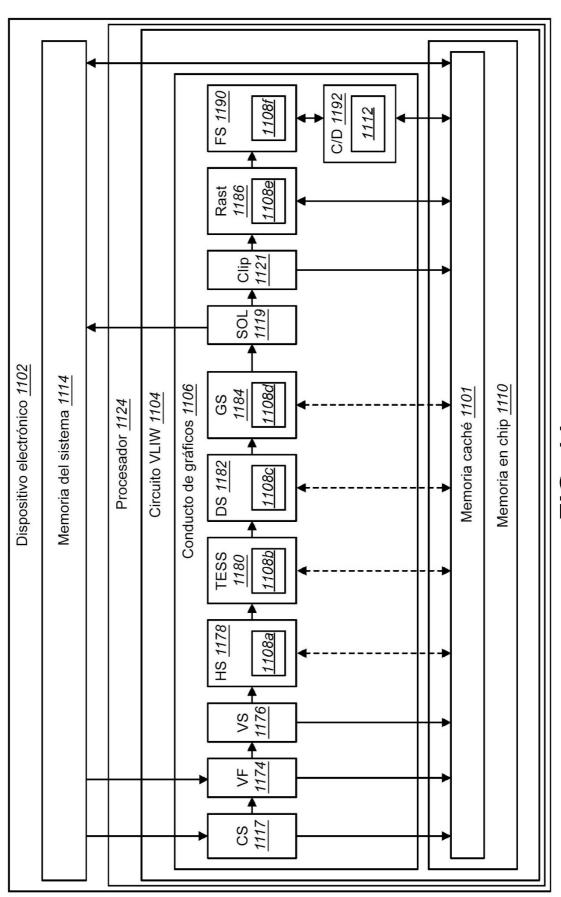

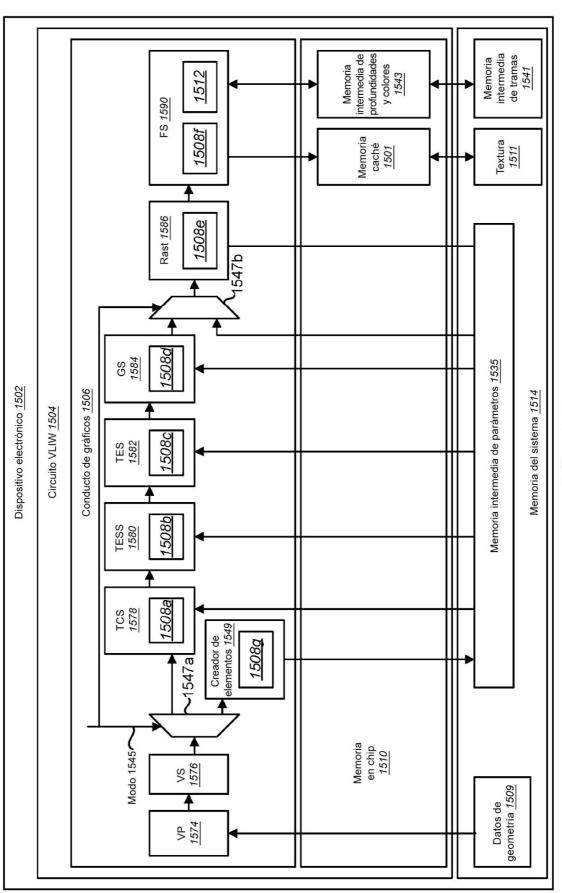

|    |        | la Figura 12 es un diagrama de bloques que ilustra otro ejemplo de un dispositivo electrónico que incluye un circuito de palabra de instrucción muy larga (VLIW);                                            |

| 45 |        | la Figura 13 es un diagrama de bloques que ilustra un ejemplo de los sistemas y procedimientos divulgados en el presente documento implementados en la arquitectura descrita en relación con la Figura 12;   |

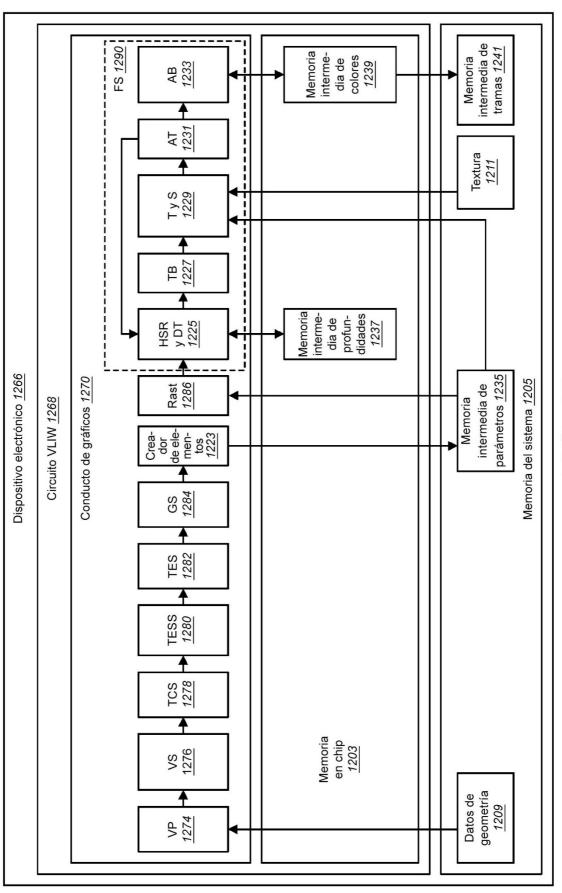

|    |        | la Figura 14 es un diagrama de bloques que ilustra otro ejemplo de un dispositivo electrónico que incluye un circuito de palabra de instrucción muy larga (VLIW);                                            |

| 50 |        | la Figura 15 es un diagrama de bloques que ilustra un ejemplo de los sistemas y procedimientos divulgados en el presente documento implementados en la arquitectura descrita en relación con la Figura 14;   |

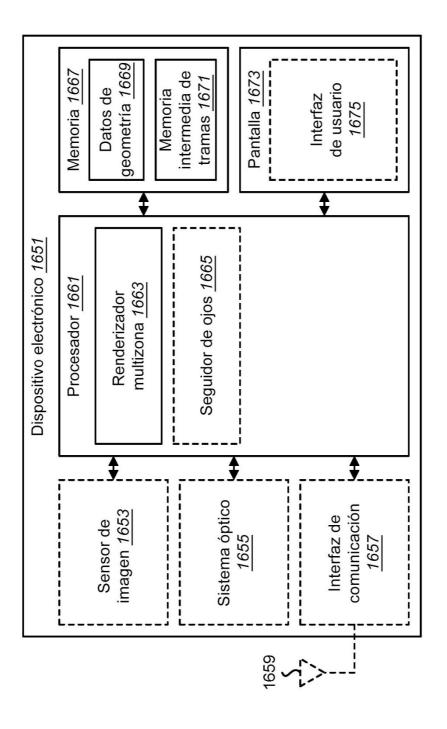

| 55 |        | la Figura 16 es un diagrama de bloques que ilustra una configuración de un dispositivo electrónico en el que pueden implementarse sistemas y procedimientos para renderizar múltiples zonas;                 |

|    |        | la Figura 17 es un diagrama de flujo que ilustra un procedimiento para renderizar múltiples zonas;                                                                                                           |

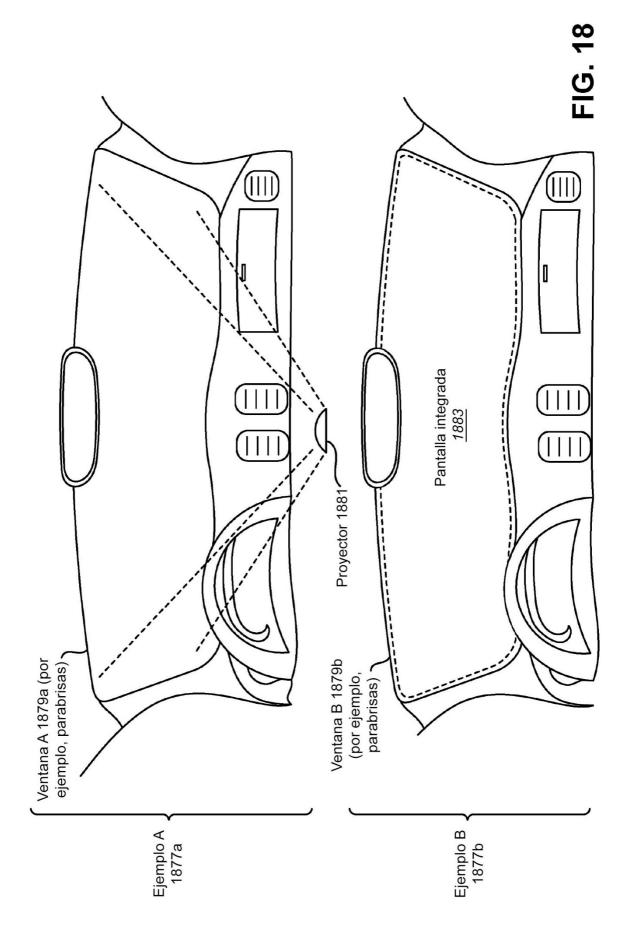

|    |        | la Figura 18 es un diagrama que ilustra algunos ejemplos de pantallas de ventana;                                                                                                                            |

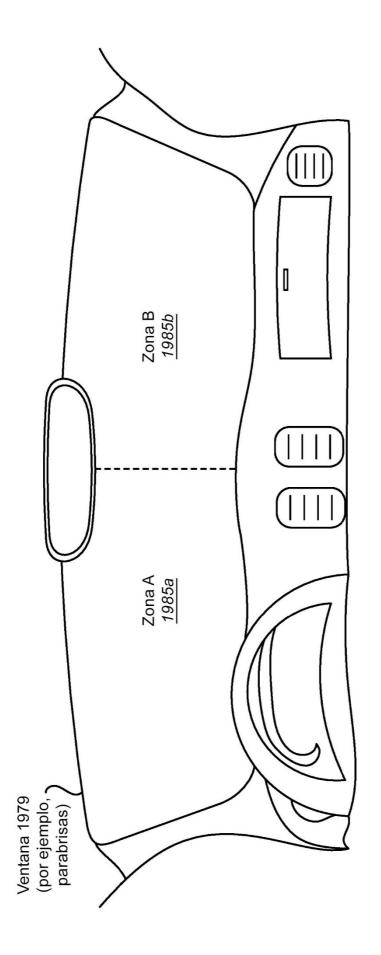

| 60 |        | la Figura 19 es un diagrama que ilustra un ejemplo de zonas en una ventana;                                                                                                                                  |

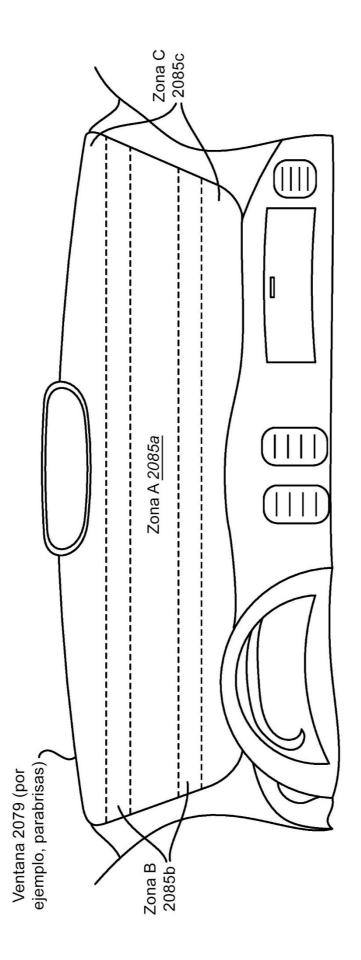

|    |        | la Figura 20 es un diagrama que ilustra otro ejemplo de zonas en una ventana;                                                                                                                                |

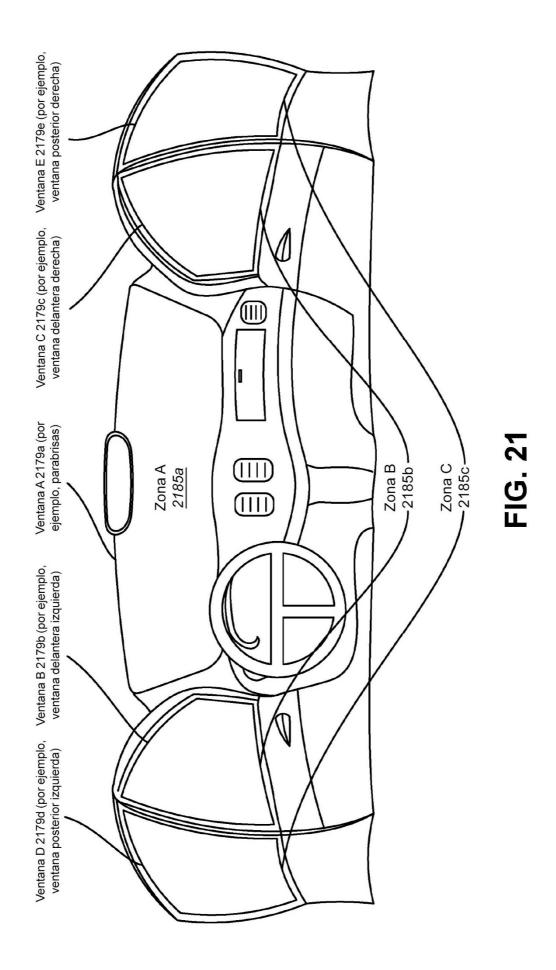

| 65 |        | la Figura 21 es un diagrama que ilustra otro ejemplo de zonas en múltiples ventanas;                                                                                                                         |

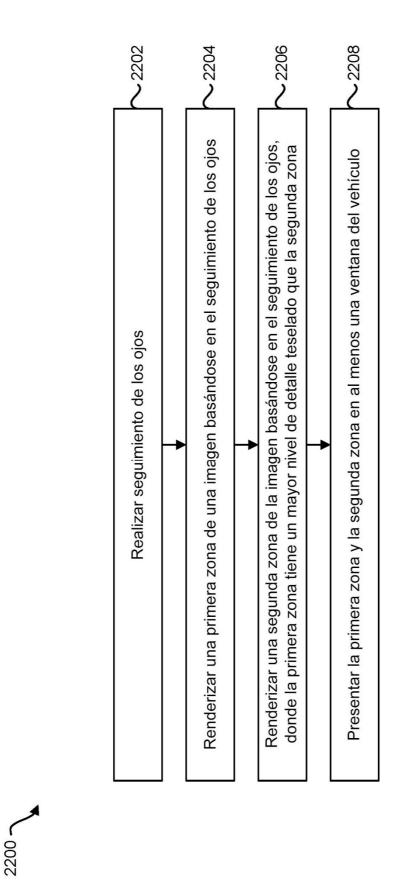

la Figura 22 es un diagrama de flujo que ilustra una configuración más específica de un procedimiento para renderizar múltiples zonas;

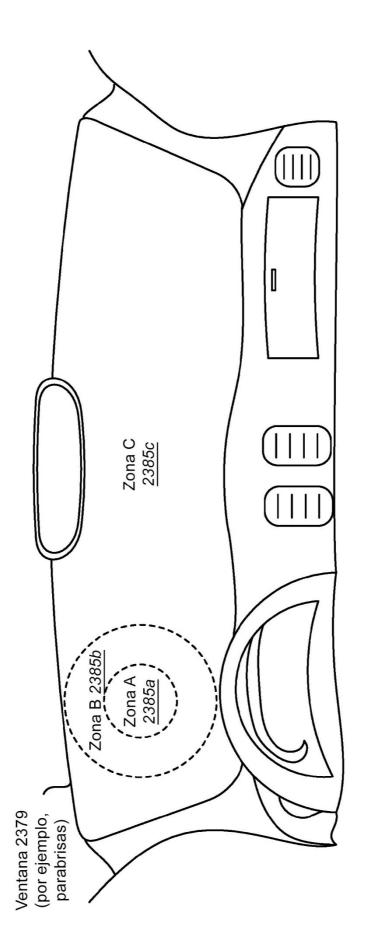

la Figura 23 es un diagrama que ilustra otro ejemplo de zonas en una ventana; y

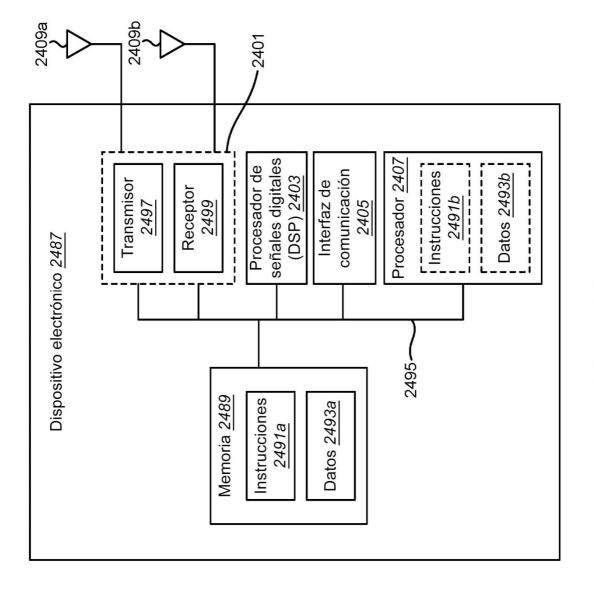

la Figura 24 ilustra determinados componentes que se pueden incluir dentro de un dispositivo electrónico.

#### **DESCRIPCIÓN DETALLADA**

5

25

30

35

40

45

50

55

60

65

[0014] Los sistemas y procedimientos divulgados en el presente documento pueden proporcionar enfoques para la renderización de múltiples niveles de detalle. Por ejemplo, se pueden renderizar múltiples niveles diferentes de detalle en la misma imagen. Esto puede mejorar la eficiencia de renderización y/o la experiencia del usuario. Como se usa en el presente documento, el término "renderizar" y sus variaciones pueden significar realizar una o más operaciones para producir datos de imágenes. Por ejemplo, la renderización puede incluir realizar una o más operaciones para convertir datos de geometría (por ejemplo, modelos geométricos, vértices, polígonos, etc.) en datos de imágenes (por ejemplo, datos de píxeles, píxeles, datos de dominio visual, etc.). Los datos de imágenes resultantes de la renderización pueden presentarse en una pantalla, almacenarse y/o transmitirse. Por ejemplo, los datos de imágenes renderizadas pueden o no presentarse en una pantalla inmediatamente. Los datos de imágenes renderizadas pueden almacenarse (para una presentación posterior en una pantalla, por ejemplo), pueden transmitirse a otro dispositivo (que puede presentar los datos de imágenes renderizadas en una pantalla, por ejemplo) y/o pueden presentarse en una pantalla.

[0015] La ineficiencia de renderización puede ser un problema actual. Por ejemplo, la realidad virtual (VR) puede incluir renderizar dos visualizaciones de una escena, lo cual puede hacer que el contenido sea dos veces más lento de renderizar. Un enfoque puede implicar realizar un seguimiento de los ojos (que se puede realizar de manera precisa y económica), renderizando tres pasadas de geometría con diferentes niveles de grosor, realizando suavizado y mezclando las tres cualidades diferentes de la memoria intermedia de la trama. Sin embargo, este enfoque puede ser ineficiente ya que las múltiples pasadas de geometría pueden superponerse, lo cual da como resultado que algunos píxeles se procesen repetidamente.

[0016] En algunas configuraciones, los sistemas y procedimientos divulgados en el presente documento pueden proporcionar enfoques para renderización de una sola pasada con múltiples niveles de detalle (múltiples LOD) (por ejemplo, renderización con resolución variable de una sola pasada). Por ejemplo, algunos enfoques pueden utilizar un teselador (por ejemplo, motor de teselado), suavizado de múltiples muestras (MSAA), envío dinámico de núcleos y/o una memoria intermedia de tramas de múltiples resoluciones (por ejemplo, no uniforme) (por ejemplo, objeto de memoria intermedia de tramas (FBO)). En algunos enfoques, solo se puede necesitar un paso de geometría. Esta mejora puede reducir el uso de ancho de banda de geometría y/o puede reutilizar MSAA.

[0017] Algunas configuraciones de los sistemas y procedimientos divulgados en el presente documento pueden ofrecer una o más ventajas de rendimiento. Por ejemplo, se puede implementar hardware que incluya un FBO de resolución múltiple y/o un envío dinámico de núcleos. Esto puede reducir el consumo de ancho de banda. Por ejemplo, múltiples (por ejemplo, tres) pasadas de geometría pueden colapsarse en una usando el teselador (por ejemplo, el motor de teselación). El suavizado de hardware de rasterizado se puede reutilizar en algunas configuraciones. Esto puede permitir mejoras en la renderización de contenido regular. De forma adicional o alternativa, el envío dinámico de núcleos de fragmentos puede reducir el cálculo. Estas mejoras pueden ser particularmente beneficiosas en el contexto de la realidad virtual (VR) y/o la realidad aumentada (AR), donde se pueden renderizar múltiples visualizaciones de una escena a la vez (para visualizaciones estereoscópicas, por ejemplo). En algunas configuraciones, VR y AR pueden combinarse. Los sistemas y procedimientos divulgados en el presente documento pueden ser beneficiosos, ya que la industria de procesamiento de gráficos busca formas de proporcionar experiencias inmersivas.

**[0018]** Los sistemas y procedimientos divulgados en el presente documento también describen enfoques para la renderización de múltiples zonas para la presentación en las ventanas. Estos sistemas y procedimientos pueden ser particularmente beneficiosos en el contexto de los vehículos para mejorar la experiencia del usuario en aplicaciones como la asistencia al conductor y los vehículos autónomos (por ejemplo, automóviles autónomos).

[0019] Ahora se describen diversas configuraciones con referencia a las Figuras, donde números de referencia parecidos pueden indicar elementos funcionalmente similares. Los sistemas y procedimientos, como se ha descrito e ilustrado en general en las Figuras en el presente documento, se pueden organizar y diseñar en una amplia variedad de configuraciones diferentes. Por tanto, la siguiente descripción más detallada de varias configuraciones, como se representa en las Figuras, no pretende limitar el alcance, como se reivindica, sino que es simplemente representativa de los sistemas y procedimientos.

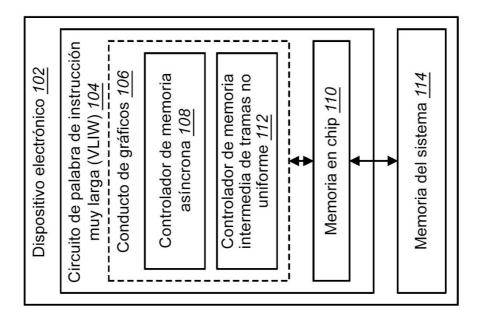

[0020] La Figura 1 es un diagrama de bloques que ilustra una configuración de un dispositivo electrónico 102 en el que se pueden implementar sistemas y procedimientos para renderizar múltiples niveles de detalle. Entre los ejemplos del dispositivo electrónico 102 se incluyen teléfonos inteligentes, ordenadores (por ejemplo, ordenadores de escritorio,

ordenadores portátiles, etc.), pantallas montadas en la cabeza (por ejemplo, casco de realidad virtual (VR), casco de realidad aumentada (AR), etc.), dispositivos VR, dispositivos AR, tablets, reproductores multimedia, televisores, automóviles, vehículos, cámaras, videocámaras, cámaras digitales, teléfonos celulares, cámaras personales, cámaras de acción, aviones, drones, vehículos aéreos no tripulados (UAV), equipos de atención médica, consolas de juegos, asistentes digitales personales (PDA), descodificadores, reproductores multimedia, etc. El dispositivo electrónico 102 puede incluir uno o más componentes o elementos. Uno o más de los componentes o elementos pueden implementarse en hardware (por ejemplo, circuitos), firmware y/o una combinación de hardware y software (por ejemplo, un procesador con instrucciones).

5

25

30

35

40

45

50

55

60

65

[0021] En algunas configuraciones, el dispositivo electrónico 102 puede incluir una palabra de instrucción muy larga 10 (VLIW) de circuito 104 y el sistema de memoria 114. El circuito 104 VLIW puede ser un circuito (por ejemplo, procesador) que implementa paralelismo de nivel de instrucción. Por ejemplo, el circuito VLIW 104 puede ejecutar instrucciones en paralelo (por ejemplo, simultáneamente). El circuito VLIW 104 puede estar acoplado (por ejemplo, en comunicación electrónica con) la memoria 114 del sistema. El circuito VLIW 104 puede ser un dispositivo para 15 renderizar imágenes. Por ejemplo, el circuito VLIW 104 puede convertir datos de geometría (por ejemplo, modelos geométricos, datos de geometría bidimensionales (2D) o tridimensionales (3D), vértices, polígonos, etc.) en una o más imágenes. Las imágenes resultantes pueden presentarse en una o más pantallas. Por ejemplo, las imágenes pueden ser una sola imagen para producir una visualización 2D o pueden ser múltiples imágenes (por ejemplo, imágenes estereoscópicas) para producir una visualización 3D. Por ejemplo, el circuito VLIW 104 puede producir múltiples 20 imágenes (por ejemplo, diferentes visualizaciones) para una visualización estereoscópica (por ejemplo, una imagen para un ojo izquierdo y otra imagen para un ojo derecho). Debe observarse que el circuito VLIW 104 puede renderizar una serie de imágenes (por ejemplo, vídeo). El circuito VLIW 104 puede implementarse en hardware o en una combinación de hardware y software. Un ejemplo del circuito VLIW 104 es una unidad de procesamiento de gráficos (GPU).

[0022] En algunas configuraciones, el dispositivo electrónico 102 puede realizar una o más de las funciones, procesos, procedimientos, pasos, etc., descritas en relación con una o más de las Figuras 2-5, 9, 11, 13 y 15-24. De forma adicional o alternativa, el dispositivo electrónico 102 puede incluir una o más de las estructuras descritas en relación con una o más de las Figuras 2-5, 9, 11, 13 y 15-24.

[0023] La memoria del sistema 114 puede almacenar instrucciones y/o datos. Entre los ejemplos de memoria del sistema 114 se incluyen memoria de acceso aleatorio (RAM), memoria de acceso aleatorio dinámico (DRAM), memoria de acceso aleatorio dinámico síncrona (SDRAM), memoria de acceso aleatorio dinámico síncrona de doble velocidad de datos (DDR SDRAM), DDR2, DDR3, DDR4, memoria de acceso aleatorio estático (SRAM), registros, memoria de solo lectura (ROM), memoria de solo lectura programable borrable (EPROM), memoria de solo lectura programable y borrable eléctricamente (EEPROM), memoria flash NAND, memoria flash NOR, etc. El circuito VLIW 104 puede acceder (por ejemplo, leer y/o escribir en) la memoria del sistema 114. La memoria del sistema 114 puede ser accesible por otros elementos (si los hay) del dispositivo electrónico 102, tales como uno o más procesadores (por ejemplo, unidades centrales de procesamiento (CPU)). La memoria del sistema 114 puede estar separada del circuito VLIW 104. Entre los ejemplos de instrucciones y/o datos que puede almacenar la memoria del sistema 114 pueden incluirse instrucciones, datos de comandos, datos de geometría (por ejemplo, vértices, polígonos, normales (por ejemplo, orientaciones de objetos), primitivas, metadatos, etc.), datos de textura, datos de visualización de acceso desordenados, parámetros de renderización (por ejemplo, parámetros de nivel de detalle), etc. En algunas configuraciones, el dispositivo electrónico 102 (por ejemplo, la memoria del sistema 114) puede incluir una o más memorias intermedias de tramas. Las memoria(s) intermedia(s) de tramas puede(n) almacenar en memoria intermedia (por ejemplo, almacenar) datos de imágenes. Los datos de imágenes almacenadas en memoria intermedia pueden presentarse en una o más pantallas.

[0024] El circuito VLIW 104 puede incluir uno o más elementos para renderizar imágenes. Entre algunos ejemplos de elementos puede incluirse una interfaz (FE), procesador de vértices (VP, buscador de vértices (VF), sombreador de vértices (VS), sombreador de control de teselación (TCS), sombreador de perímetros (HS), teselador (por ejemplo, motor de teselación) (TESS), sombreador de evaluación de teselación (TES), sombreador de dominio (DS), sombreador de geometría (GS), rasterizador (Rast), sombreador de fragmentos (FS), sombreador de píxeles (PS), creador de elementos, unidad de salida de renderización (ROP), recortador (Clip) y/o flujo de salida (SOL), etc. En algunas configuraciones, uno o más de estos elementos pueden denominarse conductos de gráficos 106. Cabe señalar que el teselador puede ser un motor de teselación de función fija en algunas configuraciones. El teselador (y/o uno o más elementos diferentes de un conducto de gráficos) puede implementarse en hardware, software o una combinación de hardware y software.

[0025] El circuito VLIW 104 puede incluir una memoria en chip 110. La memoria en chip 110 puede implementarse en el circuito VLIW 104 para proporcionar un acceso rápido a la memoria. Por ejemplo, se puede acceder a la memoria en chip 110 más rápidamente que la memoria del sistema 114. Entre los ejemplos de memoria en chip 110 pueden incluirse memoria de acceso aleatorio (RAM), memoria de acceso aleatorio dinámico (DRAM), memoria de acceso aleatorio dinámico síncrona de doble velocidad de datos (DDR SDRAM), DDR2, DDR3, DDR4, memoria estática de acceso aleatorio (SRAM), registros, memoria de solo lectura (ROM), memoria de solo lectura programable borrable (EPROM), memoria de solo lectura programable y

borrable eléctricamente (EEPROM), memoria flash NAND, memoria flash NOR, etc. En algunas configuraciones, la memoria en chip 110 puede implementarse en múltiples niveles (por ejemplo, memoria caché de nivel 1 (LI), memoria caché de nivel 2 (L2), memoria caché de nivel 3 (L3), etc.). Entre los ejemplos de datos que puede almacenar la memoria en chip 110 pueden incluirse datos de geometría (por ejemplo, vértices, polígonos, normales, primitivas, metadatos, etc.), datos de textura, datos de visualización de acceso sin ordenar, uno o más parámetros de renderización (por ejemplo,, parámetro(s) de nivel de detalle (LOD), etc. En algunas configuraciones, la memoria en chip 110 puede incluir una o más memorias intermedias de tramas (además de o de forma alternativa desde la memoria del sistema 114, por ejemplo). Las memoria(s) intermedia(s) de tramas puede(n) almacenar en memoria intermedia (por ejemplo, almacenar) datos de imágenes. Los datos de imágenes almacenadas en memoria intermedia pueden presentarse en una o más pantallas.

5

10

15

20

25

30

35

40

45

50

55

[0026] En algunas configuraciones, el circuito VLIW 104 puede incluir un controlador de memoria asíncrona 108. El controlador de memoria asíncrona 108 puede implementarse en hardware o en una combinación de hardware y software. El controlador de memoria asíncrona 108 puede implementarse en el circuito VLIW 104, por separado del circuito VLIW, o puede implementarse parcialmente en el circuito VLIW 104 y parcialmente separado del circuito VLIW 104. El controlador de memoria asíncrona 108 puede configurarse para acceder a la memoria (por ejemplo, memoria en chip 110 y/o memoria del sistema 114) asíncronamente. En algunas configuraciones, el controlador de memoria asíncrona 108 funciona "asíncronamente" en el sentido de que el controlador de memoria asíncrona 108 puede acceder a la memoria (por ejemplo, parámetro(s), parámetro(s) de nivel de detalle (LOD), etc.) fuera de sincronización con un conjunto de datos que está siendo procesado (por ejemplo, teselado). Por ejemplo, el circuito VLIW 104 puede procesar periódicamente conjuntos de datos. El procesamiento (por ejemplo, teselado) de un solo conjunto de datos puede denominarse llamada de extracción. Por ejemplo, una llamada de extracción puede ser una instrucción (por ejemplo, una petición programática, instrucción, etc.) para que el circuito VLIW 104 procese (por ejemplo, renderice) un conjunto de datos. Uno o más parámetros (por ejemplo, parámetro LOD, configuración de teselación, uno o más parámetros diferentes, etc.) pueden estar asociados y/o configurados para la llamada de extracción. En consecuencia, una llamada de extracción puede establecer un LOD que se renderizará para el conjunto de datos, por ejemplo.

[0027] En los enfoques conocidos, cada conjunto de datos (por ejemplo, llamada de extracción) tiene un nivel fijo de detalle (LOD). En esos enfoques, el LOD para un conjunto de datos no puede cambiar una vez que el procesamiento ha comenzado en ese conjunto de datos (por ejemplo, no puede cambiar durante una llamada de extracción). Además, cada conjunto de datos solo puede tener un único LOD en enfoques conocidos.

[0028] De acuerdo con los sistemas y procedimientos divulgados en el presente documento, el controlador de memoria asíncrona 108 puede acceder asíncronamente a la memoria (por ejemplo, memoria en chip 110 y/o memoria del sistema 114) para permitir la renderización de diferentes niveles de detalle (por ejemplo, diferentes zonas con diferentes niveles de detalle) dentro de un solo conjunto de datos (por ejemplo, durante el procesamiento de una llamada de extracción). Por ejemplo, el controlador de memoria asíncrona 108 puede acceder a la memoria (por ejemplo, parámetro (s), parámetro (s) LOD, etc.) después del procesamiento (por ejemplo, teselación, sombreado, etc.) en un conjunto de datos que ha comenzado y antes de que se complete el procesamiento en el conjunto de los datos. Esto puede permitir que el circuito VLIW 104 cambie el LOD durante el procesamiento de un conjunto de datos para producir diferentes LOD en un conjunto de datos. Cada conjunto de datos puede incluir múltiples primitivas (por ejemplo, puntos, polígonos, etc.). En algunas configuraciones, cada conjunto de datos puede (inicialmente) tener un solo LOD asignado. Sin embargo, el controlador de memoria asíncrona 108 puede asignar un LOD diferente a un conjunto de datos durante el procesamiento de ese conjunto de datos. En otras palabras, el controlador de memoria asíncrona 108 puede cambiar el LOD para un conjunto de datos (después de que el procesamiento (por ejemplo, teselación, sombreado, etc.) en ese conjunto de datos haya comenzado pero antes de que el procesamiento (por ejemplo, teselación, sombreado, etc.) en ese conjunto de datos se haya completado). Por ejemplo, los sistemas y procedimientos divulgados en el presente documento pueden permitir cambiar el LOD por píxel y/o por primitiva (incluso, por ejemplo, dentro de un conjunto de datos). En algunas configuraciones, los parámetros (por ejemplo, parámetro(s), parámetro(s) LOD, etc.) pueden actualizarse durante el procesamiento. Por ejemplo, un procesador (por ejemplo, unidad central de procesamiento (CPU), procesador de señal digital (DSP), etc.) o cualquier bloque de hardware dedicado (por ejemplo, cualquier hardware que trate con datos del sensor (por ejemplo, datos del sensor de seguimiento de los ojos, datos del sensor de movimiento, etc.)) puede actualizar los parámetros. El circuito VLIW 104 (por ejemplo, GPU) puede leer (por ejemplo, puede leer siempre, leer continuamente, leer periódicamente, etc.) desde una sección de memoria (por ejemplo, memoria en chip 110 y/o memoria del sistema 114) que incluye el parámetros. Por consiguiente, el circuito VLIW 104 (por ejemplo, GPU) puede ajustarse en consecuencia por primitiva en lugar de para una llamada de extracción completa. En algunas configuraciones, el circuito VLIW 104 puede renderizar diferentes niveles de detalle en una sola llamada de extracción.

[0029] Los sistemas y procedimientos divulgados en el presente documento pueden proporcionar uno o más beneficios. Por ejemplo, el controlador de memoria asíncrona 108 puede permitir un procesamiento más eficiente cuando se procesan múltiples LOD. En enfoques conocidos, se pueden renderizar múltiples capas superpuestas, donde cada capa tiene un LOD diferente. A continuación, las capas superpuestas se pueden mezclar. Sin embargo, este enfoque es ineficiente porque los mismos datos se renderizan varias veces. De acuerdo con los sistemas y procedimientos divulgados en el presente documento, se pueden renderizar diferentes LOD en una sola pasada. Esto

puede evitar volver a renderizar los mismos datos y/o evitar tener que mezclar varias capas con diferentes niveles de detalle.

[0030] De forma adicional o alternativa, los sistemas y procedimientos divulgados en el presente documento pueden permitir asíncronamente cambiar LOD. Por ejemplo, renderizar una o más zonas de una imagen puede basarse en el seguimiento de los ojos. Por ejemplo, el dispositivo electrónico 102 puede renderizar múltiples zonas con diferentes niveles de detalle, donde una zona con el mayor nivel de detalle se renderiza en un área donde el usuario está buscando actualmente. El seguimiento de los ojos puede detectar cuándo un usuario cambia la mirada para mirar una parte diferente de la imagen. Los sistemas y procedimientos divulgados en el presente documento (por ejemplo, el controlador de memoria asíncrona 108) pueden cambiar inmediatamente el LOD renderizado basándose en el seguimiento de los ojos. Por ejemplo, el circuito VLIW 104 puede aumentar el LOD en un área de la imagen que el usuario ha cambiado de mirada para ver, incluso durante el procesamiento de un conjunto de datos. Esto puede proporcionar una mejor experiencia de usuario. Además, los sistemas y procedimientos divulgados en el presente documento (por ejemplo, el controlador de memoria asíncrona 108) pueden reducir el LOD en un área de la imagen a la que ya no se dirige la mirada del usuario. Esto puede reducir el procesamiento innecesario.

[0031] El circuito VLIW 104 puede incluir un controlador de memoria intermedia de tramas no uniforme 112. El controlador de memoria intermedia de tramas no uniforme 112 (por ejemplo, FBO de resolución múltiple) puede implementarse en hardware o una combinación de hardware y software. El controlador de memoria intermedia de tramas no uniforme 112 puede implementarse en el circuito VLIW 104, por separado del circuito VLIW 104, o puede implementarse parcialmente en el circuito VLIW 104 y parcialmente separado del circuito VLIW 104. En algunas configuraciones, el controlador de memoria intermedia de tramas no uniforme 112 puede implementarse como parte del conducto de gráficos 106. De forma alternativa, el controlador de memoria intermedia de tramas no uniforme 112 puede implementarse como parte de la memoria en chip 110. En otra implementación, el controlador de memoria intermedia de tramas no uniforme 112 puede implementarse en el circuito VLIW 104 pero separado del conducto de gráficos 106 y la memoria en chip 110.

[0032] El controlador de memoria intermedia de tramas no uniforme 112 puede configurarse para acceder dinámicamente a diferentes subconjuntos de una o más memoria(s) intermedia(s) de tramas. En algunas configuraciones, los diferentes subconjuntos de una memoria intermedia de tramas pueden corresponder a diferentes niveles de detalle, zonas con diferentes niveles de detalle y/o diferentes niveles de mapas MIP. Por ejemplo, el controlador de memoria intermedia de tramas no uniforme 112 puede configurarse para funcionar dinámicamente en diferentes subconjuntos de una memoria intermedia de tramas. Cabe señalar que puede haber dos o más subconjuntos de memorias intermedias de tramas. En algunas configuraciones, diferentes subconjuntos de la memoria intermedia de tramas no uniforme pueden corresponder a diferentes visualizaciones (por ejemplo, una visualización del ojo izquierdo y una visualización del ojo derecho para la renderización estereoscópica). La memoria intermedia de tramas no uniforme puede mejorar la utilización del ancho de banda. Con una memoria intermedia de tramas no uniforme, por ejemplo, la visualización del ojo izquierdo y la visualización del ojo derecho pueden procesarse simultáneamente (por ejemplo, simultáneamente) y guardarse en la memoria 114 del sistema en una sola pasada. De forma adicional o alternativa, por ejemplo, la memoria intermedia de tramas no uniforme puede habilitar y/o mejorar la utilización de la memoria para renderizar múltiples LOD en una sola pasada.

[0033] En algunas configuraciones, el acceso dinámico a diferentes subconjuntos de la memoria intermedia de tramas puede incluir el acceso a al menos un píxel de una primera zona a una velocidad diferente de al menos un píxel de una segunda zona. La primera zona y la segunda zona pueden corresponder a diferentes niveles de detalle. Por ejemplo, el controlador de memoria intermedia de tramas no uniforme 112 puede permitir que los píxeles de una zona (con un LOD más alto, por ejemplo) se procesen a una velocidad mayor que los píxeles de otra zona (con un LOD más bajo, por ejemplo). Este enfoque puede permitir ahorros de energía al ralentizar el procesamiento de una o más zonas (por ejemplo, zonas de bajo nivel de detalle). Cabe señalar que puede haber píxeles de dos o más zonas a las que se puede acceder a dos o más velocidades diferentes.

[0034] De forma adicional o alternativa, el acceso dinámico a diferentes subconjuntos de la memoria intermedia de tramas puede incluir permitir el intercambio de subrutinas de sombreador. Por ejemplo, el intercambio de subrutinas de sombreador se puede realizar cuando el procesamiento de un primer píxel está en curso y se completa el proceso de un segundo píxel. Por ejemplo, un primer subconjunto de la memoria intermedia de tramas puede asignarse a uno o más píxeles procesados con una primera subrutina de sombreador, mientras que un segundo subconjunto de la memoria intermedia de tramas puede asignarse a uno o más píxeles procesados con una segunda subrutina de sombreador. Cuando se completa el procesamiento de uno o más píxeles de segunda subrutina de sombreador, el dispositivo electrónico 102 puede intercambiar subrutinas de sombreador para ocupar el segundo subconjunto de la memoria intermedia de tramas. Esto puede proporcionar un procesamiento más eficiente al permitir que la capacidad de memoria intermedia de tramas se utilice de manera más eficiente. Cabe señalar que se pueden utilizar dos o más subconjuntos de la memoria intermedia de tramas para permitir el intercambio de subrutinas para uno o más de los subconjuntos.

[0035] El controlador de memoria intermedia de tramas no uniforme 112 puede configurarse para sustituir una primera muestra procesada de un primer píxel por una segunda muestra de un segundo píxel para evitar el procesamiento de

la segunda muestra del segundo píxel. El primer píxel puede tener un número diferente de muestras que el segundo píxel. Por ejemplo, un primer píxel de una primera zona puede tener un LOD más alto que un segundo píxel contiguo de una segunda zona con un LOD más bajo. El controlador de memoria intermedia de tramas no uniforme 112 puede reemplazar la muestra (no procesada) del segundo píxel con la muestra (procesada) del primer píxel. De esta forma, el controlador de memoria intermedia de tramas no uniforme 112 puede reducir el procesamiento. Debe observarse que el controlador de memoria intermedia de tramas no uniforme 112 puede reemplazar una o más muestras (sin procesar) de uno o más píxeles por una o más muestras (procesadas) de uno o más píxeles diferentes.

[0036] En algunas configuraciones, el dispositivo electrónico 102 puede incluir y/o puede estar acoplado a una o más pantallas (por ejemplo, pantallas montadas en la cabeza). Las pantallas se pueden configurar para presentar los diferentes niveles de detalle.

15

20

25

30

35

40

55

60

65

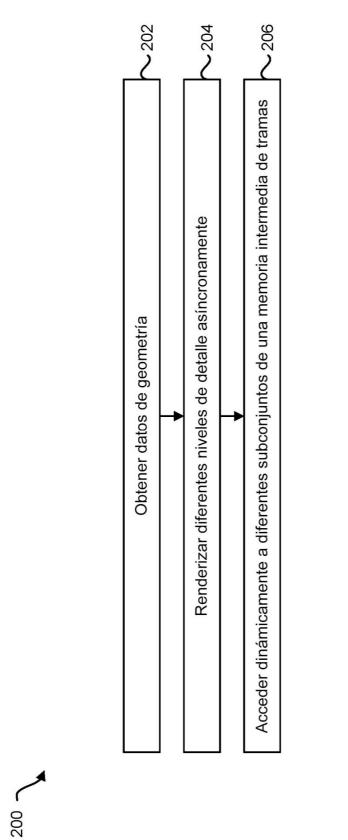

[0037] La Figura 2 es un diagrama de flujo que ilustra una configuración de un procedimiento 200 para renderizar múltiples niveles de detalle. El procedimiento 200 puede ser realizado por el dispositivo electrónico 102 descrito en relación con la Figura 1.

[0038] El dispositivo electrónico 102 puede obtener 202 datos de geometría. Por ejemplo, el dispositivo electrónico 102 puede cargar datos de geometría del almacenamiento (por ejemplo, almacenamiento en disco duro, almacenamiento extraíble como un disco duro externo, unidad de disco de vídeo digital (DVD), unidad de Blu-Ray, disco compacto (CD), unidad de memoria, etc.) en la memoria (por ejemplo, memoria del sistema 114 y/o memoria en chip 110). De forma adicional o alternativa, el dispositivo electrónico 102 puede recibir datos de geometría de otro dispositivo. Por ejemplo, el dispositivo electrónico 102 puede recibir datos de geometría a través de una interfaz de comunicación (por ejemplo, Ethernet, interfaz 802.11 del Instituto de Ingenieros Eléctricos y Electrónicos (IEEE), interfaz de red celular, etc.) y cargar los datos de geometría en la memoria (por ejemplo, memoria del sistema 114 y/o memoria en chip 110). Entre los ejemplos de datos de geometría pueden incluirse puntos, líneas y/o polígonos (por ejemplo, triángulos), etc.

[0039] El dispositivo electrónico 102 puede renderizar 204 diferentes niveles de detalle asíncronamente. Esto se puede conseguir como se ha descrito anteriormente en relación con la Figura 1. Por ejemplo, el dispositivo electrónico 102 puede acceder asíncronamente a la memoria (por ejemplo, la memoria del sistema 114 y/o la memoria en chip 110) para renderizar diferentes niveles de detalle. Por ejemplo, el dispositivo electrónico 102 puede cambiar un LOD para un conjunto de datos durante el procesamiento (donde el conjunto de datos inicialmente tenía un LOD diferente, por ejemplo). En algunas configuraciones, renderizar 204 niveles diferentes de detalle asíncronamente puede incluir la realización de teselación dinámica de LOD.

[0040] El dispositivo electrónico 102 puede acceder dinámicamente a 206 subconjuntos diferentes de una memoria intermedia de tramas. Esto se puede conseguir como se ha descrito anteriormente en relación con la Figura 1. Por ejemplo, el dispositivo electrónico 102 puede acceder al menos a un píxel de una primera zona a una velocidad diferente de al menos un píxel de una segunda zona. De forma adicional o alternativa, el dispositivo electrónico 102 puede permitir el intercambio de subrutinas de sombreador cuando el procesamiento de un primer píxel está en curso y se completa el proceso de un segundo píxel. De forma adicional o alternativa, el dispositivo electrónico 102 puede sustituir una primera muestra procesada de un primer píxel por una segunda muestra de un segundo píxel para evitar procesar la segunda muestra del segundo píxel.

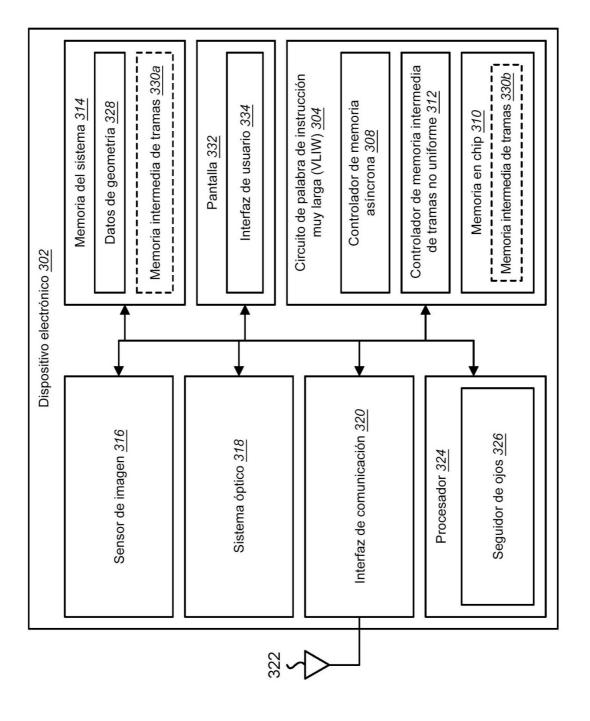

45 [0041] La Figura 3 es un diagrama de bloques que ilustra una configuración de un dispositivo electrónico 302 en el que se pueden implementar sistemas y procedimientos para renderizar múltiples niveles de detalle. El dispositivo electrónico 302 descrito en relación con la Figura 3 puede ser un ejemplo del dispositivo electrónico 102 descrito en relación con la Figura 1. En algunas configuraciones, uno o más de los componentes o elementos del dispositivo electrónico 302 pueden ser similares a los componentes o elementos correspondientes descritos en relación con la Figura 1. Uno o más de los componentes o elementos pueden implementarse en hardware (por ejemplo, circuitos) o una combinación de hardware y software (por ejemplo, un procesador con instrucciones).

[0042] En algunas configuraciones, el dispositivo electrónico 302 puede incluir el circuito de palabra de instrucción muy larga (VLIW) 304, la memoria del sistema 314, una o más pantallas 332, uno o más sensores de imagen 316, uno o más sistemas ópticos 318, una o más interfaces de comunicación 320, una o más antenas 322 y/o uno o más procesadores 324. Dos o más de los elementos o componentes descritos en relación con la Figura 3 pueden estar en comunicación electrónica entre sí. Por ejemplo, el circuito VLIW 304 puede estar acoplado (por ejemplo, en comunicación electrónica con) la memoria del sistema 314. El circuito 304 VLIW puede ser un dispositivo para renderizar imágenes como se ha descrito anteriormente en relación con una o más de las Figuras 1 y 2. En algunas configuraciones, las imágenes resultantes pueden presentarse en una o más pantallas 332. El circuito 304 VLIW puede estar separado del procesador 324 en algunas implementaciones. En otras implementaciones, el circuito VLIW 304 puede integrarse en el procesador 324.

[0043] La interfaz de comunicación 320 puede permitir que el dispositivo electrónico 302 se comunique con uno o más de otros dispositivos electrónicos diferentes. Por ejemplo, la interfaz de comunicación 320 puede proporcionar una interfaz para comunicaciones por cable y/o inalámbricas. En algunas configuraciones, la interfaz de comunicación 320

puede estar acoplada a una o más antenas 322 para transmitir y/o recibir señales de radiofrecuencia (RF). De forma adicional o alternativa, la interfaz de comunicación 320 puede habilitar uno o más tipos de comunicación por cable (por ejemplo, Universal Serial Bus (USB), Ethernet, Video Graphics Array (VGA), Digital Visual Interface (DVI), High Definition Multimedia Interface (HDMI), DisplayPort, Mobile High-Definition Link (MHL), etc.).

5

10

15

20

25

30

45

50

55

60

65

[0044] En algunas configuraciones, múltiples interfaces de comunicación 320 se pueden implementar y/o utilizar. Por ejemplo, una interfaz de comunicación 320 puede ser una interfaz de comunicación celular (por ejemplo, 3G, evolución a largo plazo (LTE), CDMA, etc.) 320, otra interfaz de comunicación 320 puede ser una interfaz Ethernet, otra interfaz de comunicación 320 puede ser una interfaz de bus serie universal (USB), otra interfaz de comunicación 320 puede ser una interfaz de red de área local inalámbrica (WLAN) (por ejemplo, interfaz 802.11 del Instituto de Ingenieros Eléctricos y Electrónicos (IEEE)), y otra interfaz de comunicación 320 puede ser una interfaz Bluetooth.

[0045] En algunas configuraciones, el dispositivo electrónico 302 puede llevar a cabo una o más de las funciones, procesos, procedimientos, pasos, etc., descrita en relación con una o más de las Figuras 1, 3-5, 9, 11, 13 y 15-24. De forma adicional o alternativa, el dispositivo electrónico 302 puede incluir una o más de las estructuras descritas en relación con una o más de las Figuras 1, 3-5, 9, 11, 13 y 15-24.

[0046] La memoria del sistema 314 puede almacenar instrucciones y/o datos. La memoria del sistema 314 descrita en relación con la Figura 3 puede ser un ejemplo de la memoria del sistema 114 descrita en relación con la Figura 1. El circuito 304 VLIW puede acceder (por ejemplo, leer y/o escribir en) la memoria del sistema 314. El (los) procesador(es) 324 también pueden acceder a la memoria del sistema 314. La memoria del sistema 314 puede almacenar datos de geometría 328. En algunas configuraciones, la memoria del sistema 314 puede incluir una memoria intermedia de tramas 330a. La memoria intermedia de tramas 330a puede ser una parte de la memoria del sistema 314 para almacenar datos de imágenes. Los datos de imágenes almacenados temporalmente pueden presentarse en una o más pantallas 332 en algunas configuraciones.

[0047] El circuito VLIW 304 puede incluir uno o más elementos para renderizar imágenes. Entre algunos ejemplos de elementos puede incluirse una interfaz (FE), procesador de vértices (VP, buscador de vértices (VF), sombreador de vértices (VS), sombreador de control de teselación (TCS), sombreador de perímetros (HS), teselador (por ejemplo, motor de teselación) (TESS), sombreador de evaluación de teselación (TES), sombreador de dominio (DS), sombreador de geometría (GS), rasterizador (Rast), sombreador de fragmentos (FS), sombreador de píxeles (PS), creador de elementos, unidad de salida de renderización (ROP), recortador (Clip) y/o flujo de salida (SOL), etc. En algunas configuraciones, uno o más de estos elementos pueden denominarse un conducto de gráficos.

[0048] El circuito VLIW 304 puede incluir una memoria en chip 310. La memoria en chip 310 descrita en relación con la Figura 3 puede ser un ejemplo de la memoria en chip 110 descrita en relación con la Figura 1. En algunas configuraciones, la memoria en chip 310 puede incluir una memoria intermedia de tramas 330b (además de o de forma alternativa desde la memoria intermedia de tramas 330a en la memoria del sistema 314, por ejemplo). La memoria intermedia de tramas puede ser una parte de la memoria en chip 310 para almacenar datos de imágenes. Los datos de imágenes almacenados temporalmente pueden presentarse en una o más pantallas 332 en algunas configuraciones.

[0049] En algunas configuraciones, el circuito VLIW 304 puede incluir un controlador de memoria asíncrona 308. El controlador de memoria asíncrona 308 puede implementarse en hardware o en una combinación de hardware y software. El controlador de memoria asíncrona 308 puede implementarse en el circuito VLIW 304, por separado del circuito VLIW, o puede implementarse parcialmente en el circuito VLIW 304 y parcialmente separado del circuito VLIW 304. El controlador de memoria asíncrona 308 puede configurarse para acceder a la memoria (por ejemplo, memoria en chip 310 y/o memoria del sistema 314) asíncronamente. Debe observarse que el controlador de memoria asíncrona 308 puede utilizar (por ejemplo, acceder a) la memoria en chip 110 y/o la memoria del sistema 114 (por ejemplo, una o ambos). Algunas configuraciones pueden depender de un caso de uso. Por ejemplo, si los datos del sensor (por ejemplo, datos del sensor de imagen 316) se escriben a una velocidad alta (por ejemplo, 1000 hertzios (Hz)), el almacenamiento en memoria caché puede perder tiempo, batería y/u otros recursos. El controlador de memoria asíncrona 308 descrito en relación con la Figura 3 puede ser un ejemplo del controlador de velocidad de memoria asíncrona 108 descrito en relación con la Figura 1. El controlador de memoria asíncrona 308 descrito en relación con la Figura 3 puede funcionar como se ha descrito en relación con el controlador de memoria asíncrona 108 descrito en relación con la Figura 1.

[0050] El circuito VLIW 304 puede incluir un controlador de memoria intermedia de tramas no uniforme 312. El controlador de memoria intermedia de tramas no uniforme 312 puede implementarse en hardware o en una combinación de hardware y software. El controlador de memoria intermedia de tramas no uniforme 312 puede implementarse en el circuito VLIW 304, por separado del circuito VLIW 304, o puede implementarse parcialmente en el circuito VLIW 304 y parcialmente separado del circuito VLIW 304. En algunas configuraciones, el controlador de memoria intermedia de tramas no uniforme 312 puede implementarse como parte del conducto de gráficos. De forma alternativa, el controlador de memoria intermedia de tramas no uniforme 312 puede implementarse como parte de la memoria en chip 310. En otra implementación, el controlador de memoria intermedia de tramas no uniforme 312 puede implementarse en el circuito VLIW 304 pero separado del conducto de gráficos 306 y la memoria en chip 310. El

controlador de memoria intermedia de tramas no uniforme 312 descrito en relación con la Figura 3 puede ser un ejemplo del controlador de memoria intermedia de tramas no uniforme 112 descrito en relación con la Figura 1. El controlador de memoria intermedia de tramas no uniforme 312 descrito en relación con la Figura 3 puede funcionar como se ha descrito en relación con el controlador de memoria intermedia de tramas no uniforme 112 descrito en relación con la Figura 1.

[0051] En algunas configuraciones, el dispositivo electrónico 302 puede llevar a cabo renderización de múltiples LOD de una sola pasada. La renderización de múltiples LOD puede incluir la renderización de diferentes zonas de una imagen con diferentes niveles de detalle. La renderización de múltiples LOD de una sola pasada puede incluir renderizar diferentes zonas con diferentes niveles de detalle (por ejemplo, niveles de detalle teselados) en una sola pasada (sin procesar repetidamente ningún píxel, por ejemplo). La renderización con resolución variable de una sola pasada puede ser un ejemplo de renderización de múltiples LOD de una sola pasada, donde diferentes zonas con diferentes niveles de detalle pueden basarse en el seguimiento de los ojos. Por ejemplo, una zona puede ser un área circular (o un área de otra forma) aproximadamente centrada en el punto de una pantalla (por ejemplo, una imagen) donde el usuario está mirando. De forma adicional o alternativa, la renderización de una sola pasada (por ejemplo, la renderización de múltiples LOD de una sola pasada) puede incluir la realización de una pasada (por ejemplo, la pasada de procesamiento) sobre los datos y/o la textura que se renderizará, aunque se debe renderizar tanto una visualización del ojo izquierdo como una visualización del ojo derecho. En consecuencia, algunas configuraciones de los sistemas y procedimientos divulgados en el presente documento pueden utilizar la mayor cantidad posible de datos para las visualizaciones de ambos ojos antes de mover los datos entre la memoria del sistema y la memoria en chip (por ejemplo, memoria GPU). En algunas configuraciones, el controlador de memoria asíncrona 308 y/o el controlador de memoria intermedia de tramas no uniforme 312 pueden permitir la realización de la renderización de múltiples LOD de una sola pasada (por ejemplo, la renderización con resolución variable de una sola pasada). Por ejemplo, el controlador de memoria asíncrona 308 puede permitir la lectura de parámetros (por ejemplo, parámetro(s) de nivel de detalle (LOD)) de un bloque de memoria volátil (por ejemplo, adaptación dinámica durante una llamada de extracción). Por ejemplo, el controlador de memoria asíncrona 308 puede permitir que uno o más sombreadores de control de teselación (TCS), teselador (TESS), sombreador de evaluación de teselación (TES), sombreador de geometría (GS), rasterizador y sombreador de fragmentos (FS) accedan a uno o más parámetros de un bloque de memoria volátil (por ejemplo, para adaptarse dinámicamente durante una llamada de extracción).

**[0052]** En algunas configuraciones, el circuito VLIW 304 puede incluir un rasterizador. El rasterizador puede permitir que MSAA realice más muestreo de las primitivas, lo cual a su vez puede activar más evaluaciones de sombreadores de fragmentos (FS). Además, se puede realizar un muestreo de las primitivas para evitar distorsiones como marcas, que se deben a que no se procesan ni promedian suficientes muestras.

[0053] El dispositivo electrónico 302 puede obtener una o más imágenes (por ejemplo, imágenes digitales, tramas de imagen, vídeo, etc.). La una o más imágenes pueden ser imágenes de uno o más usuarios y/o una escena (por ejemplo, uno o más objetos y/o fondo). Por ejemplo, el dispositivo electrónico 302 puede incluir uno o más sensores de imagen 316 y/o uno o más sistemas ópticos 318 (por ejemplo, lentes) que enfocan imágenes de objetos que se encuentran dentro del campo de visión del sistema o sistemas ópticos 318 en los sensores de imagen 316. En algunas configuraciones, el (los) sensor(es) de imagen 316 puede(n) capturar una o más imágenes. El (los) sensor(es) de imagen 316 y/o el (los) sistema(s) óptico(s) 318 puede(n) estar acoplado(s) y/o controlado(s) por el procesador 324.

[0054] De forma adicional o alternativa, el dispositivo electrónico 302 puede solicitar y/o recibir la una o más imágenes de otro dispositivo (por ejemplo, un sensor de imagen externo acoplado al dispositivo electrónico 302, un servidor de red, cámara de tráfico, cámara de caída, cámara de automóvil, cámara web, etc.). En algunas configuraciones, el dispositivo electrónico 302 puede solicitar y/o recibir una o más imágenes a través de la interfaz de comunicación 320. Por ejemplo, el dispositivo electrónico 302 puede incluir o no una cámara (por ejemplo, un sensor de imagen 316 y/o un sistema óptico 318) y puede recibir imágenes de un dispositivo remoto.

[0055] En algunas configuraciones, los uno o más sensores de imagen 316 incluidos en el dispositivo electrónico 302 y/o uno o más sensores de imagen diferentes acoplados al dispositivo electrónico 302 pueden estar orientados a la captura de una o más imágenes de un usuario. Por ejemplo, un teléfono inteligente puede incluir una cámara montada en la misma cara que una pantalla (por ejemplo, la pantalla 332). De esta manera, la cámara puede capturar imágenes de un usuario mientras el usuario mira la pantalla. En otro ejemplo, se puede montar una cámara en una consola y/o volante de un vehículo para capturar imágenes de un usuario (por ejemplo, conductor).

[0056] De forma adicional o alternativa, el uno o más sensores de imagen 316 incluidos en el dispositivo electrónico 302 y/o uno o más sensores de imagen diferentes acoplados al dispositivo electrónico 302 pueden estar orientados a la captura del paisaje. Por ejemplo, una o más cámaras pueden montarse en la parte posterior de un teléfono inteligente. En otro ejemplo, una o más cámaras pueden montarse en el exterior de un vehículo. En algunas configuraciones, el dispositivo electrónico 302 puede utilizar imágenes de escenarios en aplicaciones de realidad aumentada (AR), aplicaciones de realidad virtual (VR) y/u otras aplicaciones (por ejemplo, visualización envolvente, asistencia al conductor, sistemas avanzados de asistencia al conductor (ADAS), etc.).

65

5

10

15

20

25

30

35

40

45

50

55

60

[0057] En algunas configuraciones, las imágenes capturadas por los sensores de imagen 316 y/o recibidas a través de las interfaces de comunicaciones 320 pueden ser utilizadas por el dispositivo electrónico 302 de seguimiento de los ojos. Por ejemplo, el procesador 324 puede incluir y/o implementar un seguidor de ojos 326. El seguidor de ojos 326 puede seguir la mirada (por ejemplo, la dirección de la mirada) de uno o más ojos del usuario. Por ejemplo, el seguidor de ojos 326 puede localizar los ojos de uno o más usuarios en las imágenes y puede estimar la mirada (por ejemplo, la dirección de la mirada) de los usuarios. Por ejemplo, el seguidor de ojos 326 puede determinar (por ejemplo, estimar) dónde está mirando un usuario en una pantalla (por ejemplo, mostrar 332 o una pantalla externa) y/o dónde está mirando en una imagen presentada por una pantalla. En otras palabras, el seguidor de ojos 326 puede determinar (por ejemplo, estimar) hacia dónde se dirige la mirada de un usuario en relación con una imagen y/o una pantalla.

5

10

15

20

25

30

35

40

45

[0058] Los sistemas y procedimientos aquí descritos pueden permitir asíncronamente el cambio de LOD y/o la renderización de múltiples niveles de detalle en una sola pasada. En algunas configuraciones, renderizar una o más zonas de una imagen puede basarse en el seguimiento de los ojos. Las zonas de la imagen pueden tener diferentes niveles de detalle. Por ejemplo, el dispositivo electrónico 302 puede renderizar múltiples zonas con diferentes niveles de detalle, donde una zona con el mayor nivel de detalle se renderiza en un área donde el usuario está buscando actualmente. En algunas configuraciones, esto se puede denominar renderización con resolución variable. El seguidor de ojos 326 puede producir información de seguimiento de los ojos. La información de seguimiento de los ojos puede indicar hacia dónde se dirige la mirada de un usuario (por ejemplo, se dirigen las miradas de los usuarios) en relación con una pantalla y/o imagen. En algunas configuraciones, el procesador 324 y/o el circuito VLIW 304 pueden determinar uno o más parámetros LOD basándose en la información de seguimiento de los ojos. Los parámetros LOD pueden indicar un LOD que se renderizará para una o más zonas de una imagen. Los parámetros LOD pueden almacenarse en la memoria del sistema 314 y/o en la memoria en chip 310. Los parámetros LOD pueden actualizarse asíncronamente en relación con un conjunto de datos (por ejemplo, llamada de extracción) que está procesando el circuito 304 VLIW. El controlador de memoria asíncrona 308 puede leer los parámetros LOD (de la memoria del sistema 314 y/o la memoria en chip 310) durante el procesamiento del conjunto de datos (por ejemplo, llamada de extracción). Por ejemplo, el controlador de memoria asíncrona 308 puede actualizar la configuración de teselación

durante el procesamiento del conjunto de datos (por ejemplo, llamada de extracción).

[0059] El seguimiento de los ojos 326 puede detectar cuándo un usuario cambia la mirada para mirar a una parte diferente de la imagen. Los sistemas y procedimientos divulgados en el presente documento (por ejemplo, el controlador de memoria asíncrona 308) pueden cambiar inmediatamente el LOD renderizado basándose en el seguimiento de los ojos (por ejemplo, la información de seguimiento de los ojos y/o los parámetros LOD). Por ejemplo, el controlador de memoria asíncrona 308 puede leer uno o más parámetros (por ejemplo, parámetros LOD), que pueden cambiar durante el procesamiento de un conjunto de datos (por ejemplo, llamada de extracción). Por ejemplo, el circuito VLIW 304 puede aumentar el LOD en un área (por ejemplo, zona) de la imagen que el usuario ha cambiado de mirada para ver, incluso durante el procesamiento de un conjunto de datos. De forma adicional o alternativa, los sistemas y procedimientos divulgados en el presente documento (por ejemplo, el controlador de memoria asíncrona 308) pueden reducir el LOD en un área (por ejemplo, zona) de la imagen a la que ya no se dirige la mirada del usuario. En algunas configuraciones, una zona puede ser un área circular (o un área de otra forma) aproximadamente centrada en el punto de una pantalla (por ejemplo, una imagen) donde el usuario está mirando. En otras configuraciones, una zona puede ser el área completa de una imagen correspondiente a una ventana que el usuario está viendo.

[0060] En algunas configuraciones, el dispositivo electrónico 302 puede incluir una aplicación de cámara y/o una pantalla 332. Cuando se ejecuta la aplicación de cámara, el sensor de imagen 316 puede capturar imágenes de objetos que se encuentran dentro del campo de visión del sistema óptico 318. Las imágenes que están siendo capturadas por el sensor de imagen 316 pueden presentarse en la pantalla 332. En algunas configuraciones, estas imágenes pueden mostrarse en rápida sucesión a una velocidad de tramas relativamente alta, de modo que, en cualquier momento dado, los objetos que se encuentran dentro del campo de visión del sistema óptico 318 se presentan en la pantalla 332.

[0061] Se ha de observar que uno o más de los elementos ilustrados en el dispositivo electrónico 302 pueden ser opcionales. Por ejemplo, uno o más de los elementos ilustrados en el dispositivo electrónico 302 pueden o no estar incluidos y/o implementados. De forma adicional o alternativa, uno o más de los elementos ilustrados en el procesador 324 y/o el circuito VLIW 304 pueden implementarse por separado del procesador 324 y/o el circuito VLIW 304 (por ejemplo, en otros circuitos, en otro procesador, en un dispositivo electrónico separado, etc.). Por ejemplo, el sensor de imagen 316, el sistema óptico 318, la interfaz de comunicación 320, el procesador 324, el seguidor de ojos 326 y/o la pantalla 332 pueden no implementarse en el dispositivo electrónico 302. En algunas configuraciones, el dispositivo electrónico 302 puede recibir imágenes y/o información de seguimiento de los ojos desde otro dispositivo. De forma adicional o alternativa, se pueden implementar una o más pantallas en uno o más dispositivos separados.

[0062] En algunas configuraciones, el dispositivo electrónico 302 puede presentar una interfaz de usuario 334 en la pantalla 332. Por ejemplo, la interfaz de usuario 334 puede permitir que un usuario interactúe con el dispositivo electrónico 302. En algunas configuraciones, la pantalla 332 puede ser una pantalla táctil que recibe información del tacto físico (por ejemplo, con un dedo, un lápiz óptico u otra herramienta). De forma adicional o alternativa, el dispositivo electrónico 302 puede incluir o estar acoplado a otra interfaz de entrada. Por ejemplo, el dispositivo electrónico 302 puede incluir una cámara frente a un usuario y puede detectar gestos del usuario (por ejemplo, gestos con las manos, gestos con los brazos, seguimiento de los ojos, parpadeo de los párpados, etc.). En otro ejemplo, el

dispositivo electrónico 302 puede estar acoplado a un ratón y puede detectar un clic del ratón. Cabe señalar que puede que no sea necesaria la entrada del usuario en algunas configuraciones.

5

10

15

20

25

30

35

40

45

50

55

60

65

[0063] En algunas configuraciones, el dispositivo electrónico 302 puede incluir opcionalmente un sensor de movimiento (por ejemplo, giroscopio(s), el acelerómetro(s), etc.). Por ejemplo, el sensor de movimiento puede detectar movimiento y/o una orientación (del dispositivo electrónico 302, por ejemplo). En algunas configuraciones, la imagen que se renderiza puede basarse en información de movimiento y/u orientación. Por ejemplo, el dispositivo electrónico 302 puede ser una pantalla montada en la cabeza (por ejemplo, un casco de realidad virtual (VR), casco de realidad aumentada (AR), etc.), un vehículo (por ejemplo, automóvil, avión no tripulado, avión, etc.), un dispositivo móvil (por ejemplo, un teléfono inteligente) u otro dispositivo que pueda utilizar información de movimiento y/u orientación para renderizar una imagen. Por ejemplo, la información de movimiento y/u orientación puede indicar una dirección de visualización general en una escena renderizada. El dispositivo electrónico 302 puede renderizar la imagen basándose en esta dirección de visualización además de o de forma alternativa a partir de la información de seguimiento de los oios en algunas configuraciones. El uso de un sensor de movimiento puede ilustrar otro aspecto del funcionamiento asíncrono del controlador de memoria asíncrona 308. Por ejemplo, un sensor de movimiento puede proporcionar información de movimiento y/o información de orientación a la memoria (por ejemplo, memoria del sistema 314 y/o memoria en chip 310) a una velocidad particular (por ejemplo, 1000 hercios (Hz)), mientras que el circuito VLIW 304 puede procesar tramas a una velocidad comparativamente más baja (por ejemplo, 30 tramas por segundo (fps)). El controlador de memoria asíncrona 308 puede cambiar asíncronamente una o más operaciones de renderización (por ejemplo, teselación) en medio de la renderización de un conjunto de datos basándose en la información de movimiento y/o información de orientación.

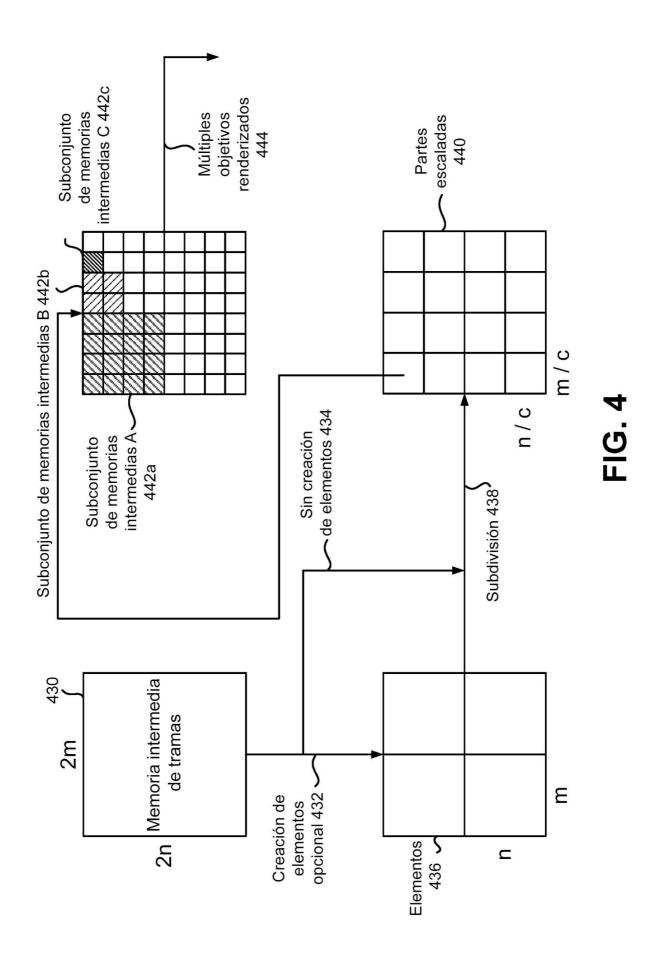

[0064] La Figura 4 es un diagrama que ilustra un ejemplo de una memoria intermedia de tramas no uniforme 430. En este ejemplo, la memoria intermedia de tramas 430 tiene una capacidad de 2n x 2m píxeles. En algunas configuraciones, el dispositivo electrónico 302 puede opcionalmente crear elementos 432 en la memoria intermedia de tramas 430 convirtiéndolos en elementos 436. En el ejemplo ilustrado en la Figura 4, se ilustran cuatro elementos 436 de tamaño (n, m). En algunas implementaciones, la memoria 310 en chip o una parte de la memoria 310 en chip puede estar limitada al tamaño de un elemento 436. En consecuencia, el dispositivo electrónico 302 puede dividir la memoria intermedia de tramas 430 en elementos 436. En otras implementaciones, la memoria en chip 310 o una parte de la memoria en chip 310 puede ser lo suficientemente grande como para contener toda la memoria intermedia de tramas 430 y no se puede realizar creación de elementos 434.

[0065] El dispositivo electrónico 302 puede subdividir 438 la memoria intermedia de tramas 430 y/o elementos 436 en partes a escala 440. Por ejemplo, la memoria intermedia de tramas 430 y/o los elementos 436 pueden subdividirse para adaptarse a múltiples resoluciones y/o niveles de detalle. En el ejemplo ilustrado en la Figura 4, las partes a escala 440 son de tamaño (n/c, m/c), donde c es un factor de escala. El factor de escala c puede variar y/o puede seleccionarse basándose en la configuración.

[0066] El dispositivo electrónico 302 (por ejemplo, el controlador 312 memoria intermedia de tramas no uniforme) puede acceder dinámicamente a diferentes subconjuntos 442a-c de la memoria intermedia de tramas 430. En el ejemplo, ilustrado en la Figura 4, el dispositivo electrónico 302 puede acceder dinámicamente al subconjunto de memorias intermedias A 442a, al subconjunto de memorias intermedias B 442b y al subconjunto de memorias intermedias C 442c. Cabe señalar que se pueden utilizar menos o más subconjuntos de memorias intermedias. También debe tenerse en cuenta que toda o solo una parte de la memoria intermedia de tramas 430 puede estar ocupada por subconjuntos de memorias intermedias. Por ejemplo, las otras partes no tramadas de la memoria intermedia de tramas pueden ser utilizadas por uno o más subconjuntos diferentes.

[0067] El acceso dinámico (por ejemplo, la lectura y/o escritura) de diferentes subconjuntos de memorias intermedias de tramas (por ejemplo, subconjuntos de memorias intermedias 442a-c) puede permitir uno o más enfoques para proporcionar un mayor control y/o eficiencia en la renderización de imágenes. En algunos enfoques, el acceso dinámico de diferentes subconjuntos de memorias intermedias de tramas puede permitir la renderización de múltiples LOD de una sola pasada. Esto se debe a que no es necesario completar una zona en un LOD antes de poder iniciar otra zona en un LOD diferente. En este enfoque, uno o más de los subconjuntos de memorias intermedias 442a-c pueden corresponder a diferentes zonas de imagen. Por ejemplo, el subconjunto de memorias intermedias A 442a puede corresponder a una zona con un LOD más alto, el subconjunto de memorias intermedias B 442b puede corresponder a una zona con un LOD medio y el subconjunto de memorias intermedias C 442c puede corresponder a una zona con un LOD más bajo. Por ejemplo, el circuito VLIW 304 puede renderizar una zona LOD más alto, que puede escribirse en el subconjunto de memorias intermedias A 442a mientras renderiza simultáneamente o secuencialmente una zona LOD media, que puede escribirse en el subconjunto de memorias intermedias B 442b. Cabe señalar que se pueden renderizar diferentes zonas LOD en cualquier orden (por ejemplo, Desde el LOD más alto al más bajo, en orden inverso u otro orden). De forma adicional o alternativa, el acceso dinámico de diferentes subconjuntos de memorias intermedias de tramas puede permitir el procesamiento de diferentes zonas a diferentes velocidades (por ejemplo, un subconjunto de memorias intermedias de tramas más grande se puede asignar para que una zona se procese más rápidamente, mientras que un subconjunto de memorias intermedias de tramas más pequeño se puede asignar para que otra zona sea procesada más lentamente).

[0068] En algunos enfoques, el acceso dinámico de diferentes subconjuntos de memorias intermedias de tramas puede permitir procesos de sombreador paralelos (por ejemplo, subrutinas). Por ejemplo, se pueden ejecutar diferentes procesos de sombreador en paralelo, donde un proceso de sombreador accede a un subconjunto de la memoria intermedia de tramas y otro proceso de sombreador accede a otro subconjunto de la memoria intermedia de tramas. De forma adicional o alternativa, el acceso dinámico de diferentes subconjuntos de memorias intermedias de tramas puede permitir el intercambio de subrutinas de sombreador. Por ejemplo, se puede ejecutar una primera subrutina de sombreador que acceda al subconjunto de memorias intermedias A 442a. Mientras la primera subrutina de sombreador está en curso, una segunda subrutina de sombreador que accede al subconjunto de memorias intermedias B 442b puede finalizar. La segunda subrutina de sombreador puede intercambiarse por otra subrutina de sombreador (que puede acceder al subconjunto de memorias intermedias B 442b, por ejemplo) mientras la primera subrutina de sombreador está en curso. Esto puede permitir una mayor eficiencia en la utilización del espacio de la memoria intermedia de tramas, en lugar de tener que esperar a que termine una subrutina de sombreado antes de que se pueda iniciar otra.

5

10

15

20

25

30

35

40

65

[0069] En algunos enfoques, el acceso dinámico de diferentes subconjuntos de memorias intermedias de tramas puede permitir la sustitución de la muestra. Por ejemplo, el controlador de memoria intermedia de tramas no uniforme 312 puede intercambiar una o más muestras de un píxel procesado por una o más muestras de otro píxel. En algunas configuraciones, el circuito VLIW 304 puede realizar suavizado (por ejemplo, suavizado de múltiples muestras (MSAA)). Al realizar el suavizado, diferentes píxeles pueden tener diferentes números de muestras. Por ejemplo, un primer píxel (por ejemplo, "fino") en el subconjunto de memorias intermedias A 442a puede tener 4 muestras y puede usar sombreado de mayor calidad, mientras que un segundo píxel cercano (por ejemplo, contiguo) (por ejemplo, "grueso") en el subconjunto de memorias intermedias B 442b puede tener 1 muestra y usar sombreado de menor calidad. En lugar de realizar el procesamiento (por ejemplo, sombreado) en el segundo píxel, el controlador de memoria intermedia de tramas no uniforme 312 puede sustituir una muestra del primer píxel por una muestra del segundo píxel. Esto puede evitar realizar cualquiera de los procesamientos para el segundo píxel. De forma adicional o alternativa, el controlador de memoria intermedia de tramas no uniforme 312 puede realizar la sustitución de muestras en el procesamiento de mapas MIP. Por ejemplo, el controlador de memoria intermedia de tramas no uniforme 312 puede sustituir una muestra de un nivel superior (en el subconjunto de memorias intermedias A 442a, por ejemplo) por una muestra de un nivel inferior (en el subconjunto de memorias intermedias B 442b, por ejemplo). Esto puede evitar algo o procesamiento en uno o más niveles inferiores.

[0070] El controlador de memoria intermedia de tramas no uniforme 312 puede permitir el envío dinámico del procesamiento de sombreado (por ejemplo, subrutinas, núcleos, etc.), puede permitir la sustitución de la muestra de píxeles y/o puede proporcionar una memoria intermedia de tramas de múltiples LOD. Como se ilustra en la Figura 4, la memoria intermedia de tramas 430 puede almacenar datos de imágenes que pueden transmitirse como múltiples objetivos renderizados 444.

[0071] El listado (1) ilustra un ejemplo de pseudocódigo que ilustra un enfoque para la funcionalidad de memoria intermedia de tramas no uniforme. Cabe señalar que GLSL es una abreviatura de OpenGL Shading Language y SSBO es una abreviatura de Shader Storage Buffer Object. El Listado (1) ilustra cómo múltiples zonas con diferentes niveles de detalle

60 [0072] La Figura 5 es un diagrama de flujo que ilustra una configuración más específica de un procedimiento 500 para renderizar múltiples niveles de detalle. El procedimiento 500 puede ser realizado por el dispositivo electrónico 302 descrito en relación con la Figura 3.

[0073] El dispositivo electrónico 302 puede obtener 502 datos de geometría (por ejemplo, datos de geometría 328). Esto se puede conseguir como se ha descrito en relación con una o más de las Figuras 1-3. Por ejemplo, el dispositivo electrónico 302 puede cargar datos de geometría desde el almacenamiento en la memoria (por ejemplo, memoria del

sistema 314 y/o memoria en chip 310) y/o puede recibir datos de geometría de otro dispositivo y cargar los datos de geometría en la memoria (por ejemplo, memoria del sistema 314 y/o memoria en chip 310).

[0074] El dispositivo electrónico 302 puede llevar a cabo 504 seguimiento de los ojos. Esto se puede conseguir como se ha descrito en relación con la Figura 3. Por ejemplo, el dispositivo electrónico 302 puede obtener (por ejemplo, capturar y/o recibir) una o más imágenes y puede determinar hacia dónde se dirige la mirada de un usuario (por ejemplo, dónde mira un usuario en una pantalla y/o una imagen que se presenta en la pantalla) basándose en la una o más imágenes.

5

25

30

35

40

45

50

55

60

65

10 [0075] El dispositivo electrónico 302 puede renderizar 506 diferentes niveles de detalle asíncronamente basándose en el seguimiento de los ojos. Esto se puede conseguir como se ha descrito anteriormente en relación con una o más de las Figuras 1-3. Por ejemplo, el dispositivo electrónico 302 puede acceder asíncronamente a la memoria (por ejemplo, memoria del sistema 314 y/o memoria en chip 310) para renderizar diferentes niveles de detalle basándose en el seguimiento de los ojos. Por ejemplo, el dispositivo electrónico 302 puede cambiar un LOD para un conjunto de datos durante el procesamiento (donde el conjunto de datos inicialmente tenía un LOD diferente, por ejemplo) cuando la zona para el conjunto de datos cambia basándose en el seguimiento de los ojos. En algunas configuraciones, el dispositivo electrónico 302 puede aumentar el LOD para el conjunto de datos cuando la mirada de un usuario se dirige a un área de la imagen correspondiente al conjunto de datos. De forma adicional o alternativa, el dispositivo electrónico 302 puede disminuir el LOD para el conjunto de datos cuando la dirección de la mirada de un usuario se aleja de un área de la imagen correspondiente al conjunto de datos.

[0076] En algunas configuraciones, la renderización 506 de diferentes niveles de detalle asíncronamente puede incluir realizar teselación de LOD dinámica. Por ejemplo, la memoria (por ejemplo, la memoria del sistema 314 y/o la memoria en chip 310) puede actualizarse para indicar un cambio en los parámetros de teselación de LOD (por ejemplo, un grado de teselación). El controlador de memoria asíncrona 308 puede acceder al parámetro de teselación de LOD actualizado para cambiar la teselación de LOD asíncronamente.

[0077] El dispositivo electrónico 302 puede acceder dinámicamente a 508 subconjuntos diferentes de una memoria intermedia de tramas. Esto se puede conseguir como se ha descrito anteriormente en relación con una o más de las Figuras 1-4. Por ejemplo, el dispositivo electrónico 302 puede acceder al menos a un píxel de una primera zona a una velocidad diferente de al menos un píxel de una segunda zona. De forma adicional o alternativa, el dispositivo electrónico 302 puede permitir el intercambio de subrutinas de sombreador cuando el procesamiento de un primer píxel está en curso y se completa el proceso de un segundo píxel. De forma adicional o alternativa, el dispositivo electrónico 302 puede sustituir una primera muestra procesada de un primer píxel por una segunda muestra de un segundo píxel para evitar procesar la segunda muestra del segundo píxel.

[0078] El dispositivo electrónico 302 puede presentar 510 la imagen renderizada. Por ejemplo, el dispositivo electrónico 302 puede transmitir datos de imágenes que se han renderizado 506 con diferentes niveles de detalle asíncronamente. En algunas configuraciones, los datos de imágenes pueden proporcionarse a una pantalla integrada 332. En otras configuraciones, los datos de imágenes pueden proporcionarse a una pantalla remota que está en comunicación con el dispositivo electrónico 302. Por ejemplo, el dispositivo electrónico 302 puede proporcionar los datos de imágenes a una pantalla que está acoplada al dispositivo electrónico 302 (a través de VGA, DVI, HDMI, etc.)

[0079] La Figura 6 es un diagrama de flujo que ilustra un ejemplo de un procedimiento 600 para la renderización con resolución variable. En este procedimiento, se obtienen datos de geometría 602. El seguimiento de los ojos también se realiza 604. Una capa gruesa se renderiza 606, una capa media se renderiza 608 y una capa fina se renderiza 610. Por ejemplo, la capa fina se puede renderizar 610 en una imagen a la que se dirige la mirada de un usuario. La capa media se puede renderizar 608 en un área más grande que se superpone al área de capa fina. La capa gruesa se puede renderizar 606 en un área aún más grande (por ejemplo, la imagen completa) que incluye el área de capa media y el área de capa fina. En consecuencia, puede haber una superposición significativa entre las capas. La capa gruesa, la capa media y la capa fina pueden fusionarse 612 con suavizado. La imagen resultante puede enviarse 614 a la memoria intermedia de tramas.