# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

(1) Número de publicación: 2801 598

61 Int. Cl.:

**G06F 1/3237** (2009.01)

(12)

### TRADUCCIÓN DE PATENTE EUROPEA

T3

86 Fecha de presentación y número de la solicitud internacional: 27.11.2017 PCT/US2017/063306

(87) Fecha y número de publicación internacional: 21.06.2018 WO18111526

(96) Fecha de presentación y número de la solicitud europea: 27.11.2017 E 17817485 (0)

(97) Fecha y número de publicación de la concesión europea: 22.04.2020 EP 3555726

(54) Título: Generación de habilitación de compuertas de reloj

(30) Prioridad:

13.12.2016 US 201662433547 P 01.08.2017 US 201715666107

Fecha de publicación y mención en BOPI de la traducción de la patente: 11.01.2021

(73) Titular/es:

QUALCOMM INCORPORATED (100.0%) 5775 Morehouse Drive San Diego, CA 92121-1714, US

(72) Inventor/es:

**ZERWICK, ADAM ANDREW**

(74) Agente/Representante:

FORTEA LAGUNA, Juan José

#### **DESCRIPCIÓN**

Generación de habilitación de compuertas de reloj

#### 5 REFERENCIA CRUZADA A SOLICITUDES RELACIONADAS

**[0001]** La presente solicitud reivindica la prioridad y el beneficio de la solicitud provisional n.º 62/433,547 presentada en la Oficina de Patentes y Marcas de EE. UU. el 13 de diciembre de 2016, y la solicitud no provisional n.º 15/666,107 presentada en la Oficina de Patentes y Marcas de EE. UU, el 1 de agosto de 2017.

#### **ANTECEDENTES**

#### Campo

10

15 **[0002]** Los aspectos de la presente divulgación se refieren a las compuertas de reloj, y más en particular, a la generación de habilitación de compuertas de reloj.

#### **Antecedentes**

- 20 [0003] Reducir el consumo de energía en un dispositivo móvil es importante para prolongar la vida útil de la batería del dispositivo móvil. Un contribuyente significativo al consumo de energía de un chip (una pastilla) en un dispositivo móvil es la energía dinámica, que se debe a la conmutación de los transistores en el chip. En este sentido, se han diseñado diversos sistemas de reducción de energía para reducir el consumo de energía dinámica en un chip. Un sistema conlleva bloquear el paso de una señal de reloj hacia un circuito (por ejemplo, una canalización) en el chip cuando el circuito no está en uso (por ejemplo, no está procesando datos). El bloqueo del paso de la señal de reloj hacia el circuito detiene la conmutación de los transistores del circuito, reduciéndose de este modo la energía dinámica.

- [0004] Se llama la atención sobre el documento US 2004/032855 A1 que describe un circuito de procesamiento de datos de comunicación que controla adecuadamente una operación de activación/desactivación de señales de reloj, con lo cual se reduce por tanto eficazmente el consumo de energía. El circuito de procesamiento de datos de comunicación procesa datos de comunicación en base a una señal de reloj que se va a introducir. El circuito de procesamiento de datos de comunicación incluye una sección de procesamiento de paquetes para procesar datos de comunicación, un contador de paquetes para discernir entre la presencia y la ausencia de datos de comunicación en proceso en la sección de procesamiento de paquetes, y un controlador de reloj para introducir o detener una señal de reloj destinada a la sección de procesamiento de paquetes como respuesta a una salida del contador de paquetes.

- [0005] Se llama además la atención sobre el documento EP 2 124 130 A2 que describe un procesador de paquetes que tiene una o dos o más unidades de procesamiento de paquetes con un detector de paquetes que detecta si existe o no un paquete en una unidad de procesamiento de paquetes, y facilita una señal de detección de paquetes que indica un resultado de la detección, y un controlador de frecuencia de reloj que controla un reloj que se va a suministrar a la unidad de procesamiento de paquetes en base a la señal de detección de paquetes.

#### 45 BREVE EXPLICACIÓN

60

65

[0006] La presente invención se expone en las reivindicaciones independientes, respectivamente. Los modos de realización preferentes de la invención se describen en las reivindicaciones dependientes.

- 50 [0007] A continuación, se presenta un sumario simplificado de uno o más modos de realización para permitir una comprensión básica de dichos modos de realización. Este sumario no es una visión general amplia de todos los modos de realización contemplados y no pretende identificar ni elementos clave o cruciales de todos los modos de realización ni delimitar el alcance de algunos o de todos los modos de realización. Su único propósito es presentar algunos conceptos de uno o más modos de realización de manera simplificada como preludio a la descripción más detallada que se presenta posteriormente.

- [0008] Un aspecto se refiere a un sistema de compuertas de reloj para una canalización. El sistema de compuertas de reloj incluye un dispositivo de compuertas de reloj configurado para bloquear o dejar pasar una señal de reloj hacia la canalización, y un controlador de reloj. El controlador de reloj está configurado para hacer un seguimiento de un número de paquetes de entrada en una entrada de la canalización, hacer un seguimiento de un número de paquetes de salida en una salida de la canalización, determinar si se ha de bloquear o dejar pasar la señal de reloj en base al número de los paquetes de entrada y el número de los paquetes de salida, ordenar al dispositivo de compuertas de reloj que deje pasar la señal de reloj si se determina dejar pasar la señal de reloj, y ordenar al dispositivo de compuertas de reloj que bloquee la señal de reloj si se determina bloquear la señal de reloj.

[0009] Un segundo aspecto se refiere a un procedimiento de compuertas de reloj. El procedimiento incluye hacer un seguimiento de un número de paquetes de entrada en una entrada de una canalización, hacer un seguimiento de un número de paquetes de salida en una salida de la canalización y determinar si se debe bloquear o dejar pasar una señal de reloj hacia la canalización en base al número de los paquetes de entrada y el número de los paquetes de salida. El procedimiento también incluye dejar pasar la señal de reloj hacia la canalización si se determina dejar pasar la señal de reloj, y bloquear la señal de reloj si se determina bloquear la señal de reloj.

**[0010]** Para conseguir los fines anteriores y otros relacionados, el uno o más modos de realización incluyen las características descritas en mayor detalle más adelante en el presente documento y expuestas en particular en las reivindicaciones. La descripción siguiente y los dibujos adjuntos exponen con detalle determinados aspectos ilustrativos del uno o más modos de realización.

#### BREVE DESCRIPCIÓN DE LOS DIBUJOS

#### 15 **[0011]**

5

10

20

25

35

50

60

65

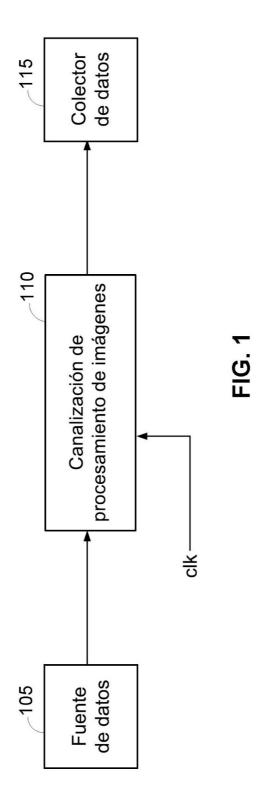

- La FIG. 1 muestra un ejemplo de canalización de procesamiento de imágenes.

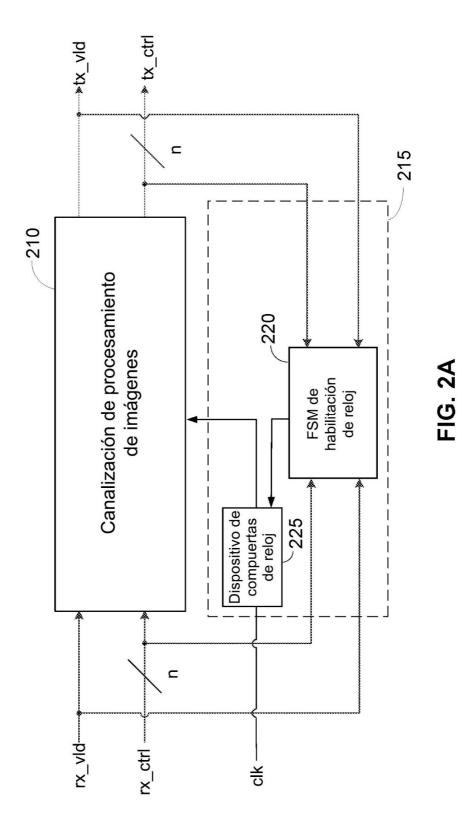

- La FIG. 2A muestra un ejemplo de sistema de compuertas de reloj que incluye una máquina de estados finitos.

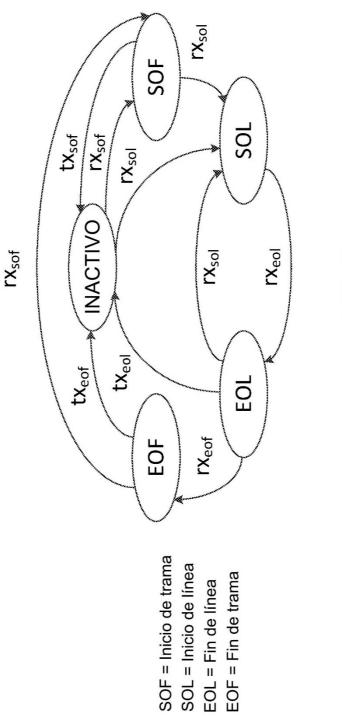

- La FIG. 2B muestra un diagrama de estados ejemplar para la máquina de estados finitos de la FIG. 2A.

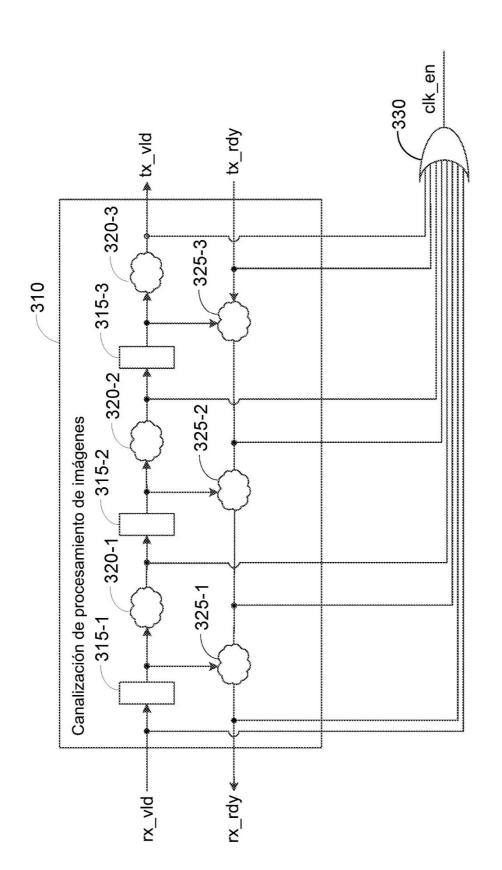

- La FIG. 3 muestra un ejemplo de sistema de compuertas de reloj configurado para verificar si hay datos válidos y/o una señal de listo en cada fase de una canalización.

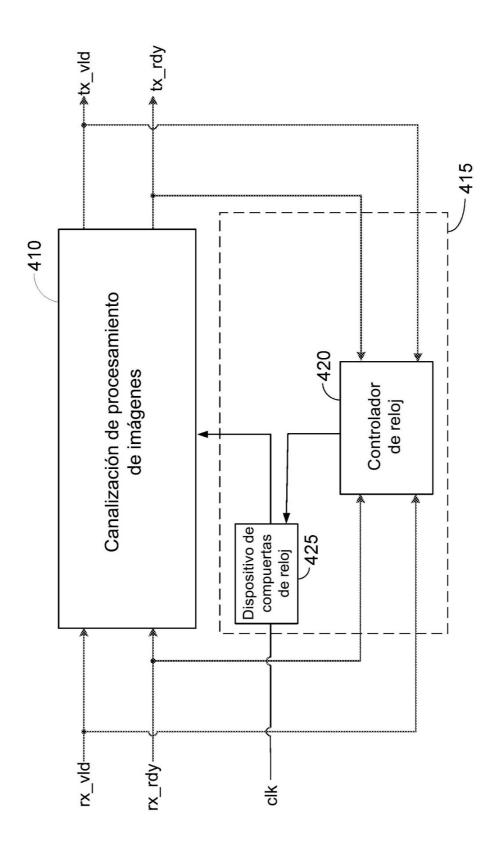

- La FIG. 4 muestra un ejemplo de sistema de compuertas de reloj de acuerdo con unos aspectos de la presente divulgación.

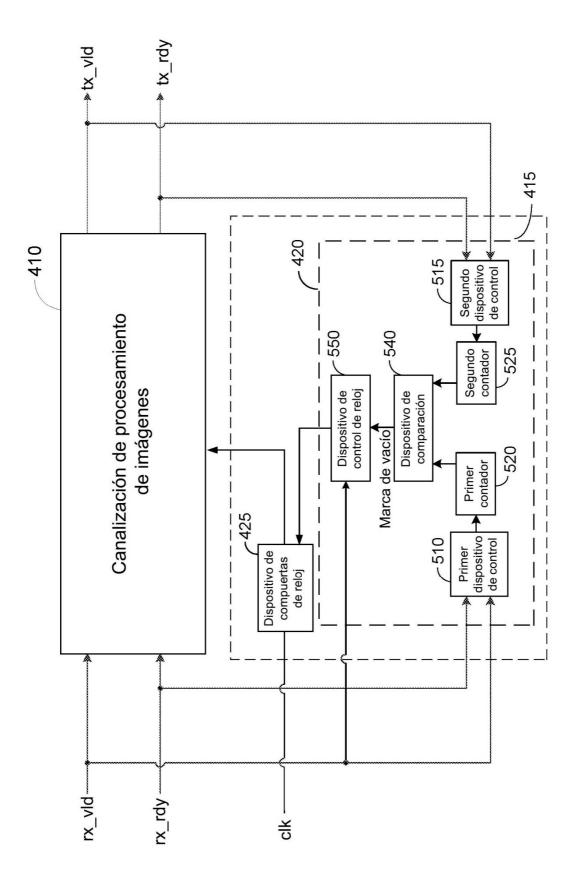

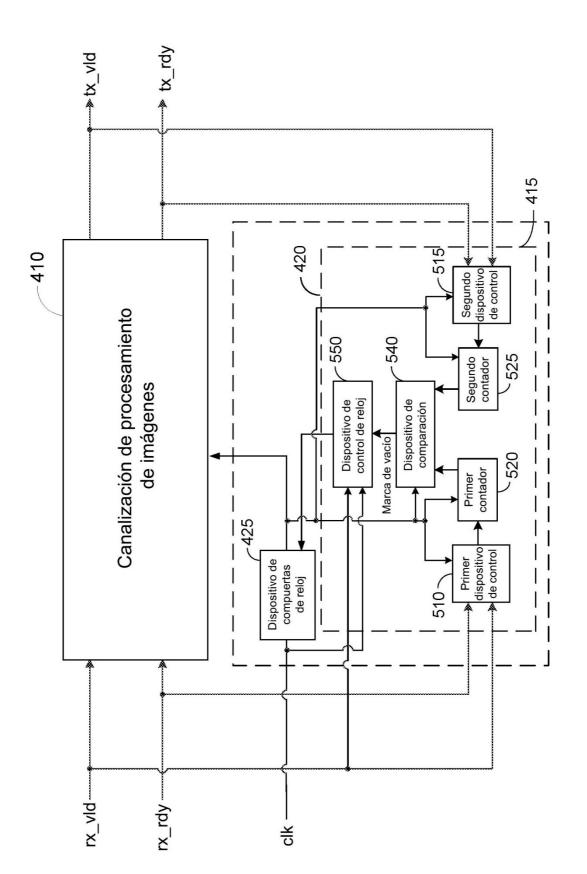

- La FIG. 5 muestra una implementación ejemplar de un controlador de reloj de acuerdo con determinados aspectos de la presente divulgación.

- La FIG. 6 muestra un ejemplo en el que el controlador de reloj de la FIG. 5 recibe una señal de reloj para operaciones de temporización del controlador de reloj de acuerdo con determinados aspectos de la presente divulgación.

- La FIG. 7 es una tabla que muestra ejemplos de áreas de chips para diferentes procedimientos de compuertas de reloi y diferentes profundidades de canalización.

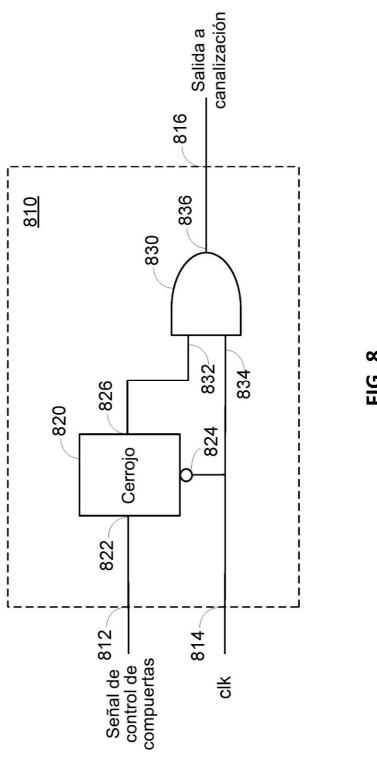

- La FIG. 8 muestra un ejemplo de celda de compuertas de reloj (CGC) que se puede usar en un sistema de compuertas de reloj de acuerdo con determinados aspectos de la presente divulgación.

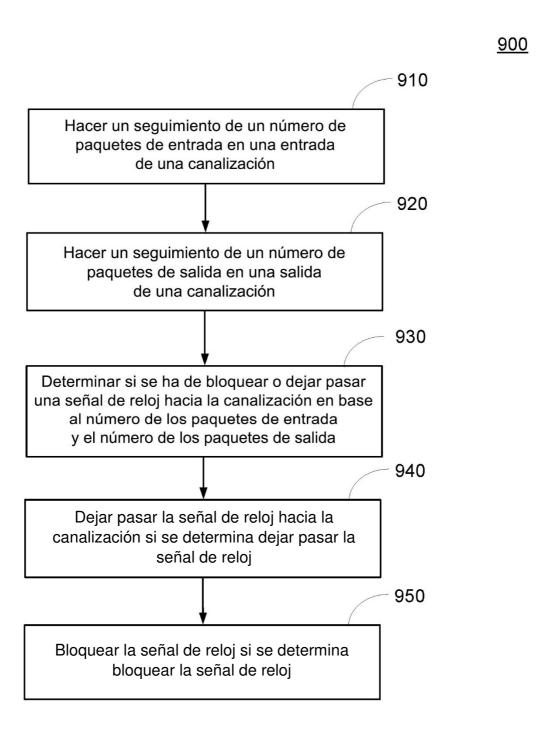

- La FIG. 9 es un diagrama de flujo que ilustra un procedimiento para compuertas de reloj de acuerdo con determinados aspectos de la presente divulgación.

#### 45 **DESCRIPCIÓN DETALLADA**

- [0012] La descripción detallada expuesta a continuación, en relación con los dibujos adjuntos, pretende ser una descripción de diversas configuraciones y no pretende representar las únicas configuraciones en las cuales se pueden llevar a la práctica los conceptos descritos en el presente documento. La descripción detallada incluye detalles específicos con el propósito de permitir una plena comprensión de los diversos conceptos. Sin embargo, resultará evidente a los expertos en la técnica que estos conceptos se pueden llevar a la práctica sin estos detalles específicos. En algunos casos, se muestran estructuras y componentes bien conocidos en forma de diagrama de bloques para evitar ofuscar dichos conceptos.

- [0013] Un sistema puede incluir una canalización configurada para procesar datos de una fuente de datos, y facilitar los datos procesados a un colector de datos. La canalización incluye múltiples fases de canalización (también denominadas unidades o elementos de procesamiento) que procesan los datos (por ejemplo, secuencialmente). Se puede usar una canalización, por ejemplo, para procesar datos de imagen de una fuente de datos de imagen, tal como un sensor de cámara o una memoria.

- [0014] A este respecto, la FIG. 1 muestra un ejemplo de canalización de procesamiento de imágenes 110 (también denominado módulo de procesamiento de señales de imagen (ISP)). La canalización de procesamiento de imágenes 110 recibe datos (por ejemplo, datos de imagen) desde una fuente de datos 105 (por ejemplo, un sensor de cámara, una memoria, etc.). La canalización de procesamiento de imágenes 110 procesa los datos recibidos y facilita los datos procesados (por ejemplo, datos de imagen procesados) a un colector de datos 115 (por ejemplo, un procesador de visualización, una unidad central de procesamiento (CPU), una memoria, etc.). La

canalización de procesamiento de imágenes 110 incluye múltiples fases de canalización para procesar los datos. El procesamiento de imágenes puede incluir uno o más de los siguientes: filtrado de ruido, corrección de color, correlación de tonos, interpolación cromática, etc.

- [0015] La canalización de procesamiento de imágenes 110 recibe una señal de reloj (denominada "clk") para operaciones de temporización de la canalización de procesamiento de imágenes 110. La señal de reloj clk se requiere para que la canalización de procesamiento de imágenes 110 procese datos. Sin embargo, hay determinados períodos de tiempo (por ejemplo, entre tramas) durante los cuales no hay datos en la canalización de procesamiento de imágenes 110 que se deban procesar. Durante estos períodos de tiempo, es deseable bloquear (inhabilitar) el paso de la señal de reloj clk hacia la canalización de procesamiento de imágenes 110 para ahorrar energía. El bloqueo de la señal de reloj clk reduce el consumo de energía dinámica al detener la conmutación de transistores en la canalización de procesamiento de imágenes 110 cuando no hay datos en la canalización 110 que se deban procesar.

- [0016] La FIG. 2A muestra un ejemplo de compuertas de reloj de acuerdo con un enfoque. En este enfoque, un sistema de compuertas de reloj 215 incluye una máquina de estados finitos (FSM) de habilitación de reloj 220 y un dispositivo de compuertas de reloj 225. El dispositivo de compuertas de reloj 225 está configurado para bloquear y dejar pasar selectivamente la señal de reloj clk hacia la canalización de procesamiento de imágenes 210 bajo el control de la FSM 220, como se describe en mayor detalle a continuación.

20

25

30

35

40

45

- [0017] En este ejemplo, la canalización de procesamiento de imágenes 210 recibe datos válidos (por ejemplo, datos de píxeles) de la fuente de datos (no mostrada en la FIG. 2A) en tramas, en la que cada trama incluye múltiples líneas de datos válidos. En la FIG. 2A, los datos válidos recibidos por la canalización de procesamiento de imágenes 210 desde la fuente de datos se denotan por "rx vld", y los datos válidos facilitados por la canalización de procesamiento de imágenes 210 al colector de datos (no mostrado en la FIG.2A) se denotan por "tx\_vld".

- [0018] En este ejemplo, la canalización de procesamiento de imágenes 210 recibe una señal de control de recepción (denotada por "rx\_ctrl") desde la fuente de datos, y facilita una señal de control de transmisión (denotada por "tx\_ctrl") al colector de datos. La señal de control de recepción rxctrl incluye marcadores que indican el inicio de una trama de entrada (denotado por "rxeol"), el final de una trama de entrada (denotado por "rxeol"), el final de una línea de entrada (denotado por "rxeol"). La señal de control de transmisión tx\_ctrl incluye marcadores que indican el inicio de una trama de salida (denotado por "txeol"), el final de una línea de salida (denotado por "txeol"), y el final de una línea de salida (denotado por "txeol"), y el final de una línea de salida (denotado por "txeol").

- [0019] En funcionamiento, la FSM 220 recibe la señal de control de recepción rx\_ctrl y la señal de control de transmisión tx\_ctrl, y determina si se ha de ordenar al dispositivo de compuertas de reloj 225 que bloquee (inhabilite) la señal de reloj clk o deje pasar (habilite) la señal de reloj clk en base a las señales de control recibidas. Por ejemplo, la FSM 220 puede ordenar al dispositivo de compuertas de reloj 225 que bloquee (inhabilite) la señal de reloj clk entre el final de una trama de salida (txeol) y el inicio de la siguiente trama de entrada (rxsol), suponiendo que no haya datos válidos entre tramas adyacentes. La FSM 220 también puede ordenar al dispositivo de compuertas de reloj 225 que bloquee (inhabilite) la señal de reloj clk entre el final de una línea de salida (txeol) y el inicio de la siguiente línea de entrada (rxsol), suponiendo que no haya datos válidos entre líneas adyacentes. Por tanto, la FSM 220 puede bloquear (inhabilitar) la señal de reloj clk entre tramas adyacentes y entre líneas adyacentes dentro de una trama para reducir el consumo de energía. La FIG. 2B muestra un diagrama de máquina de estados ejemplar para la FSM 220 de acuerdo con determinados aspectos, en la que la señal de reloj clk se bloquea en el estado inactivo.

- [0020] Un inconveniente de este enfoque es que la FSM 220 no bloquea (inhabilita) la señal de reloj clk cuando hay una o más "burbujas" dentro de una línea activa, en el que una burbuja es un espacio sin datos válidos. Por tanto, este enfoque pierde oportunidades para bloquear (inhabilitar) la señal de reloj clk durante determinados períodos de tiempo cuando no hay datos válidos en la canalización 210, desperdiciando de este modo energía.

- [0021] La FIG. 3 muestra un ejemplo de compuertas de reloj de acuerdo con otro enfoque. En este enfoque, la canalización de procesamiento de imágenes 310 recibe datos válidos rx\_vld desde la fuente de datos (no mostrada en la FIG.3), y facilita datos válidos tx\_vld al colector de datos (no mostrado en la FIG.3). Además, la canalización de procesamiento de imágenes 310 facilita una señal de listo para recepción (denominada "rx\_rdy") a la fuente de datos para indicar a la fuente de datos que la canalización de procesamiento de imágenes 310 está lista para recibir datos válidos desde la fuente de datos. La canalización de procesamiento de imágenes 310 también recibe una señal de listo para transmisión (denotada por "tx\_rdy") desde el colector de datos que indica que el colector de datos está listo para recibir datos válidos desde la canalización de procesamiento de imágenes 310.

- [0022] En este ejemplo, la canalización de procesamiento de imágenes 310 incluye unos cerrojos 315-1 a 315-3 para enclavar datos válidos (por ejemplo, datos de píxeles) en diferentes puntos de la canalización de procesamiento de imágenes 310, y unas unidades de procesamiento 320-1 a 320-3 (por ejemplo, lógica combinatoria) configuradas para procesar datos válidos en diferentes fases de canalización. La canalización de

procesamiento de imágenes 310 también incluye una lógica 325-1 a 325-3 para generar la señal de listo para recepción rx\_rdy. Por ejemplo, la lógica 325-1 a 325-3 puede verificar si en los cerrojos hay datos válidos y verificar la señal de listo para transmisión tx\_rdy para determinar si la canalización 310 está lista para recibir más datos válidos desde la fuente de datos. Por ejemplo, la lógica 325-1 a 325-3 puede dejar de imponer la señal de listo para recepción rx\_rdy si los cerrojos están llenos y la señal de listo para transmisión tx\_rdy no se impone. En este caso, la canalización 310 puede estar llena y no puede facilitar (transmitir) datos válidos al colector de datos para dejar espacio en la canalización 310 a más datos válidos. Los cerrojos 315-1 a 315-3, las unidades de procesamiento 320-1 a 320-3 y/o la lógica 325-1 a 325-3 se pueden temporizar usando la señal de reloj clk (no mostrada en la FIG.3).

[0023] En este ejemplo, el sistema de compuertas de reloj incluye una lógica de control de compuertas de reloj 330 (representada como una compuerta OR en la FIG.3) que verifica si hay datos válidos en la canalización 310. La lógica de control de compuertas de reloj 330 realiza esta tarea verificando si hay datos válidos y/o una señal de listo en cada una de las fases de la canalización. Si la lógica de control de compuertas de reloj 330 detecta datos válidos y/o una señal de listo en al menos uno de los estados de canalización, la lógica de control de compuertas de reloj 330 habilita el paso de (deja pasar) la señal de reloj clk hacia la canalización de procesamiento de imágenes 310. Si la lógica de control de compuertas de reloj 330 no detecta ningún dato válido y/o señal de listo, la lógica de control de compuertas de reloj 330 inhabilita (bloquea) la señal de reloj clk.

[0024] A diferencia del enfoque de compuertas de reloj previo analizado anteriormente con referencia a la FIG. 2A, este enfoque puede bloquear (inhabilitar) el reloj de la señal de reloj clk durante una burbuja (espacio sin datos válidos) dentro de una línea activa. Esto se debe a que este enfoque bloquea (inhabilita) el reloj de la señal de reloj clk cuando no hay datos válidos en la canalización 310. Sin embargo, este enfoque potencialmente puede dar lugar a problemas relacionados con la temporización cuando la profundidad de la canalización es grande, las frecuencias de reloj son altas, etc. Esto es así porque el abanico de entrada (es decir, el número de entradas) en la lógica de control de compuertas de reloj 330 se incrementa a medida que la profundidad de canalización (número de fases de canalización) se incrementa. El incremento en el abanico de entrada incrementa los retardos de propagación en la lógica de control de compuertas de reloj 330, lo que hace que sea más difícil para la lógica de control de compuertas de reloj 330 cumplir determinados requisitos de temporización para un funcionamiento adecuado, especialmente a altas frecuencias. Como resultado, es difícil mejorar la canalización 310 usando este enfoque.

**[0025]** La FIG. 4 muestra un sistema de compuertas de reloj 415, de acuerdo con determinados aspectos de la presente divulgación. El sistema de compuertas de reloj 415 incluye un controlador de reloj 420 y un dispositivo de compuertas de reloj 425. El dispositivo de compuertas de reloj 425 está configurado para bloquear o dejar pasar selectivamente la señal de reloj clk hacia la canalización de procesamiento de imágenes 410 bajo el control del controlador de reloj 420, como se describe en mayor detalle a continuación.

[0026] En funcionamiento, la canalización de procesamiento de imágenes 410 recibe datos válidos (por ejemplo, datos de píxeles) desde la fuente de datos en paquetes y facilita datos válidos (por ejemplo, datos de píxeles) al colector de datos en paquetes. Cada paquete puede incluir N bits de datos válidos (por ejemplo, de 8 a 14 bits). El controlador de reloj 420 hace un seguimiento del número de paquetes de entrada en la entrada de la canalización de procesamiento de imágenes 410 (número de paquetes recibidos por la canalización de procesamiento de imágenes 410). El controlador de reloj 420 también hace un seguimiento del número de paquetes de salida en la salida de la canalización de procesamiento de imágenes 410). En un ejemplo, el controlador de reloj 420 hace un seguimiento del número de paquetes de entrada cuando se impone la señal de listo para recepción rx rdy, y hace un seguimiento del número de paquetes de salida cuando se impone la señal de listo para transmisión tx rdy. En otro ejemplo, el controlador de reloj 420 hace un seguimiento del número de paquetes de salida independientemente de la señal de listo para recepción rx\_rdy y la señal de listo para transmisión tx rdy, respectivamente.

[0027] El controlador de reloj 420 compara a continuación el número de paquetes de entrada con el número de paquetes de salida para determinar si la canalización de procesamiento de imágenes 410 está vacía (no hay datos válidos en la canalización 410). Por ejemplo, el controlador de reloj 420 puede determinar que la canalización 410 está vacía cuando el número de paquetes de entrada y el número de paquetes de salida coinciden, y determinar que la canalización 410 no está vacía cuando el número de paquetes de entrada y el número de paquetes de salida no coinciden.

[0028] Si el controlador de reloj 420 determina que la canalización 410 está vacía, el controlador de reloj 420 puede ordenar al dispositivo de compuertas de reloj 425 que bloquee (inhabilite) el paso de la señal de reloj clk hacia la canalización 410 para ahorrar energía. En un ejemplo, después de determinar que la canalización 410 está vacía, el controlador de reloj 420 también puede verificar si hay un paquete de entrada de datos válidos en la entrada de la canalización 410. Si el controlador de reloj 420 no detecta un paquete de entrada de datos válidos, el controlador de reloj 420 puede ordenar al dispositivo de compuertas de reloj 425 que bloquee (inhabilite) el paso de la señal de reloj clk hacia la canalización 410.

[0029] Si el controlador de reloj 420 determina que la canalización 410 no está vacía, el controlador de reloj 420 puede dejar la señal de reloj clk habilitada (sin bloquear).

[0030] Después de que se haya bloqueado (inhabilitado) el paso de la señal de reloj clk hacia la canalización 410, el controlador de reloj 420 puede establecer si en la entrada de la canalización 410 hay un paquete de entrada de datos válidos. Si el controlador de reloj 420 detecta un paquete de entrada, el controlador de reloj 420 habilita (deja pasar) la señal de reloj clk de modo que la canalización 410 pueda comenzar a procesar el paquete de entrada. Si el controlador de reloj 420 no detecta un paquete de entrada, el controlador de reloj 420 deja la señal de reloj clk inhabilitada (bloqueada). En un ejemplo, el controlador de reloj 420 establece si en la entrada de la canalización 410 hay un paquete de entrada cuando se impone la señal de listo para recepción rx\_rdy. En este ejemplo, la canalización 410 retiene la señal de listo para recepción rx\_rdy cuando la señal de reloj clk está bloqueada. En otro ejemplo, el controlador de reloj 420 establece si en la entrada de la canalización 410 hay un paquete de entrada independiente de la señal de listo para recepción rx rdy.

5

10

50

55

- 15 **[0031]** El controlador de reloj 420 es ventajoso con respecto al primer enfoque de compuertas de reloj analizado anteriormente con referencia a la FIG. 2A, en la medida en que el controlador de reloj 420 puede bloquear la señal de reloj clk durante una burbuja dentro de una línea activa. Esto se debe a que el controlador de reloj 420 bloquea la señal de reloj clk cuando la canalización 410 queda vacía durante la burbuja.

- 20 [0032] Además, el controlador de reloj 420 es ventajoso con respecto al segundo enfoque de compuertas de reloj analizado anteriormente con referencia a la FIG. 3 en la medida en que el controlador de reloj 420 tiene un pequeño abanico de entrada (número de entradas) en comparación con la lógica de control de compuertas de reloj 330 mostrada en la FIG. 3. Esto es así porque el controlador de reloj 420 verifica la entrada y la salida de la canalización 410 en lugar de verificar si en cada fase de canalización 410 hay datos válidos y/o una señal de listo. Como resultado, no es necesario incrementar el abanico de entrada del controlador de reloj 420 a medida que se añaden más fases de canalización, lo que hace que este enfoque sea más escalable. El abanico de entrada relativamente pequeño de este enfoque mitiga los problemas de temporización asociados con el segundo enfoque de compuertas de reloj analizado anteriormente.

- [0033] La FIG. 5 muestra una implementación ejemplar del controlador de reloj 420 de acuerdo con determinados de la presente divulgación. En este ejemplo, el controlador de reloj 420 incluye un primer dispositivo de control 510, un primer contador 520, un segundo dispositivo de control 515, un segundo contador 525, un dispositivo de comparación 540 y un dispositivo de control de reloj 550. El primer contador 520 está configurado para contar un número de paquetes de entrada, y el segundo contador 515 está configurado para contar un número de paquetes de salida, como se analiza en mayor detalle a continuación. Cada contador puede ser un contador de vuelta a cero que se pone a cero cuando se alcanza un valor máximo del contador.

- [0034] En funcionamiento, el primer dispositivo de control 510 establece si en la entrada de la canalización 410 hay paquetes de entrada de datos válidos (por ejemplo, cuando se impone la señal de listo para recepción rx\_rdy).

40 Por ejemplo, se puede indicar cada paquete de entrada mediante un indicador de paquete (por ejemplo, un delimitador). El indicador de paquete puede estar localizado al principio del paquete o al final del paquete. En este ejemplo, el primer dispositivo de control 510 puede detectar un paquete de entrada detectando el indicador de paquete respectivo. El primer dispositivo de control 510 puede incrementar el valor de recuento del primer contador 520 cada vez que el primer dispositivo de control 510 detecta un paquete de entrada. Por tanto, en este ejemplo, el primer contador 520 hace un seguimiento de un número de paquetes de entrada.

- [0035] El segundo dispositivo de control 515 establece si en la salida de la canalización 410 hay paquetes de salida de datos válidos (por ejemplo, cuando se impone la señal de listo para transmisión tx\_rdy). Por ejemplo, se puede indicar cada paquete de salida mediante un indicador de paquete (por ejemplo, un delimitador). El indicador de paquete puede estar localizado al principio del paquete o al final del paquete. En este ejemplo, el segundo dispositivo de control 515 puede detectar un paquete de salida detectando el indicador de paquete respectivo. El segundo dispositivo de control 515 puede incrementar el valor de recuento del segundo contador 525 cada vez que el segundo dispositivo de control 515 detecta un paquete de salida. Por tanto, en este ejemplo, el segundo contador 525 hace un seguimiento de un número de paquetes de salida.

- [0036] El dispositivo de comparación 540 compara el valor de recuento del primer contador 520 con el valor de recuento del segundo contador 525. Si los valores de recuento coinciden, el dispositivo de comparación 540 determina que la canalización 410 está vacía. Si los valores de recuento no coinciden, el dispositivo de comparación 540 determina que la canalización 410 no está vacía. El dispositivo de comparación 540 genera a continuación una marca de vacío en base a la comparación, en el que la marca de vacío indica si la canalización 410 está vacía. Por ejemplo, la marca de vacío puede tener un primer valor lógico (por ejemplo, uno) cuando se determina que la canalización 410 está vacía, y un segundo valor lógico (por ejemplo, cero) cuando se determina que la canalización 410 no está vacía.

- 65 **[0037]** El dispositivo de control de reloj 550 está configurado para recibir la marca de vacío desde el dispositivo de comparación 540. Si la marca de vacío indica que la canalización no está vacía, el dispositivo de control de reloj

550 puede dejar la señal de reloj clk habilitada (sin bloquear). En este caso, el dispositivo de compuertas de reloj 425 deja pasar la señal de reloj clk hacia la canalización 410. Si la marca de vacío indica que la canalización está vacía, el dispositivo de control de reloj 550 puede ordenar al dispositivo de compuertas de reloj 425 que bloquee (inhabilite) el paso de la señal de reloj clk hacia la canalización 410. En un ejemplo, si la marca de vacío indica que la canalización está vacía, el dispositivo de control de reloj 550 también puede verificar si hay un paquete de entrada de datos válidos en la entrada de la canalización 410. Si el dispositivo de control de reloj 550 no detecta un paquete de entrada de datos válidos, el dispositivo de control de reloj 550 puede ordenar al dispositivo de compuertas de reloj 425 que bloquee (inhabilite) el paso de la señal de reloj clk hacia la canalización 410. En este ejemplo, el dispositivo de control de reloj 550 puede detectar un paquete de entrada detectando el indicador de paquete respectivo (por ejemplo, delimitador). Cuando el dispositivo de compuertas de reloj 425 bloquea (inhabilita) la señal de reloj clk, el dispositivo de compuertas de reloj 425 facilita un estado lógico constante (cero o uno) a la canalización 410 independiente del estado lógico de la señal de reloj clk.

10

15

35

40

45

50

55

[0038] Después de que se haya bloqueado (inhabilitado) el paso de la señal de reloj clk hacia la canalización 410, el dispositivo de control de reloj 550 puede establecer si en la entrada de la canalización 410 hay un paquete de entrada de datos válidos. Si el dispositivo de control de reloj 550 detecta un paquete de entrada, el dispositivo de control de reloj 550 habilita (deja pasar) la señal de reloj clk. Si el dispositivo de control de reloj 550 no detecta un paquete de entrada, el dispositivo de control de reloj 550 deja la señal de reloj clk inhabilitada (bloqueada).

20 [0039] En un ejemplo, el dispositivo de control de reloj 550 puede estar configurado para facilitar un primer valor lógico (por ejemplo, uno) al dispositivo de compuertas de reloj 425 para habilitar la señal de reloj clk y facilitar un segundo valor lógico (por ejemplo, cero) al dispositivo de compuertas de reloj 425 para bloquear (inhabilitar) la señal de reloj clk. En este ejemplo, el dispositivo de control de reloj 550 facilita el primer valor lógico cuando la marca de vacío indica que la canalización no está vacía. El dispositivo de control de reloj 500 puede facilitar el segundo valor lógico cuando la marca de vacío indica que la canalización está vacía. En un ejemplo, el dispositivo de control de reloj 550 puede facilitar el segundo valor lógico cuando la marca de vacío indica que la canalización 410 está vacía y no se detecta ningún paquete de entrada en la entrada de la canalización. Después de que se haya bloqueado la señal de reloj clk, el dispositivo de control de reloj 550 puede establecer si en la entrada de la canalización hay un paquete de entrada, y cambiar su salida del segundo valor lógico al primer valor lógico tras la detección de un paquete de entrada para volver a habilitar la señal de reloj clk.

[0040] El controlador de reloj 420 también puede recibir la señal de reloj clk para temporizar unas operaciones del controlador de reloj 420. A este respecto, la FIG. 6 muestra un ejemplo en el que el primer dispositivo de control 510, el primer contador 520, el segundo dispositivo de control 515, el segundo contador 525 y el dispositivo de comparación 540 reciben la señal de reloj clk desde la salida del dispositivo de compuertas de reloj 425. Por tanto, en este ejemplo, cuando se inhabilita (bloquea) el paso de la señal de reloj clk hacia la canalización 410, la señal de reloj clk para el primer dispositivo de control 510, el primer contador 520, el segundo dispositivo de control 515, el segundo contador 525 y el dispositivo de comparación 540 también se bloquean para ahorrar energía. El primer y el segundo contadores 520 y 525 pueden mantener sus valores de recuento actuales cuando la señal de reloj clk está bloqueada. En este ejemplo, cada uno del primer y el segundo contadores 520 y 525 puede reanudar el recuento desde el valor de recuento retenido cuando la señal de reloj clk se vuelve a habilitar. De forma alternativa, los contadores 520 y 525 se pueden reiniciar cuando la señal de reloj clk se bloquea. En este ejemplo, cada uno del primer y el segundo contador 520 y 525 puede comenzar a contar desde un valor de recuento de reinicio (por ejemplo, cero) cuando la señal de reloj clk se vuelve a habilitar.

[0041] La señal de reloj clk para el dispositivo de control de reloj 550 puede pasar por alto el dispositivo de compuertas de reloj 425 de modo que la señal de reloj clk para el dispositivo de control de reloj 550 no se bloquea cuando la señal de reloj clk para la canalización 410 se bloquea. En este ejemplo, la señal de reloj clk se puede usar para temporizar operaciones del dispositivo de control de reloj 550 usadas para detectar un paquete de entrada en la entrada de la canalización 410 y, al detectar un paquete de entrada, habilitar (dejar pasar) la señal de reloj clk para la canalización 410. En otro ejemplo, el dispositivo de control de reloj 550 puede incluir una o más compuertas lógicas que no necesitan la señal de reloj clk para habilitar la señal de reloj clk cuando un paquete de entrada está presente en la entrada de la canalización 410. En este caso, no es necesario proporcionar la señal de reloj clk al dispositivo de compuertas de reloj 425.

**[0042]** Se pueden implementar diversos componentes del controlador de reloj 420 usando componentes de un controlador síncrono de primero en entrar, primero en salir (FIFO), como se analiza en mayor detalle a continuación.

[0043] Un controlador síncrono FIFO controla la escritura de datos en y la lectura de datos desde una memoria FIFO. A este respecto, un controlador FIFO puede incluir un contador de escritura, un contador de lectura y un dispositivo de comparación. El valor de recuento del contador de escritura se incrementa cuando se introducen datos en la memoria FIFO, y se usa para generar un puntero de escritura que especifica la ubicación (dirección) en la memoria FIFO en la que se van a escribir los datos. El valor de recuento del contador de lectura se incrementa cuando se leen datos desde la memoria FIFO, y se usa para generar un puntero de lectura que especifica la ubicación (dirección) en la memoria FIFO desde la que se van a leer los datos. El dispositivo de comparación

compara el puntero de escritura con el puntero de lectura para determinar si la memoria FIFO está vacía y facilita una marca de vacío en base a la comparación que indica si la memoria FIFO está vacía. Por ejemplo, el dispositivo de comparación puede determinar que la memoria FIFO está vacía cuando el puntero de escritura y el puntero de lectura coinciden.

5

10

**[0044]** En un ejemplo, el primer contador 520, el segundo contador 525 y el dispositivo de comparación 540 del controlador de reloj 420 se pueden implementar usando un contador de escritura, un contador de lectura y un dispositivo de comparación de un controlador FIFO. En este ejemplo, la canalización 410 se trata como una memoria FIFO con el propósito de determinar si la canalización 410 está vacía. Esto permite que el controlador de reloj 420 reúse componentes (por ejemplo, un contador de escritura, un contador de lectura y un dispositivo de comparación) de un controlador FIFO usado para generar la marca de vacío para el controlador FIFO para generar la marca de vacío para el controlador de reloj 420.

15

[0045] Cabe destacar que, aunque la canalización 410 se trata como una memoria FIFO con el propósito de determinar si la canalización 410 está vacía en el ejemplo anterior, la canalización difiere de una memoria FIFO en otros aspectos. Por ejemplo, la canalización 410 procesa datos mientras que una memoria FIFO simplemente almacena (por ejemplo, almacena en memoria intermedia) datos.

20

[0046] La FIG. 7 es una tabla 700 que muestra ejemplos de áreas de chip para los tres procedimientos de compuertas de reloj diferentes analizados para diferentes profundidades de canalización (es decir, diferentes números de fases de canalización). Las cuatro primeras filas de la tabla 700 muestran ejemplos de áreas de chip para el enfoque FSM (mostrado en la FIG.2A) para profundidades de canalización de 2, 50, 100 y 500. Las cuatro siguientes filas de la tabla 700 muestran ejemplos de áreas de chip para el enfoque de compuerta OR (mostrado en la FIG. 3) para profundidades de canalización de 2, 50, 100 y 500. Las cuatro últimas filas de la tabla 700 muestran ejemplos de áreas de chip para el enfoque FIFO (mostrado en las FIGS. 4-6) para profundidades de canalización de 2, 50, 100 y 500.

25

30

[0047] Como se muestra en la FIG. 7, el área de chip para el enfoque FSM no se incrementa a medida que la profundidad de canalización asciende. Por el contrario, el área del chip para el enfoque de compuerta OR se incrementa de forma aproximadamente lineal con los incrementos en la profundidad de canalización. Esto se debe a que se añade una entrada adicional a la compuerta OR para cada fase de canalización adicional. El enfoque de compuerta OR no es muy escalable porque los incrementos en la profundidad de canalización pueden dar como resultado incrementos significativos en el área del chip ocupada por la compuerta OR. El incremento significativo en el área de chip no solo ocupa un valioso espacio en el chip, sino que también se traduce en un incremento significativo en el consumo de energía.

35

**[0048]** El área de chip para el enfoque FIFO se incrementa ligeramente con los incrementos en la profundidad de canalización. El incremento en el área de chip se debe a los bits adicionales necesarios para hacer un seguimiento de un número mayor de paquetes de entrada y de salida a medida que la profundidad de canalización se incrementa. Los bits adicionales se escalan con log2 (es decir, logaritmo de base 2) de la profundidad de canalización. Como se muestra en la tabla 700, el incremento en el área de chip para el enfoque FIFO es significativamente menor que el enfoque de compuerta OR. Por tanto, a medida que se incrementa la profundidad de canalización, el enfoque FIFO requiere un área y una potencia significativamente menores que los del enfoque de compuerta OR.

45

40

[0049] El enfoque FIFO ocupa más área de chip que el enfoque FSM en el ejemplo mostrado en la FIG. 7. Sin embargo, el enfoque FIFO puede bloquear la señal de reloj clk durante las burbujas de las líneas activas, mientras que el enfoque FSM no bloquea la señal de reloj clk durante las burbujas, como se analiza anteriormente. Por tanto, el enfoque FIFO puede bloquear la señal de reloj con más frecuencia (es decir, aprovechar más oportunidades para bloquear la señal de reloj), lo que da como resultado más ahorro de energía gracias al bloqueo de reloj.

50

[0050] El dispositivo de compuertas de reloj 425 se puede implementar usando una cualquiera de un número de celdas de compuertas de reloj (CGC) conocidas en la técnica. Por ejemplo, la biblioteca de celdas estándar para un chip (pastilla) típicamente incluye una o más CGC. En este ejemplo, se puede seleccionar una de las CGC de la biblioteca de celdas para implementar el dispositivo de compuertas de reloj 425.

55

60

65

[0051] A este respecto, la FIG. 8 muestra una celda de compuertas de reloj (CGC) 810 ejemplar que se puede usar para implementar el dispositivo de compuertas de reloj 425. En este ejemplo, la CGC 810 incluye un cerrojo activado por flanco negativo 820 y una compuerta AND 830. La CGC 810 tiene una entrada de control de compuertas 812 que recibe una señal de control de compuertas desde el dispositivo de control de reloj 550, una entrada de reloj 814 que recibe la señal de reloj clk y una salida 816 acoplada a la entrada de reloj de la canalización 410. El cerrojo 820 tiene una entrada de control 822 que recibe la señal de control de compuertas, una entrada de reloj 824 que recibe la señal de reloj clk y una salida 826. La compuerta AND 830 tiene una primera entrada 832 acoplada a la salida 826 del cerrojo 820, una segunda entrada 834 que recibe la señal de reloj clk, y una salida 836 acoplada a la salida 816 de la CGC 810.

[0052] En este ejemplo, la CGC 810 bloquea la señal de reloj clk cuando la señal de control de compuertas del dispositivo de control de reloj 550 es baja (cero lógico). En este caso, la CGC 810 facilita un cero lógico a la canalización 410 independientemente del estado lógico de la señal de reloj clk. La CGC 810 pasa la señal de reloj clk a la canalización 410 cuando la señal de control de compuertas es alta (uno lógico). La señal de control de compuertas también se puede denominar señal de habilitación de reloj, ya que controla si la señal de reloj clk para la canalización está habilitada.

[0053] En funcionamiento, el cerrojo 820 enclava el valor lógico de la señal de control de compuertas en un flanco descendente de la señal de reloj clk, y facilita el valor lógico enclavado de la señal de control de compuertas a la primera entrada 832 de la compuerta AND 830. Si el valor lógico enclavado de la señal de control de compuertas es de uno lógico, la compuerta AND 830 pasa la señal de reloj clk a la salida 816 de la CGC 810. Si el valor lógico enclavado de la señal de control de compuertas es de cero lógico, la compuerta AND 830 facilita un cero lógico independientemente del estado lógico de la señal de reloj clk, bloqueando eficazmente la señal de reloj clk. En este ejemplo, el cerrojo 820 se usa para evitar problemas en la salida 816 de la CGC 810. Se debe apreciar que la CGC 810 mostrada en la FIG. 8 es solo ejemplar, y que el dispositivo de compuertas de reloj 425 se puede implementar usando otras CGC conocidas en la técnica.

10

15

20

25

30

35

40

45

50

55

60

65

[0054] La FIG. 9 ilustra un procedimiento 900 para compuertas de reloj de acuerdo con determinados aspectos de la presente divulgación. El controlador de reloj 420 y el dispositivo de compuertas de reloj 425 pueden realizar el procedimiento 900.

[0055] En la etapa 910, se hace un seguimiento de un número de paquetes de entrada en una entrada de una canalización. Por ejemplo, se puede hacer un seguimiento del número de paquetes de entrada incrementando un valor de recuento de un primer contador (por ejemplo, el primer contador 520) para cada paquete de entrada.

**[0056]** En la etapa 920, se hace un seguimiento de un número de paquetes de salida en una salida de la canalización. Por ejemplo, se puede hacer un seguimiento del número de paquetes de entrada incrementando un valor de recuento de un segundo contador (por ejemplo, el segundo contador 525) para cada paquete de salida.

**[0057]** En la etapa 930, se determina si se ha de bloquear o dejar pasar una señal de reloj hacia la canalización en base al número de los paquetes de entrada y al número de los paquetes de salida. Por ejemplo, se puede determinar bloquear la señal de reloj si el número de los paquetes de entrada y el número de los paquetes de salida coinciden, y se puede determinar dejar pasar la señal de reloj hacia la canalización si el número de los paquetes de entrada y el número de los paquetes de salida no coinciden.

[0058] En la etapa 940, la señal de reloj se pasa a la canalización si se determina dejar pasar la señal de reloj.

[0059] En la etapa 950, la señal de reloj se bloquea si se determina bloquear la señal de reloj.

[0060] El controlador de reloj 420 analizado anteriormente se puede implementar con un procesador de propósito general, un procesador de señales digitales (DSP), un circuito integrado específico de la aplicación (ASIC), una matriz de compuertas programables in situ (FPGA) u otro dispositivo de lógica programable, componentes de hardware discretos (por ejemplo, compuertas lógicas) o cualquier combinación de los mismos diseñada para realizar las funciones descritas en el presente documento. Un procesador puede realizar las funciones descritas en el presente documento ejecutando software que comprende código para realizar las funciones. El software puede estar almacenado en un medio de almacenamiento legible por ordenador, tal como una RAM, una ROM, una EEPROM, un disco óptico y/o un disco magnético.

[0061] Dentro de la presente divulgación, la palabra "ejemplar" se usa para significar "que sirve de ejemplo, caso o ilustración". No se debe interpretar necesariamente que cualquier implementación o aspecto descrito en el presente documento como "ejemplar" es preferente o ventajoso con respecto a otros aspectos de la divulgación. Asimismo, el término "aspectos" no requiere que todos los aspectos de la divulgación incluyan la característica, la ventaja o el modo de funcionamiento analizados.

**[0062]** Aunque la presente divulgación se analiza anteriormente usando el ejemplo de una canalización de procesamiento de imágenes, se debe apreciar que la presente divulgación no se limita a este ejemplo. Los modos de realización de la presente divulgación se pueden aplicar a otros tipos de canalizaciones que procesan datos para bloquear o dejar pasar la señal de reloj hacia los otros tipos de canalizaciones.

[0063] La descripción previa de la divulgación se proporciona para permitir que cualquier experto en la técnica realice o use la divulgación. Diversas modificaciones de la divulgación resultarán fácilmente evidentes a los expertos en la técnica, y los principios genéricos definidos en el presente documento se pueden aplicar a otras variantes sin apartarse del alcance de la divulgación. Por tanto, no se pretende limitar la invención a los ejemplos descritos en el presente documento, sino que se le ha de conceder el alcance más amplio consecuente con las reivindicaciones adjuntas.

#### REIVINDICACIONES

1. Un sistema de compuertas de reloj para una canalización (410), que comprende:

un dispositivo de compuertas de reloj (425) configurado para dejar pasar o bloquear una señal de reloj (clk) hacia la canalización; y

un controlador de reloj (420) configurado para hacer un seguimiento de un número de paquetes de entrada en una entrada de la canalización, hacer un seguimiento de un número de paquetes de salida en una salida de la canalización, determinar si se ha de dejar pasar o bloquear la señal de reloj en base al número de los paquetes de entrada y el número de los paquetes de salida, ordenar al dispositivo de compuertas de reloj que deje pasar la señal de reloj si se determina dejar pasar la señal de reloj, y ordenar al dispositivo de compuertas de reloj que bloquee la señal de reloj si se determina bloquear la señal de reloj;

en el que el controlador de reloj está configurado para ordenar al dispositivo de compuertas de reloj que bloquee la señal de reloj si el número de los paquetes de entrada coincide con el número de paquetes de salida, y ordenar al dispositivo de compuertas de reloj que deje pasar la señal de reloj si el número de los paquetes de entrada no coincide con el número de paquetes de salida.

2. El sistema de compuertas de reloj de la reivindicación 1, en el que el controlador de reloj comprende:

un primer contador (520);

un primer dispositivo de control (510) configurado para detectar los paquetes de entrada en la entrada de la canalización, e incrementar un valor de recuento del primer contador para cada uno de los paquetes de entrada detectados, en el que el valor de recuento del primer contador indica el número de los paquetes de entrada:

30 un segundo contador (525); y

5

10

15

20

35

40

45

55

un segundo dispositivo de control (515) configurado para detectar los paquetes de salida en la salida de la canalización, e incrementar un valor de recuento del segundo contador para cada uno de los paquetes de salida detectados, en el que el valor de recuento del segundo contador indica el número de los paquetes de salida.

3. El sistema de compuertas de reloj de la reivindicación 2, en el que el controlador de reloj comprende además:

un dispositivo de comparación configurado para comparar el valor de recuento del primer contador con el valor de recuento del segundo contador, y generar una marca en base a la comparación, en el que la marca indica si la canalización está vacía; y

un dispositivo de control de reloj configurado para ordenar al dispositivo de compuertas de reloj que deje pasar la señal de reloj si la marca no indica que la canalización está vacía, y para ordenar al dispositivo de compuertas de reloj que bloquee la señal de reloj si la marca indica que la canalización está vacía.

- **4.** El sistema de compuertas de reloj de la reivindicación 3, en el que la marca indica que la canalización está vacía si el valor de recuento del primer contador y el valor de recuento del segundo contador coinciden.

- 50 5. El sistema de compuertas de reloj de la reivindicación 4, en el que la marca no indica que la canalización está vacía si el valor de recuento del primer contador y el valor de recuento del segundo contador no coinciden.

- 6. El sistema de compuertas de reloj de la reivindicación 2, en el que el primer dispositivo de control está configurado para detectar cada uno de los paquetes de entrada detectando un delimitador del paquete de entrada.

- 7. El sistema de compuertas de reloj de la reivindicación 6, en el que el segundo dispositivo de control está configurado para detectar cada uno de los paquetes de salida detectando un delimitador del paquete de salida.

- **8.** El sistema de compuertas de reloj de la reivindicación 1, en el que, después de ordenar al dispositivo de compuertas de reloj que bloquee la señal de reloj, el controlador de reloj está configurado además para establecer si en la entrada de la canalización hay un siguiente paquete de entrada, y, al detectar el siguiente paquete de entrada, ordenar al dispositivo de compuertas de reloj que deje pasar la señal de reloj.

- **9.** Procedimiento (900) para compuertas de reloj, que comprende:

|            | hacer un seguimiento (910) de un número de paquetes de entrada en una entrada de una canalización (410);                                                                                                                                                                                                                                                                                            |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5          | hacer un seguimiento (920) de un número de paquetes de salida en una salida de la canalización;                                                                                                                                                                                                                                                                                                     |

| 5          | determinar (930) si se ha de bloquear o dejar pasar una señal de reloj (clk) hacia la canalización en base al número de los paquetes de entrada y el número de los paquetes de salida;                                                                                                                                                                                                              |

| 10         | dejar pasar (940) la señal de reloj hacia la canalización si se determina dejar pasar la señal de reloj; y                                                                                                                                                                                                                                                                                          |

| 10         | bloquear (950) la señal de reloj si se determina bloquear la señal de reloj; y                                                                                                                                                                                                                                                                                                                      |

|            | en el que determinar si se ha de bloquear o dejar pasar la señal de reloj comprende:                                                                                                                                                                                                                                                                                                                |

| 15         | determinar que se ha de bloquear la señal de reloj si el número de los paquetes de entrada coincide con el número de los paquetes de salida; y                                                                                                                                                                                                                                                      |

| 20         | determinar que se ha de dejar pasar la señal de reloj si el número de los paquetes de entrada no coincide con el número de los paquetes de salida.                                                                                                                                                                                                                                                  |

|            | 10. El procedimiento de la reivindicación 9, en el que hacer un seguimiento del número de los paquetes de entrada comprende incrementar un valor de recuento de un primer contador para cada uno de los paquetes de entrada, y hacer un seguimiento del número de los paquetes de salida comprende incrementar un valor de recuento de un segundo contador para cada uno de los paquetes de salida. |

| 25         | 11. El procedimiento de la reivindicación 10, en el que incrementar el valor de recuento del primer contador incluye:                                                                                                                                                                                                                                                                               |

| 00         | detectar cada uno de los paquetes de entrada en la entrada de la canalización detectando un delimitador del paquete de entrada; e                                                                                                                                                                                                                                                                   |

| 30         | incrementar el valor de recuento del primer contador para cada uno de los paquetes de entrada detectados.                                                                                                                                                                                                                                                                                           |

| 35         | 12. El procedimiento de la reivindicación 10, en el que incrementar el valor de recuento del segundo contador incluye:                                                                                                                                                                                                                                                                              |

| <b>3</b> 3 | detectar cada uno de los paquetes de salida en la salida de la canalización detectando un delimitador del paquete de salida; e                                                                                                                                                                                                                                                                      |

| 40         | incrementar el valor de recuento del segundo contador para cada uno de los paquetes de salida detectados.                                                                                                                                                                                                                                                                                           |

|            | 13. El procedimiento de la reivindicación 10, en el que determinar si se ha de bloquear o dejar pasar la señal de reloj comprende:                                                                                                                                                                                                                                                                  |

| 45         | comparar el valor de recuento del primer contador con el valor de recuento del segundo contador; y                                                                                                                                                                                                                                                                                                  |

|            | determinar si se ha de bloquear o dejar pasar la señal de reloj en base a la comparación; y                                                                                                                                                                                                                                                                                                         |

| 50         | en el que determinar si se ha de bloquear o dejar pasar la señal de reloj comprende determinar que se ha<br>de bloquear la señal de reloj si el valor de recuento del primer contador y el valor de recuento del segundo<br>contador coinciden,                                                                                                                                                     |

| E E        | en el que determinar si se ha de bloquear o dejar pasar la señal de reloj comprende determinar que se ha de dejar pasar la señal de reloj si el valor de recuento del primer contador y el valor de recuento del segundo contador no coinciden.                                                                                                                                                     |

| 55         | 14. El procedimiento de la reivindicación 9, que comprende además:                                                                                                                                                                                                                                                                                                                                  |

| 60         | después de bloquear la señal de reloj, establecer si en la entrada de la canalización hay un siguiente paquete de entrada; y                                                                                                                                                                                                                                                                        |

| ou         | dejar pasar la señal de reloj al detectar el siguiente paquete de entrada.                                                                                                                                                                                                                                                                                                                          |

|            | <b>15.</b> El sistema de compuertas de reloj de la reivindicación 1, o el procedimiento de la reivindicación 9, en el que la canalización es una canalización de procesamiento de imágenes.                                                                                                                                                                                                         |

13

FIG. 2B

FIG. 3

FIG. 4

FIG. 5

E

√ 700

| Procedimiento | Profundidad<br>de canalización | Área (µm²) |

|---------------|--------------------------------|------------|

| FSM           | 2                              | 4,4        |

| FSM           | 50                             | 4,4        |

| FSM           | 100                            | 4,4        |

| FSM           | 200                            | 4,4        |

| OR            | 2                              | 11,7       |

| OR            | 50                             | 25,5       |

| OR            | 100                            | 41,2       |

| OR            | 200                            | 158,5      |

| FIFO          | 2                              | 22,9       |

| FIFO          | 50                             | 24,4       |

| FIFO          | 100                            | 28,8       |

| FIFO          | 500                            | 32,8       |

|               |                                |            |

FIG. 7

FIG. 9